1.1 PCB板上预划分数字、模拟、DAA信号布线区域。

1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。

1.3 高速数字信号走线尽量短。

1.4 敏感模拟信号走线尽量短。

1.5 合理分配电源和地。

1.6 DGND、AGND、实地分开。

1.7 电源及临界信号走线使用宽线。

1.8 数字电路放置於并行总线/串行DTE接口附近,DAA电路放置於电话线接口附近。

2. 元器件放置

2.1 在系统电路原理图中:

a) 划分数字、模拟、DAA电路及其相关电路;

b) 在各个电路中划分数字、模拟、混合数字/模拟元器件;

c) 注意各IC芯片电源和信号引脚的定位。

2.2 初步划分数字、模拟、DAA电路在PCB板上的布线区域(一般比例2/1/1),数字、模拟元器件及其相应走线尽量远离并限定在各自的布线区域内。

Note:当DAA电路占较大比重时,会有较多控制/状态信号走线穿越其布线区域,可根据当地规则限定做调整,如元器件间距、高压抑制、电流限制等。

2.3 初步划分完毕後,从Connector和Jack开始放置元器件:

a) Connector和Jack周围留出插件的位置;

b) 元器件周围留出电源和地走线的空间;

c) Socket周围留出相应插件的位置。

2.4 首先放置混合型元器件(如Modem器件、A/D、D/A转换芯片等):

a) 确定元器件放置方向,尽量使数字信号及模拟信号引脚朝向各自布线区域;

b) 将元器件放置在数字和模拟信号布线区域的交界处。

2.5 放置所有的模拟器件:

a) 放置模拟电路元器件,包括DAA电路;

b) 模拟器件相互靠近且放置在PCB上包含TXA1、TXA2、RIN、VC、VREF信号走线的一面;

c) TXA1、TXA2、RIN、VC、VREF信号走线周围避免放置高噪声元器件;

d) 对於串行DTE模块,DTE EIA/TIA-232-E

系列接口信号的接收/驱动器尽量靠近Connector并远离高频时钟信号走线,以减少/避免每条线上增加的噪声抑制器件,如阻流圈和电容等。

2.6 放置数字元器件及去耦电容:

a) 数字元器件集中放置以减少走线长度;

b) 在IC的电源/地间放置0.1uF的去耦电容,连接走线尽量短约跣?MI;

c) 对并行总线模块,元器件紧靠

Connector边缘放置,以符合应用总线接口标准,如ISA总线走线长度限定在2.5in;

d) 对串行DTE模块,接口电路靠近Connector;

e) 晶振电路尽量靠近其驱动器件。

2.7 各区域的地线,通常用0 Ohm电阻或bead在一点或多点相连。

3. 信号走线

3.1 Modem信号走线中,易产生噪声的信号线和易受干扰的信号线尽量远离,如无法避免时要用中性信号线隔离。

Modem易产生噪声的信号引脚、中性信号引脚、易受干扰的信号引脚如下表所示:

===============================================================

| Noise Source | neutral | noise

sensitive

-----------+----------------+----------------+-----------------

VDD,GND, AGND | | 31,38,34,37 |

-----------+----------------+----------------+-----------------

Crystal | 52,53 | |

-----------+----------------+----------------+-----------------

Reset | | 35 |

-----------+----------------+----------------+-----------------

Memory BUS| 1-6,9-10,12-13 | |

| 43-50,58-68 | |

-----------+----------------+----------------+-----------------

NVRAM | | 39,42 |

-----------+----------------+----------------+-----------------

Telephone | | 7-8,36,51,54 | 24-25,30,32-33

-----------+----------------+----------------+-----------------

Audio | | | 23,26-29

-----------+----------------+----------------+-----------------

串行DTE | 40-41 | 11,14-22,55-57 |

===============================================================

===============================================================

| Noise Source | neutral | noise

sensitive

-----------+----------------+----------------+-----------------

VDD,GND, AGND | | 31,38,34,37 |

-----------+----------------+----------------+-----------------

Crystal | 52,53 | |

-----------+----------------+----------------+-----------------

Reset | | 35 |

-----------+----------------+----------------+-----------------

Memory BUS| 1-6,9-10,12-13 | |

| 43-50,58-68 | |

-----------+----------------+----------------+-----------------

NVRAM | | 39,42 |

-----------+----------------+----------------+-----------------

Telephone | | 7-8,36,51,54 | 24-25,30,32-33

-----------+----------------+----------------+-----------------

Audio | | | 23,26-29

-----------+----------------+----------------+-----------------

并行总线 | 11,14-22,40-41 | |

| 55-57 | |

===============================================================

3.2 数字信号走线尽量放置在数字信号布线区域内;

模拟信号走线尽量放置在模拟信号布线区域内;

(可预先放置隔离走线加以限定,以防走线布出布线区域)

数字信号走线和模拟信号走线垂直以减小交叉耦合。

3.3 使用隔离走线(通常为地)将模拟信号走线限定在模拟信号布线区域。

a) 模拟区隔离地走线环绕模拟信号布线区域布在PCB板两面,线宽50-100mil;

b) 数字区隔离地走线环绕数字信号布线区域布在PCB板两面,线宽50-100mil,其中一面PCB板边应布200mil宽度。

3.4 并行总线接口信号走线线宽>10mil(一般为12-15mil),如/HCS、/HRD、/HWT、/RESET。

3.5 模拟信号走线线宽>10mil(一般为12-15mil),如MICM、MICV、SPKV、VC、VREF、TXA1、TXA2、RXA、TELIN、TELOUT。

3.6 所有其它信号走线尽量宽,线宽>5mil(一般为 10mil),元器件间走线尽量短(放置器件时应预先考虑)。

3.7 旁路电容到相应IC的走线线宽>25mil,并尽量避免使用过孔。

3.8 通过不同区域的信号线(如典型的低速控制/状态信号)应在一点(首选)或两点通过隔离地线。如果走线只位於一面, 隔离地线可走到PCB的另一面以跳过信号走线而保持连续。

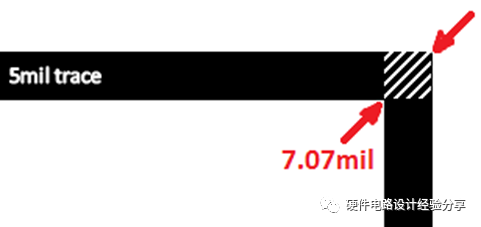

3.9 高频信号走线避免使用90度角弯转,应使用平滑圆弧或45度角。

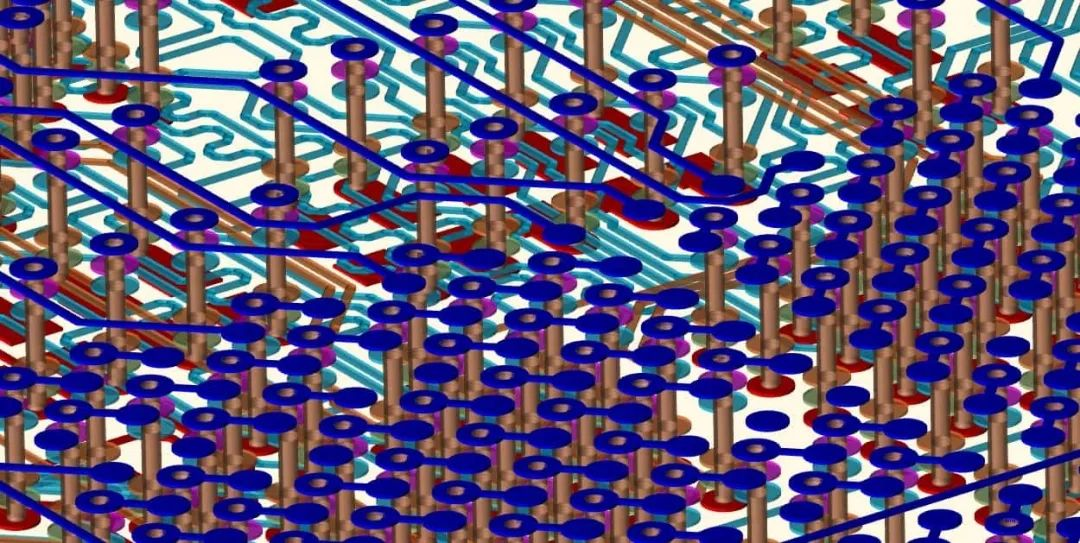

3.10 高频信号走线应减少使用过孔连接。

3.11 所有信号走线远离晶振电路。

3.12 对高频信号走线应采用单一连续走线,避免出现从一点延伸出几段走线的情况。

3.13 DAA电路中,穿孔周围(所有层面)留出至少60mil的空间。

3.14 清除地线环路,以防意外电流回馈影响电源。

4. 电源

4.1 确定电源连接关系。

4.2 数字信号布线区域中,用10uF电解电容或钽电容与0.1uF瓷片电容并联後接在电源/地之间.在PCB板电源入口端和最远端各放置一处,以防电源尖峰脉冲引发的噪声干扰。

4.3 对双面板,在用电电路相同层面中,用两边线宽为 200mil的电源走线环绕该电路。(另一面须用数字地做相同处理)

4.4 一般地,先布电源走线,再布信号走线。

5. 地

5.1双面板中,数字和模拟元器件(除DAA)周围及下方未使用之区域用数字地或模拟地区域填充,各层面同类地区域连接在一起,不同层面同类地区域通过多个过孔相连:Modem DGND引脚接至数字地区域,AGND引脚接至模拟地区域;数字地区域和模拟地区域用一条直的空隙隔开。

5.2 四层板中,使用数字和模拟地区域覆盖数字和模拟元器件(除DAA);Modem DGND引脚接至数字地区域,AGND引脚接至模拟地区域;数字地区域和模拟地区域用一条直的空隙隔开。

5.3 如设计中须EMI过滤器,应在接口插座端预留一定空间,绝大多数EMI器件(Bead/电容)均可放置在该区域;未使用之区域用地区域填充,如有屏蔽外壳也须与之相连。

5.4 每个功能模块电源应分开。功能模块可分为:并行总线接口、显示、数字电路(SRAM、EPROM、Modem)和DAA等,每个功能模块的电源/地只能在电源/地的源点相连。

5.5 对串行DTE模块,使用去耦电容减少电源耦合,对电话线也可做相同处理。

5.6 地线通过一点相连,如可能,使用Bead;如抑制EMI需要,允许地线在其它地方相连。

5.7 所有地线走线尽量宽,25-50mil。

5.8 所有IC电源/地间的电容走线尽量短,并不要使用过孔。

6. 晶振电路

6.1 所有连到晶振输入/输出端(如XTLI、XTLO)的走线尽量短,以减少噪声干扰及分布电容对Crystal的影响。XTLO走线尽量短,且弯转角度不小於45度。(因XTLO连接至上升时间快,大电流之驱动器)

6.2 双面板中没有地线层,晶振电容地线应使用尽量宽的短线连接至器件上离晶振最近的DGND引脚,且尽量减少过孔。

6.3 如可能,晶振外壳接地。

6.4 在XTLO引脚与晶振/电容节点处接一个100 Ohm电阻。

6.5 晶振电容的地直接连接至 Modem的GND引脚,不要使用地线区域或地线走线来连接电容和Modem的GND引脚。

7. 使用EIA/TIA-232接口的独立Modem设计

7.1 使用金属外壳。 如果须用塑料外壳,应在内部贴金属箔片或喷导电物质以减小EMI。

7.2 各电源线上放置相同模式的Choke。

7.3 元器件放置在一起并紧靠EIA/TIA-232接口的Connector。

7.4 所有EIA/TIA-232器件从电源源点单独连接电源/地。电源/地的源点应为板上电源输入端或调压芯片的输出端。

7.5 EIA/TIA-232电缆信号地接至数字地。

7.6 以下情况EIA/TIA-232电缆屏蔽不用接至Modem外壳;空接;通过Bead接到数字地;EIA/TIA-232电缆靠近Modem外壳处放置一磁环时直接连到数字地。

8. VC及VREF电路电容走线尽量短,且位於中性区域。

8.1 10uF VC电解电容正极与0.1uF VC电容的连接端通过独立走线连至Modem的VC引脚(PIN24)。

8.2 10uF VC电解电容负极与0.1uF VC电容的连接端通过Bead後用独立走线连至Modem的AGND引脚(PIN34)。

8.3 10uF VREF电解电容正极与0.1uF VC电容的连接端通过独立走线连至Modem的VREF引脚(PIN25)。

8.4 10uF VREF电解电容负极与0.1uF VC电容的连接端通过独立走线连至Modem的VC引脚(PIN24);注意与8.1走线相独立。

VREF ------+--------+

┿ 10u ┿ 0.1u

VC ------+--------+

┿ 10u ┿ 0.1u

+--------+-----~~~~~---+ AGND

使用之Bead应满足:

100MHz时,阻抗=70W;;

额定电流=200mA;;

最大电阻=0.5W。

9. 电话和Handset接口

9.1 Tip和Ring线接口处放置Choke。

9.2 电话线的去耦方法与电源去耦类似,使用增加电感组合体、Choke、电容等方法。但电话线的去耦比电源去耦更困难也更值得注意, 一般做法是预留这些器件的位置,以便性能/EMI测试认证时调整。

9.3 Tip和Ring线到数字地间放置耐压高的滤波电容(0.001uF/1KV)。

- pcb(383717)

- ut指南(5317)

相关推荐

PCB Layout的第一次经历分享

PCB Layout的第一次经历分享

试着layout一回,使用的软件是PADS layout 2005 sp1。据同事说这个软件不算稳定,用时心里也有点虚,不过上手的时候用的就是这个版本,就没

2010-01-16 16:59:57 2485

2485

2485

2485PCB layout中的走线设计

PCB layout需要丰富的经验和扎实的理论基础支持,还要多踩几个坑,多做几个仿真加深对走线的理解,才能形成闭环的走线设计。

2022-07-19 15:10:41 3170

3170

3170

3170PCB Layout的设计要点

在集成电路应用设计中,项目原理图设计完成之后,就需要进行PCB布板的设计。 PCB设计是一个至关重要的环节。 设计结果的优劣直接影响整个设计功能。 因此,合理高效的PCB Layout是芯片电路设计调试成功中至关重要的一步。 本次我们就来简单讲一讲PCB Layout的设计要点。

2023-05-22 10:59:17 734

734

734

734

PCB Layout设计要点与技巧

在集成电路应用设计中,项目原理图设计完成之后,就需要进行PCB布板的设计。PCB设计是一个至关重要的环节。设计结果的优劣直接影响整个设计功能。因此,合理高效的PCB Layout是芯片电路设计调试成功中至关重要的一步。本次我们就来简单讲一讲PCB Layout的设计要点。

2023-05-31 10:52:56 936

936

936

936

pcb layout中IC常用封装介绍

本内容介绍了pcb layout中IC常用封装,了解这些常识对PCB LAYOUT是有帮助的。下面还将介绍几种IC封装。

2011-11-09 15:52:07 8229

8229

8229

8229PCB layout软件该如何学习和PCB设计需要注意的问题

的常见布线规则、注意事项掌握PCB的常见布线规则、注意事项。10常用快捷键介绍Pads原理图、Layout常用快捷键熟练掌握Pads原理图、Layout常用快捷键的使用11高级Layout指南介绍较复杂

2014-09-16 19:35:45

PCB layout 服务

本人从事PCB layout工作已多年,熟悉1-20层板的设计,应用PADS9.3,allegro16.3软件设计PCB板,能够导入各种软件的原理图,做过GPS,雷达模拟器等产品,有FPGA

2012-10-02 00:06:44

PCB及PCB LAYOUT设计

PCB及PCB LAYOUT设计工程师欢迎下载分享本人主要做LED驱动IC 产品QQ2892715427望认识各位工程师朋友互相学习技术探讨方案资料太大还没有分享完有需要的工程朋友 可以回帖[hide][/hide]

2015-11-19 15:24:21

layout与PCB有何关系

精辟!一文看懂layout与PCB的关系由于开关电源的开关特性, 容易使得开关电源产生极大的电磁兼容方面的干扰,作为一个电源工程师、电磁兼容工程师,或则一个 PCB layout 工程师必须了解

2021-08-06 08:46:28

BK3432Q/BK3432 开发应用指南& PCB LAYOUT指南,专业技术支持

我司是上海博通BK芯片一级代理,主要产品有蓝牙、2.4G芯片和蓝牙模组公司有强大的研发团队不仅可以为您提供最好的技术支持,还可以为您提供一站式物联网解决方案。详询:刘 ***qq506710311二.蓝牙模块1. BLE蓝牙芯片系列:BK3431Q:低功耗蓝牙4.2BLE,SOC芯片,Flash版本,ARM9内核,QFN48和QFN32封装,64KRAM, 500K Flash,RX5.2mA,TX5.0mA,休眠2uA适用于蓝牙电子秤、蓝牙防丢、蓝牙手环、智能穿戴设备、蓝牙智能家居APP控制等低功耗蓝牙产品BK3432:低功耗蓝牙4.2BLE+3.0双模,SOC芯片,Flash版本,ARM9内核,QFN32封装,20K RAM, 160K Flash,RX5.1mA,TX4.8mA,休眠1.8uA,资源相对BK3431Q做了精简,兼容性更好,性价比更好,适用于做标准透传类等简单的应用开发。BK3266: 低功耗蓝牙音频双模芯片耳机3266, qfn32 4*4 (主推)4Mflash (传统蓝牙BL、 tws/AI)、 8Mflash(数据大,多国语言,OTA,来电报号)AI耳机 :开放数据接口,对接云,(小米,百度,阿里(主要),亚马逊(下半年))40pin5*5:8M和16M16GPIO产品:入耳,单边,头戴,tws,线控,提供:参考设计,Tws,,弹窗、自动开机,双边通话,敲击唤醒UA287Q标准透传模块Ÿ功耗极低,休眠电流在2微安,TX发射电流为5mA,RX接受电流为5.2mA。Ÿ性价比高Ÿ资源丰富,内置500K Flash,有64kRAM可供客户二次开发Ÿ支持蓝牙4.2,可做主机模式或从机模式Ÿ支持微信AirSync广泛应于电子称、手环,键鼠,血压计,血糖仪、pos机等低功耗产品支持二次开发,满足客户订制化应用。三.BK上海博通2.4G芯片1. 2.4G无线射频系列:1)BK2425:单RF,有裸片和QFN20两种封装,适用于遥控器、无线键鼠、手柄、玩具和无线周边设备。2)BK2535:SOC芯片,Flash版本,51核+RF2.4G,有QFN32和QFN56两种封装,IO口多,功耗最低,可用于无线键鼠,鼠标,智能遥控器,无线数据传输,安防产品,数据采集系统等3)BK2451:SOC芯片,OTP版本,51核+RF2.4G,SOP20和QFN20封装,支持USB2.0,常用于USB接收端4)BK2461:SOC芯片,OTP版本,ARM9+RF2.4G,内置PA,最大可输出功率12dBm,5PWM,有SOP16、SOP20和QFN24三种封装,适用于远距离控制产品,如飞控,灯控,各类遥控器、空鼠和玩具等5)BK2452:SOC芯片,OTP版本,51核+RF2.4G,SOP16和QFN32封装6)BK2471:SOC芯片,Flash版本,ARM9+RF2.4G,有QFN32和QFN56封装,常用于无人机等飞控产品作为接收端四、wifi芯片系列(蓝牙+wifi二合一芯片)7)BK7231S 数传wifi芯片8)BK7231U 蓝牙+wifi双模,支持图传,无人机应用9)BK7251蓝牙+wifi音频 支持音频解码,可用于故事机,播报机等●其中以上多款芯片可以根据不同的产品进行搭配,实现利益最大化。

2019-05-13 09:59:54

PADS 高速PCB layout设计手机layout视频教程下载地址

PADS 高速PCB layout设计手机layout视频教程下载地址Cadence DDR3 PCBlayout视频教程:

2015-04-05 22:13:08

UltraScale架构用于闪存的PCB布局指南是什么

什么是闪存的布局指南,如长度要求?我在文档中看不到任何信息:UG583-UltraScale架构PCB设计和引脚规划用户指南_ 1.1谢谢以上来自于谷歌翻译以下为原文What's

2019-04-16 06:06:39

[分享]PCB Layout指南(上)

本帖最后由 eehome 于 2013-1-5 10:03 编辑

<p>PCB Layout指南(上)&nbsp;&nbsp

2009-05-31 11:03:19

[分享]PCB Layout指南(下)

本帖最后由 eehome 于 2013-1-5 09:53 编辑

<p>PCB Layout指南(下)&nbsp;&nbsp

2009-05-31 11:04:10

专业承接PCB Layout设计~

本人有6年PCB layout设计经验,长期从事数码产品的PCB layout及EMC设计整改工作!熟悉ORCAD和PADS设计软体精通PCB布局走线设计及设计过程的EMC考量!现愿承接PCB

2014-02-23 15:59:44

专业承接PCB layout设计~

本人有6年PCB layout设计经验,长期从事数码产品的PCB layout及EMC设计整改工作!熟悉ORCAD和PADS设计软体精通PCB布局走线设计及设计过程的EMC考量!现愿承接PCB

2014-02-23 16:02:10

承接pcb layout 兼职

本帖最后由 pcb兼职 于 2017-3-9 20:30 编辑

本人从事PCB Layout设计有5年的工作经验,能独立处理工作。期间Layout做过电脑主板,工控主板,医疗仪器。曾在

2017-03-04 21:25:12

承接pcb layout 兼职

`本人从事PCB Layout设计有5年的工作经验,能独立处理工作。期间Layout做过电脑主板,工控主板,医疗仪器。曾在外包公司派到华为现场办公,做过的产品有电源板,数模混合,路由器,融合网关

2017-06-13 22:39:40

承接电路、PCB设计,PCB Layout !

本人有多年的硬件及PCB layout设计经验,深厚的电子专业水平和硬件设计能力,熟悉产品开发流程,现想利用业余时间承接电路设计,PCB 设计,PCB layout。设计软件有pads

2015-05-16 19:16:35

接电路设计,PCB设计,PCB Layout

本人有多年的硬件及PCB layout设计经验,深厚的电子专业水平和硬件设计能力,熟悉产品开发流程,现想利用业余时间承接电路设计,PCB 设计,PCB layout。设计软件有pads

2015-05-16 19:18:22

pcb设计教程 (收藏多年的经典知识)

pcb设计教程内容有:高速PCB设计指南之一 高速PCB设计指南之二 PCB Layout指南(上) PCB Layout指南(下) PCB设计的一般原则 PCB设计基础知识 PCB设计基本概念 pcb设计注意

2009-01-18 13:08:07 0

0

0

0PCB LAYOUT基本规范

為確保產品之製造性, R&D在設計階段必須遵循Layout相關規範, 以利製造單位能順利生產, 確保產品良率, 降低因設計而重工之浪費. “PCB Layout Rule” Rev1.60 (發文字號: MT-8-2-0029)發

2009-10-17 10:59:02 235

235

235

235PCB设计基础教程手册

PCB设计基础教程

此教程包括:

高速PCB设计指南之一 高速PCB设计指南之二 PCB Layout指南(上) PCB Layout指南(下) PCB设计的一般原则 PCB设计基础知识 PCB设计

2010-03-15 14:22:26 0

0

0

0PCB Layout中的走线策略

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PC

2010-06-11 15:41:21 0

0

0

0XL-BST PCB LAYOUT智能工具

XL-BST PCB LAYOUT智能工具是一款架构于Xpedition,结合设计师实际应用场景,由解决多项实际应用操作组成的智能工具。通过XL-BST,在设计操作层面,设计师能快速

2024-03-18 17:55:31

PCB LAYOUT设计规范手册

PCB Layout Rule Rev1.70, 規範內容如附件所示, 其中分為:

(1) ”PCB LAYOUT 基本規範”:為R&D Layout時必須遵守的事項, 否則SMT,DIP,裁板時無法生產.

(2) “錫偷LAYOUT

2010-11-01 16:59:45 0

0

0

0PCB LAYOUT術語解釋

PCB LAYOUT術語解釋

PCB LAYOUT 術語解釋(TERMS)1. COMPONENT SIDE(零件面、正面)︰大多數零件放置之面。2. SOLDER SIDE(焊錫面、反面)。3. SOLDER M

2008-07-18 12:31:05 2320

2320

2320

2320pcb layout是什么

pcb layout是什么

PCB是印刷电路板(即Printed Circuit Board)的简称。印刷电路板是组装电子零件用的基板,是在通用基材上按预定设计形成点

2009-09-30 08:52:24 15959

15959

15959

15959pcb layout基础学习

本专题详细讲解了什么是pcb layout,pcb layout基础知识的学习及pcb layout工程师需要注意的事项,还有pcb layout设计的一些经验分享。

2011-11-21 14:04:34

PCB Layout指南

2012-03-08 03:20:38 0

0

0

0PCB layout电路设计七大法宝!

PCB Layout设计规则检查 能够应用和生产,继而成为一个正式的有效的产品才是PCB layout最终目的,layout的工作才算告一个段落。那么在layout的时候,应该注意哪些常规的要点

2018-03-23 14:56:00 2652

2652

2652

2652常用pcb layout软件有哪些

本文开始借介绍了pcb layout的概念和特性,其次介绍了pcb layout设计流程,最后介绍了几款pcb layout的常用软件与发展趋势。

2018-04-09 15:40:43 17025

17025

17025

17025

PCB layout工程师的7个好习惯

作为一名优秀的PCB layout工程师,好的工作习惯会使你的设计更合理,性能更好,生产更容易。本文罗列了PCB layout工程师的7个好习惯,来看看你都占了几个吧!

2022-02-16 15:46:31 2616

2616

2616

2616PCB LAYOUT的直角走线、差分走线、蛇形线资料下载

电子发烧友网为你提供PCB LAYOUT的直角走线、差分走线、蛇形线资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-31 08:41:16 17

17

17

17layout与PCB的29个基本关系资料下载

电子发烧友网为你提供layout与PCB的29个基本关系资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-31 08:44:58 7

7

7

7PCB 指南:快速理解高速layout设计资料下载

电子发烧友网为你提供PCB 指南:快速理解高速layout设计资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:49:21 25

25

25

25PCB Layout pcb布局的基本原则

PCB Layout即PCB布局,要使电子电路获得最佳性能,电子元器件的布局及导线的布线是非常关键的环节。要使PCB质量好,造价低,性能高,应将设计重点放在布局环节。以下是PCB布局的原则:

2021-07-21 16:44:24 14234

14234

14234

14234干货分享:PCB Layout的设计要点

在集成电路应用设计中,项目原理图设计完成之后,就需要进行PCB布板的设计。PCB设计是一个至关重要的环节。设计结果的优劣直接影响整个设计功能。因此,合理高效的PCB Layout是芯片电路...

2021-12-16 16:54:04 15

15

15

15干货分享:PCB Layout 的设计要点

在集成电路应用设计中,项目原理图设计完成之后,就需要进行PCB布板的设计。PCB设计是一个至关重要的环节。设计结果的优劣直接影响整个设计功能。因此,合理高效的PCB Layout是芯片电路...

2021-12-29 18:52:46 22

22

22

22PCB Layout中的走线策略

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中是至关重要的。

2022-08-12 14:38:39 1322

1322

1322

1322PCB Layout的设计要点及技巧

在集成电路应用设计中,项目原理图设计完成之后,就需要进行PCB布板的设计。PCB设计是一个至关重要的环节。设计结果的优劣直接影响整个设计功能。因此,合理高效的PCB Layout是芯片电路设计调试成功中至关重要的一步。本次我们就来简单讲一讲PCB Layout的设计要点

2023-04-27 15:16:40 910

910

910

910

PCB layout在布线上的设计规范有哪些?

一站式PCBA智造厂家今天为大家讲讲pcb layout设计需要注意哪些细节?pcb layout设计规范。Printed Circuit Board (PCB)是一种电子零件,它是连接

2024-02-23 09:19:41 142

142

142

142 电子发烧友App

电子发烧友App

评论