在亚微米以下的电路设计中,需要对电路进行全芯片的ESD保护结构的设计。如何使全芯片有效面积尽可能小、ESD性能可靠性满足要求且不需要增加额外的工艺步骤成为全芯片设计者的主

2012-04-23 10:17:42 3374

3374

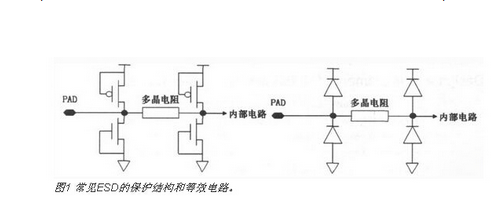

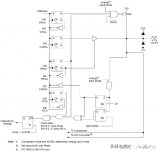

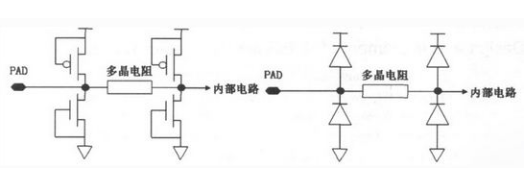

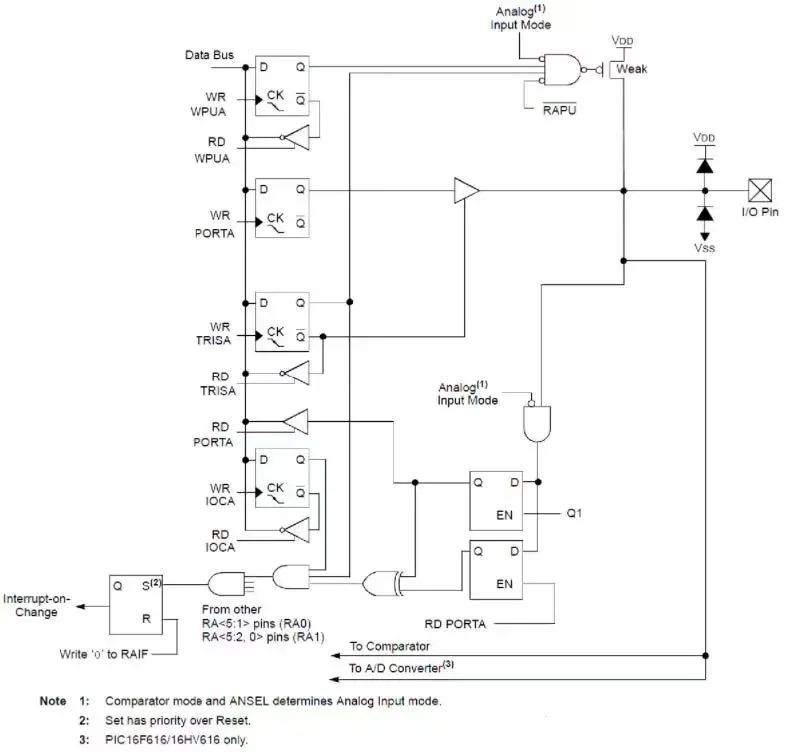

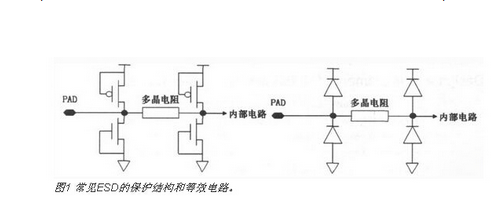

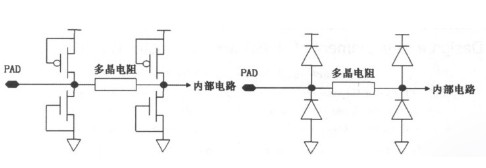

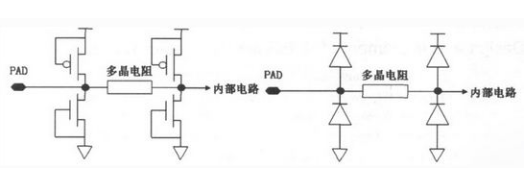

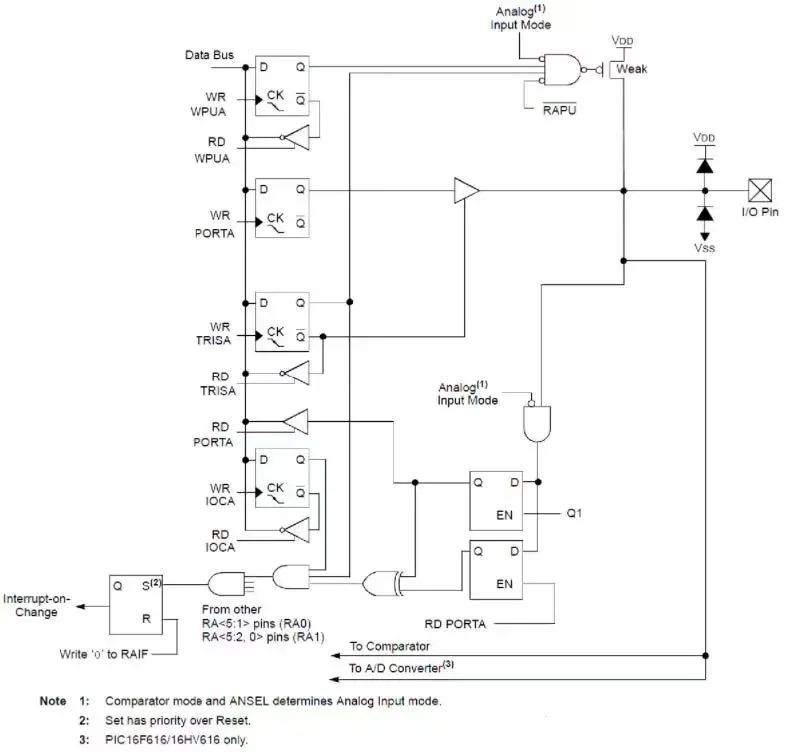

大部分的ESD电流来自电路外部,因此ESD保护电路一般设计在PAD旁,I/O电路内部。典型的I/O电路由输出驱动和输入接收器两部分组成。ESD 通过PAD导入芯片内部,因此I/O里所有与PAD直接

2014-12-24 11:05:47 2546

2546

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关

2017-12-05 09:03:40 12076

12076

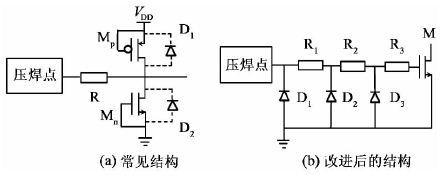

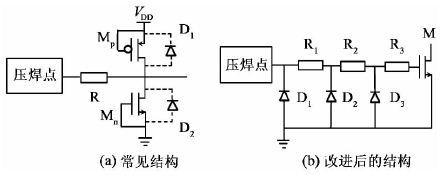

本文介绍了3种应用于笔者所开发的电容式触摸感应检测按键电路中的ESD保护结构。这3种保护结构在传统ESD结构基础上结合电容式触摸感应检测按键电路的具体特点进行全面改进,以达到保护电路且尽量少地增加

2018-12-14 16:05:34 8455

8455

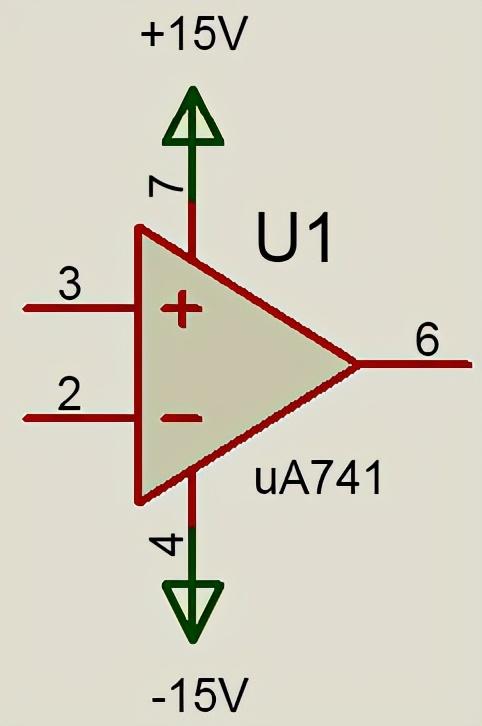

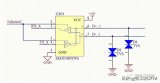

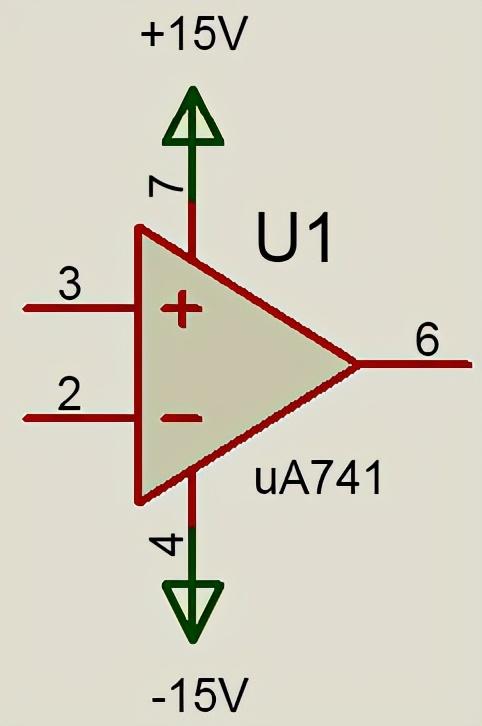

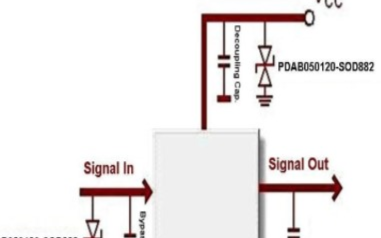

【任务】运放是模拟电路的灵魂核心器件,为使运放工作可靠且寿命达到设计预期,应该对运放采取必要的保护措施。运放作为一种高输入阻抗,高增益的器件,其损坏的原因主要有:电源极性接反,浪涌电压,过压,过载。试对uA741运放进行:极性保护、浪涌电压保护、过压保护、过载保护电路设计。

2023-03-31 15:59:31 3598

3598

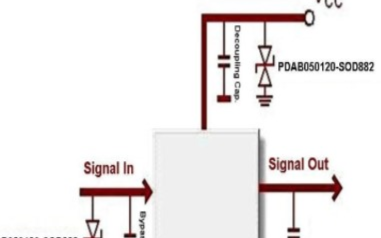

今天给大家分享的是:在电路设计和PCB设计如何防止ESD损坏设备。

2023-05-24 09:28:35 934

934

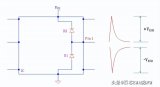

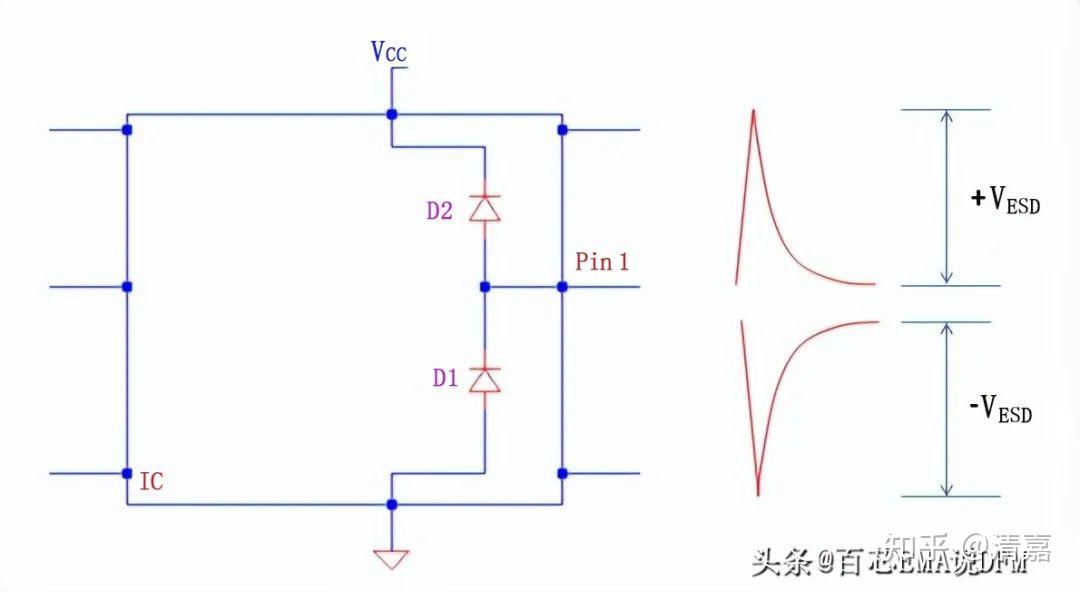

工程师都在知道在设计的时候会考虑到ESD,通常也会使用到TVS二极管。但是重点在于需要多保护,什么时候不需要保护了?这篇文章会对电路进行模拟。 一、ESD 保护电路的作用 主要就是 减少电压和电流

2023-07-01 19:40:01 4252

4252

ESD代表静电放电。许多材料可以导电并积累电荷。ESD 是由于摩擦带电(材料之间的摩擦)或静电感应而发生的。每当发生这种情况时,物体都会在其表面形成固定电荷(静电)。当这个物体放置得太靠近另一个带电物体或材料时,电压差会导致电流在它们之间流动,直到恢复电荷平衡。

2023-07-25 10:04:05 4000

4000

ESD代表静电放电。许多材料可以导电并积累电荷。ESD 是由于摩擦带电(材料之间的摩擦)或静电感应而发生的。

2023-08-16 09:19:32 1239

1239

ESD 静电放电给你的电子产品带来致命的危害不仅降低了产品的可靠性增加了维修成本而且不符合欧洲共同体规定的工业标准EN61000-4-2 就会影响产品在欧洲的销售所以电子设备制造商通常会在电路设计的初期就考虑ESD 保护电路本文将讨论ESD保护电路的几种方法.

2009-10-12 08:22:10

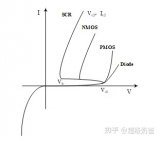

造成栅氧击穿,所以他不见的是一种很好的ESD设计方案,而且有源区越小则栅压的影响越大,而有源区越大则snap-back越难开启,所以很难把握。4、还有一种复杂的ESD保护电路:可控硅晶闸管(SCR

2021-12-04 07:00:00

所能耐受的最大峰值电压;4、用于信号传输电路保护时,一定要注意所传输信号的频率或传输速率,当信号频率或传输速率较高时,应选用低电容系列的管子,否则会影响通信质量。ESD静电二极管的封装形式:根据电路设计

2018-10-12 16:38:47

`ESD器件概述ESD保护元件的作用是转移来自敏感元件的ESD应力,使电流流过保护元件而非敏感元件,同时维持敏感元件上的低电压;ESD保护元件还应具有低泄漏和低电容特性,不会降低电路功能;不会对高速

2020-03-19 11:32:36

电路最常见的ESD保护器件主要有:TVS(瞬态电压抑制器)、MLV(片式压敏电阻)、PESD(聚合物静电保护器)。 ESD保护器件合理选取要根据其所保护的接口的信号频率,选择足够低电容以及稳定ESD

2018-06-01 15:18:55

亚太区市场营销副总裁麦满权指出:真正有效的ESD保护是不能完全集成到CMOS芯片之中的! 其次,也可以在物理电路设计方面下功夫,较敏感的电路元件应该尽量远离通孔或接缝处,如果可能的话,线缆连接器的接地

2008-07-29 09:51:53

UM5051/5052的重要参数ESD保护器件的种类ESD应用举例

2021-04-02 07:37:30

内部2 kV等级的ESD保护所需要的面积。半导体标准产品部亚太区市场营销副总裁麦满权指出:真正有效的ESD保护是不能完全集成到CMOS芯片之中的!其次,也可以在物理电路设计方面下功夫,较敏感的电路元件

2011-07-05 14:19:03

减少及应用环境不断变化,ESD保护的界线已经大幅改变。我们依次来审视一下这几种因素。1 几何尺寸更小——随着当今最先进的专用集成电路(ASIC)半导体工艺节点降至90纳米及以下,与ESD相关的失效

2011-01-27 10:35:10

ESD保护策略解析ESD保护策略解析手机、数码相机、MP3播放器和PDA等手持设备的设计工程师,正不断地面临着在降低整个系统成本的同时、又要以更小的体积提供更多功能的挑战。集成电路设计工程师通过在

2010-08-18 19:44:07

。为此,在电路设计中,ESD保护二极管,是必不可缺少的电路保护器件。何为ESD二极管?ESD,中文意思:静电释放,国际上习惯将用于静电防护的器材统称为“ESD”,是一种常用性的过压、静电保护元件,保护

2018-10-17 16:04:52

系统级ESD现象和器件级ESD现象有什么差异?ESD事件保护的系统级设计方法有哪几种?

2021-06-08 07:20:49

如何正确保护IC?ESD传递模式有哪几种?ESD保护和应用电路如何提高ESD保护?

2021-04-23 06:23:47

ESD波形是什么ESD方面所需考虑因素ESD如何选择最有效的保护方案

2021-04-08 06:07:41

ESD静电保护器是一种过压,防静电保护元件,用来保护电子设备中敏感电路受到ESD(静电放电)的影响,作用是转移来自敏感元件的ESD应力,使电流流过保护元件而非敏感元件,同时维持敏感元件上的低电压

2018-01-26 11:31:09

ESD静电保护器的选型: ①首先根据工作电压,确定要选择的VRWM值 ②根据电路布线情况确定保护的管脚数量及封装,如布线方便可选用多路保护的ESD,布线复杂时选用多个ESD器件。 ③根据信号

2016-05-26 16:22:40

了产品的可靠性,增加了维修成本,而且不符合欧洲共同体规定的工业标准EN61000-4-2,产品就不能够在欧洲销售。所以电子设备制造商通常会在电路设计的初期就考虑ESD保护。本文将讨论ESD保护电路的几种

2018-10-11 16:10:23

`<p><strong>保护电路设计方法</strong></p><br/>[/hide]`

2009-12-02 11:45:21

。 不过,总是有部分电路点较为敏感,同时也很难与外部隔离。因此,最有效的方法是使用保护元件来将电流导离较敏感的元件。也就是在电子系统的连接器或端口处放置ESD保护元件,使得电流流经保护元件,且不

2013-01-04 14:58:24

的ESD保护是不能完全集成到CMOS芯片之中的! 其次,也可以在物理电路设计方面下功夫,较敏感的电路元件应该尽量远离通孔或接缝处,如果可能的话,线缆连接器的接地应该要在系统信号引脚接触前连接到系统的接地

2014-02-14 10:30:16

现在的可穿戴电子产品保护器件要求更低的电容,更低的钳位电压和更小巧尺寸。可穿戴技术对电路设计人员而言,是一种有趣的挑战。为什么?想想这些设备被设计成与消费者密切相关的产品。因为他们是直接通过接触皮肤

2021-04-06 06:40:09

在实际电路设计中我们会采用以下几种方法的一种或几种来进行静电保护:

2021-01-21 07:55:09

在实际电路设计中我们会采用以下几种方法的一种或几种来进行静电保护:

2021-03-17 06:50:23

ESD保护设计必不可少。由于HDMI2.0的速度快,越来多的设备采用多个HDMI接口,所以对ESD保护方案提出了一些新要求。首选,低电容ESD保护对于高速条件下保持数据的完整性非常关键。其次,多个

2018-12-10 17:58:31

`<strong>IGBT保护电路设计方法<br/></strong><br/>[/hide]`

2009-12-02 11:03:27

使用的组件闸极氧化层很薄且接面很浅,很容易受到ESD的冲击而造成损伤。因此,这些电子产品需要额外的ESD保护组件来避免ESD冲击产生系统当机,甚至硬件受到损坏, 而NFC天线是必须有ESD保护组件保护的第一关。

2019-06-13 08:18:01

PCB布板时的ESD保护设计方法是什么?

2023-04-06 17:49:21

ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。几种典型的通用ESD保护电路分享个人的ESD保护9大措施

2019-06-28 08:00:00

SIM卡模块的SIM卡接口的ESD静电和闭锁保护 TVS 管 SMF05C随着物联网智能设备终端的发展,在多样化的物联网智能终端设备联网模块的设计中,在器件选型、电路设计等方面就需要考虑各种应用场

2021-02-01 11:21:33

TVS的ESD保护原理ESD TVS器件采用的技术汇总

2021-04-02 06:19:56

`内容简介《IGBT驱动与保护电路设计及应用电路实例》结合国内外IGBT的发展和最新应用技术,以从事IGBT应用电路设计人员为《IGBT驱动与保护电路设计及应用电路实例》的读者对象,系统、全面地讲解

2021-07-24 17:13:18

IGBT驱动与保护电路设计及应用电路实例链接:https://pan.baidu.com/s/1Zhphe5yvZi5xHr7Ng4ppOg提取码:lwrt内容简介《IGBT驱动与保护电路设计

2022-02-17 11:29:03

多样化,从单路的SOD-323到多路的SOT-23、SOT23-6L、QFN-10等,电路设计工程师可以根据电路板布局及接口类型选择不同封装的ESD静电保护二极管。

2021-03-11 13:00:12

标准EN61000-4-2,产品就不能够在欧洲销售。所以电子设备制造商通常会在电路设计的初期就考虑ESD保护。本文将讨论ESD保护电路的几种方法。ESD的危害ESD基本上可以分为三种类型:一是各种机器

2016-07-22 11:26:49

常见ESD保护元件可分为哪几类?不同便携应用的ESD保护解决方案

2021-06-08 06:15:34

卡中进行自动 ATR 检索以减少软件开发工作1 个用户卡 + 3 个 SAM所有卡侧引脚上的 8kV IEC 61000-4-2 ESD 保护电路设计已构建完成并通过测试

2018-11-19 11:49:18

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求。

2021-04-02 06:35:57

如何实现精密电路中精确有效的ESD保护 科技的不断进步,电子产品趋于微小化,精密化,那么如何给数据传输速率日趋攀高的系统提供有效可靠的ESD安全保护?其实静电的破坏不光光是存在于电路设计过程中

2013-12-27 09:32:22

,提高了芯片的运算速度。 但是,随着工艺的进步和尺寸的减小,静电释放(ESD),Elecyro Static Discharge)问题变得日益严峻。据统计,在集成电路设计中大约40%的失效电路是ESD问题造成的。如何设计ESD保护电路?这个问题急需解决。

2019-08-07 06:24:17

ESD的失效模式是什么?包括哪些?MOS集成电路中常用的提高ESD能力的手段有哪些?

2021-04-12 06:25:45

关键芯片组外部ESD保护要求硅ESD保护技术与无源ESD保护技术比较消除信号完整性问题的PicoGuard XS ESD保护技术智能手机等便携及消费产品电路保护及滤波应用示例

2021-04-09 06:55:32

本帖最后由 gk320830 于 2015-3-8 15:08 编辑

实现 ESD 失效最小化的电路设计原则 不要把对 ESD 敏感的器件——例如 CMOS 器件——的引脚直接连接到连接器

2013-02-25 10:40:00

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如:穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结...

2022-01-25 06:44:13

接口电路设计指南,设计手册更为强壮的接口IC,逻辑端和RS232端所有IO引脚都具有正负15V ESD保护。下载地址:接口电路设计指南

2009-10-24 12:04:48

控制ESD从设计开始 防止由ESD 引起的失效的第一步是电路设计。要从ESD出发,选用适合于应用需求的器件。对采用不易受 ESD 损坏的元器件的电路进行恰当的设计,就可减少电路板和系统现场失效

2013-12-11 12:31:34

难度特别大。理解器件如何提供高于1GB/s的串行数据速率和完整的通信协议保护可以避免这个问题。硕凯电子专注电路保护领域,对静电放电保护有着丰富经验,更多ESD静电保护器件及电路设计,请直接进入硕凯电子网站咨询在线客服。

2019-07-19 17:40:22

新型互补电容耦合ESD保护电路的设计提出了一种改进型的基于亚微米工艺中ESD 保护电路, 它由互补式电容实现, 结构与工艺简单。电路采用0.6μm1P2MCMOS 工艺进行了验证, 结果表明

2009-12-23 16:33:58

,不普通数字电路更容易遭到损坏,因为用于ESD保护的传输入保护结构会增加输入泄露,因此不能使用。所有ESD敏感器件均采用保护性封装。IC通常装在导电泡沫中或者防静电包装套管中,而后将容器密封在一个静电

2018-01-16 14:21:19

电容触摸屏的ESD保护电路ESD TVS能够提高电容触摸屏的抗干扰能力,有效防止因为系统电源和使用环境等干扰信号导致的电容触摸屏死机,重启,跳点误触发等问题;提高电容触摸屏的ESD能力,防止因为触

2021-12-13 15:50:37

分别设计一个过压 过温 过流的保护电路模块,完成过流保护电路设计,要求,当电流超过4.2A时保护电路输出高电平,当电流重新降至3.6A时保护电路的输出端重新回到低电平;完成过压保护电路设计,要求,当

2020-06-20 15:23:57

、ESD保护电路设计

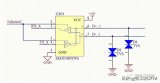

1、TVS 二极管和二极管电路

TVS 二极管保护电路是非工业低电压设置中最常见的电路之一。与嵌入在电源管理 IC 或微控制器中的其他 ESD 保护元件相比,TVS 浪涌二极管保护

2023-08-26 12:39:49

CMOS工艺中GG2NMOS结构ESD保护电路设计:采用GG2NMOS 结构的ESD 保护电路的工作原理和对其进行的ESD 实验,提出了一种保护电路的栅耦合技术方案,并达到了预期效果. 通过实验可以看出其性

2009-11-20 14:48:43 41

41 本文研究了在CMOS 工艺中I/O 电路的 ESD 保护结构设计以及相关版图的要求,其中重点讨论了PAD 到VSS 电流通路的建立。关键词:ESD 保护电路,ESD 设计窗口,ESD 电流通路Constru

2009-12-14 10:45:54 55

55 汽车电子保护电路设计作者: Mitchell Lee Hua Bai Jeff Witt 凌力尔特公司关键词:电池,电压,保护电路摘要:本文介绍了汽车电子的保护电路设计。汽车环境对电子产品而

2010-02-06 10:39:02 87

87 摘要:设计了一个适用于RnD的多功能ESD保护电路,并对其工作原理和测试结果进行了论述。这个保护电路不仅能够进行传统的ESD保护,还可以避免内部电路因受到过大场强而产生

2010-04-28 09:45:28 24

24 摘要:采用GG-NMOS结构的ESD保护电路的工作原理和对其进行的ESD实验,提出了一种保护电路的栅耦合技术方案,并达到了预期效果.通过实验可以看出其性能达到了人体放电模式的2级

2010-05-08 09:41:45 24

24 HDMI接口的ESD保护电路及解决方案

RClamp0524P,具有低电

2009-11-20 09:17:54 3338

3338

整体电路采用Hspice和CSMC 2P2M 的0.6 m CMOS工艺的工艺库(06mixddct02v24)仿真,基于CSMC 2P2M 0.6 m CMOS工艺完成版图设计,并在一款多功能数字芯片上使用,版图面积为1 mm1 mm,参与MPW(多项目晶圆)计划流

2012-04-18 15:36:06 77

77 双极性工艺 ESD保护电路 :

2012-04-19 10:47:51 1807

1807

基于FPGA的惯性平台测试保护电路设计..

2016-01-04 17:03:55 7

7 电子专业单片机相关知识学习教材资料——ESD保护电路的设计,感兴趣的小伙伴们可以瞧一瞧。

2016-09-13 17:46:48 0

0 ESD放电二级管是一种过压、防静电保护元件,是为高速数据传输应用的I/O端口保护设计的器件。ESD保护器件是用来避免电子设备中的敏感电路受到ESD(静电放电)的影响。

2017-11-08 14:15:14 77813

77813

当前的集成电路设计中大量采用了可控硅的设计结构来进行 ESD 的保护,但是一般的SCR 保护结构很难满足现在低电压,以及一些特殊要求的集成电路 ESD 保护的要求。研究一种低触发电压的可控硅结构保护电路,通过和工艺寄生参数的结合,满足了低触发电压的设计要求。

2018-04-29 11:37:00 8350

8350 偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进行防范。

2019-02-25 16:11:34 5860

5860

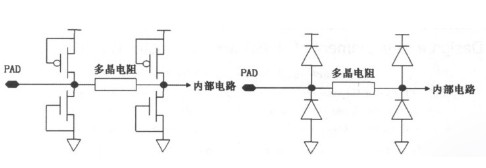

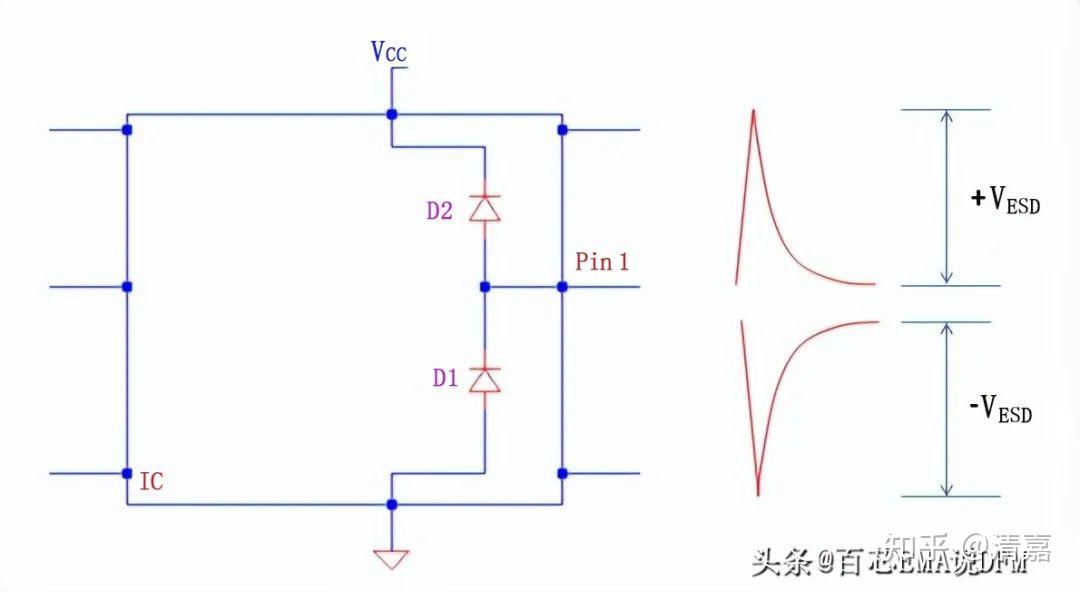

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

2019-03-04 14:24:01 4168

4168

ESD保护电路的设计目的就是要避免工作电路成为ESD的放电通路而遭到损害,保证在任意两芯片引脚之间发生的ESD,都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能箝位工作电路的电压,防止工作电路由于电压过载而受损。

2019-04-08 15:26:11 2192

2192

随着CMOS集成电路产业的高速发展,越来越多的CMOS芯片应用在各种电子产品中,但在电子产品系统的设计过程中,随着CMOS工艺尺寸越求越小,单位面积上集成的晶体管越来越多,极大地降低了芯片的成本

2020-12-30 10:28:00 2

2 非常经典的保护电路设计方法介绍。

2021-06-21 10:48:49 92

92 来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如:穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发器锁死;短路反偏的PN结...

2021-12-01 11:21:13 0

0 《IGBT驱动与保护电路设计及应用电路实例》第2版

2022-02-08 15:12:33 0

0 偏置的PN结;熔化有源器件内部的焊接线或铝线。为了消除静电释放(ESD)对电子设备的干扰和破坏,需要采取多种技术手段进行防范。

2022-02-15 16:15:34 3302

3302

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。在设计过程中,通过预测可以将绝大多数设计修改仅限于增减元器件。通过调整PCB布局布线,能够很好地防范ESD。以下是一些常见的防范措施。

2022-03-11 09:24:58 2175

2175 影响 ESD 保护要求的集成电路趋势

2022-11-14 21:08:21 2

2 用于SD卡保护的4重ESD保护阵列-PESD3V3X4UHM

2023-02-20 20:11:46 1

1 今天给大家分享的是:在电路设计和PCB设计如何防止ESD损坏设备。

2023-06-05 09:34:28 550

550

静电放电(ESD)会对集成电路(IC)造成破坏性的能量冲击,良好的IC设计能够在IC装配到应用电路的过程中保护IC免遭ESD冲击的破坏。安装后,IC还必须能够承受ESD穿过静电防护电路进入最终电路

2023-06-10 15:40:58 582

582

电子设备需要使用外部保护器件,除了因为:产品的功能集成化造成I/O接口的增多,为ESD进入电路及电压敏感型元件提供了有效路径;产品外观小型化,使得IC更容易受到ESD损坏;满足ESD抑制标准

2021-12-14 05:17:19 746

746

ESD静电保护管是一种常用性的过压、静电保护元件,保护电子设备中敏感电路免遭静电影响。ESD静电保护管并联于电路中,当电路正常运作时,ESD静电保护管处于高阻态,不影响线路正常工作;当电路出现异常

2022-09-22 17:36:59 4515

4515

什么是电路保护?电路保护器件选型要领,怎么选?本篇优恩就围绕这两个问题作出解答。一、什么是电路保护?答:电路保护器件是电路保护极其重要的一个环节,选型没选好,则会影响后期使用,发现一系列问题。很多

2022-10-19 14:38:00 616

616

ESD静电保护管是一种常用性的过压、静电保护元件,保护电子设备中敏感电路免遭静电影响。ESD静电保护管并联于电路中,当电路正常运作时,ESD静电保护管处于高阻态,不影响线路正常工作;当电路出现异常

2023-06-05 10:36:54 869

869

在电路设计时,一般都是需要考虑ESD防护电路的设计的,否则就会非常容易导致电子产品轻易的就被电磁,静电等干扰损坏。 通常设计电路时都会考虑到使用ESD保护元器件来作为基本的工具,但是怎么放,放哪里

2023-11-06 10:51:31 279

279

电子发烧友网站提供《IGBT的保护电路设计方法.pdf》资料免费下载

2023-11-18 09:39:47 10

10 Resistor不单独用于芯片的ESD保护,它往往用于辅助的ESD保护,如芯片Input第一级保护和第二级保护之间的限流电阻。如图5,当ESD电流过大,第一级ESD器件难以将电压钳位至安全区域时,第二级ESD器件的导通将使其与电阻分压,从而进一步降低进入内部电路的电压。

2023-12-07 09:15:04 515

515

正在加载...

电子发烧友App

电子发烧友App

评论