由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。

2023-07-18 09:22:31 875

875

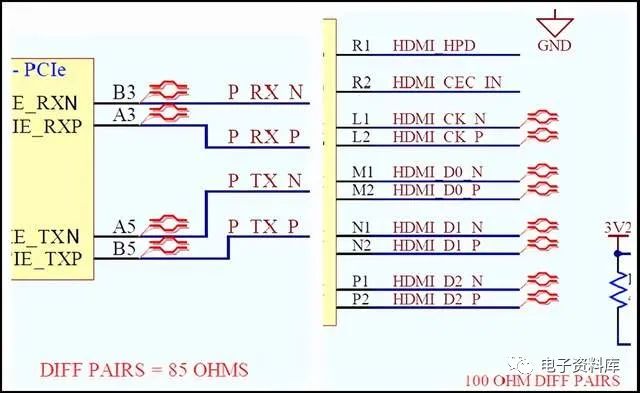

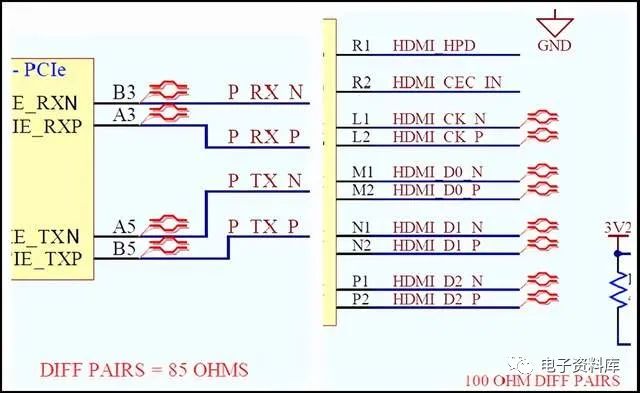

、PCB供应商反馈信息等,而最终得出此推荐设计。适用于大部分PCB供应商的制程工艺标准和具有阻抗控制要求的PCB板设计。 一、 双面板阻抗设计 100欧姆差分阻抗推荐设计①、包地设计:线宽、间距 7/5/7 mil地线宽度20mil信号与地线距离6mil,每400mil内加接地过孔;②

2020-11-02 14:05:20 11191

11191 随着高速信号传输,对高速PCB设计提出了更高的要求,阻抗控制是高速PCB设计常规设计,PCB加工十几道工序会存在加工误差,当前常规板厂阻抗控制都是在10%的误差。理论上,这个数值是越小越好

2023-06-25 10:05:15 528

528

可控阻抗是由PCB迹线及其相关参考平面形成的传输线的特性阻抗。当高频信号在PCB传输线上传播时,它是相关的。控制阻抗对于解决信号完整性问题,即无失真的信号传播。

2023-09-28 10:01:01 2107

2107

的电路里,对交流电所起的阻碍作用叫做阻抗。阻抗常用Z表示。阻抗由电阻、感抗和容抗三者组成,但不是三者简单相加。阻抗的单位是欧姆。 PCB中的阻抗是指电路板上导线、电源、负载和其他元件之间的电阻抗。PCB阻抗控制是设计PCB电路板的重要

2024-01-03 08:40:18 534

534

PCB 阻抗是高频工作时电路的电容和电感的组合,虽然也是以Ω为单位测量,但是与作为直流特性的电阻有些不同,阻抗是一种交流特性,意味着与频率有关,而电阻则不是。

2024-02-22 10:20:33 545

545

PCB阻抗控制 详情见附件

2017-11-26 14:13:37

在实际情况中,需要在数字边际速度高于1ns或模拟频率超过300Mhz时控制迹线阻抗。PCB 迹线的关键参数之一是其特性阻抗(即波沿信号传输线路传送时电压与电流的比值)。印制电路板上导线的特性阻抗

2019-05-30 07:18:53

PCB阻抗控制打样要注意哪些问题?

2023-04-14 15:55:11

PCB阻抗与连接排线的阻抗需要叠加吗?

2023-04-11 16:17:59

上的导体,其阻抗值应控制在某一范围之内,称为“阻抗控制”。影响PCB走线的阻抗的因素主要有铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。所以在设计PCB

2018-09-18 15:50:04

PCB板阻抗设计:阻抗线有无参考层阻抗如何变化?生产PCB时少转弯的阻抗线的阻抗更容易控制稳定性?

2023-04-10 17:03:31

摘要: 本文具体分析了PCB板的特性阻抗和特性阻抗的控制办法。 1、电阻 交流电流流过一个导体时,所受到的阻力称为阻抗 (Impedance),符合为Z,单位还是Ω。 此时的阻力同直流电流所

2018-09-14 16:21:15

本文具体分析了PCB板的特性阻抗和特性阻抗的控制办法。

2021-04-25 07:27:35

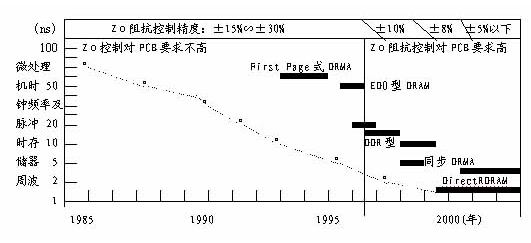

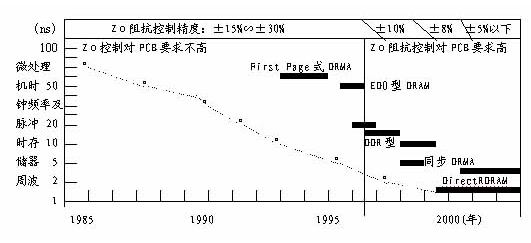

搭载RIA的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的 PCB 板件的特性阻抗控制精度不在局限于原来的±15%或士10%,有的阻抗控制精度要求提高到±8%甚至

2023-09-21 06:14:35

通道。 需要说明的是,在具体的PCB层叠设置时,要对以上原则进行灵活掌握和运用,根据实际单板的需求进行合理的分析,最终确定合适的层叠方案,切忌生搬硬套。 PCB设计走线的阻抗控制简介 在PCB

2023-04-12 15:12:13

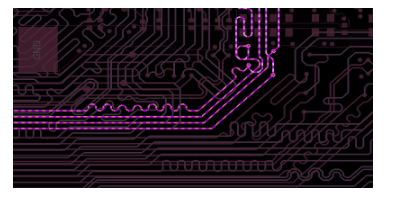

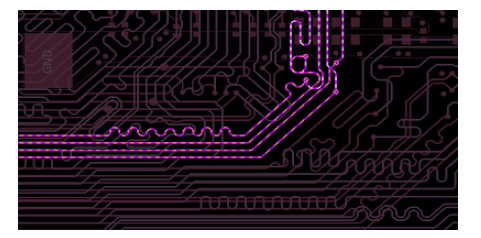

ST25RU3993-eval PCB 内部放大器输出差分走线看起来不适合首选阻抗。查看红色圈出的痕迹。这些不应该是 100 欧姆差分与紫色混频器反馈迹线相同吗?布局中的迹线宽度显然与紫色标记的 100 欧姆差异迹线不同。

2023-01-16 08:35:17

cadence pcb设计各层阻抗都是怎么定的呢?为什么每层显示的阻抗都不一样?

2016-01-25 22:55:40

为什么说控制阻抗在对PCB线路板如此重要?

2023-04-14 15:09:13

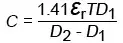

越小其特性阻抗越低(差分阻抗与差份线队之间的间距成反比)。差分传输线特性阻抗通常情况下为100Ω,有时也用到75Ω。考虑到多层PCB板生产时PCB迹线可分布于表面或者内层,这两种情况下PCB迹线

2009-09-28 14:48:47

在能量上的传输。3、特性阻抗控制(Z0 )上述此种“讯号”传输时所受到的阻力,另称为“特性阻 抗”,代表符号为Z0。所以,PCB导线上单解决“通”、“断”和“短路”的问题还 不够,还要控制

2015-04-10 20:52:45

各位pcb设计师你们好请问PCB布线有关的如何计算阻抗 收到者求回复感谢!

2019-09-25 03:18:38

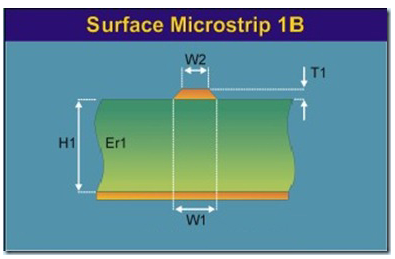

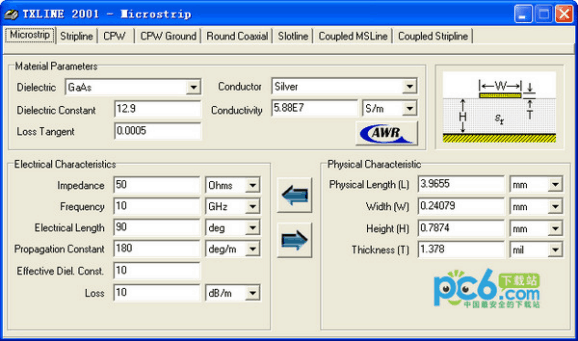

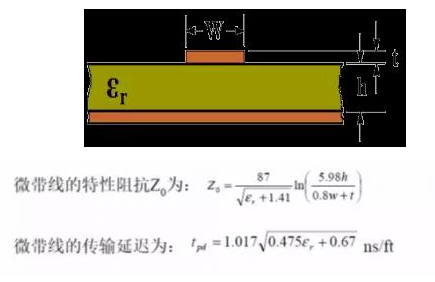

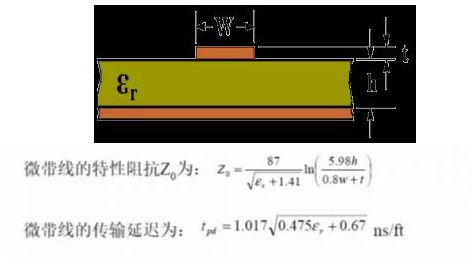

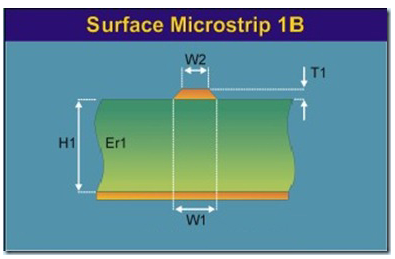

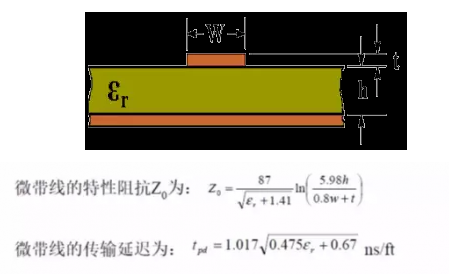

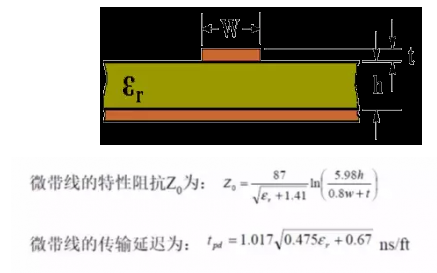

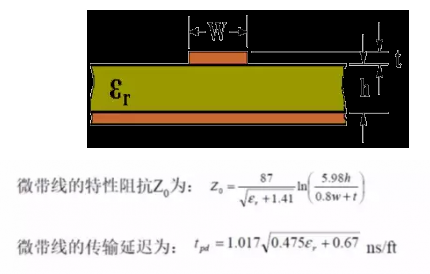

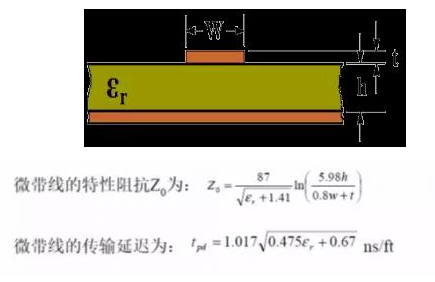

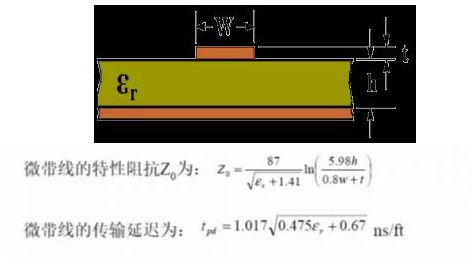

实现阻抗控制的传输线配置方式控制阻抗 PCB 通常使用微波传输带或带状线传输线路,以单端(未平衡)或差分(已平衡)配置的方式生产。单端配置以下为几种常见单端微波传输带和带状线传输带的配置:注意以下各

2009-09-28 16:16:56

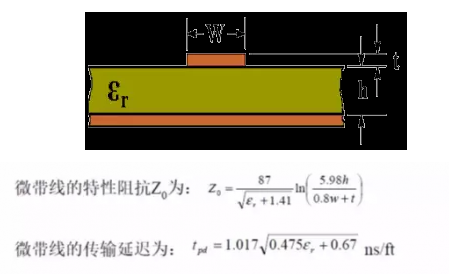

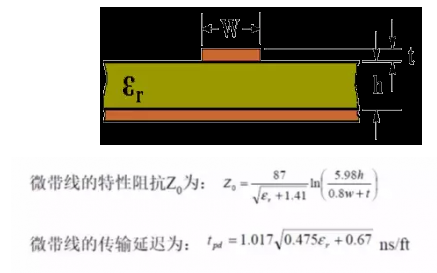

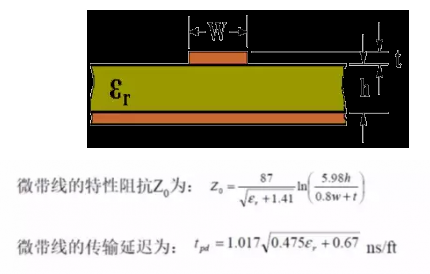

影响PCB特性阻抗的因素:介质厚度H、铜的厚度T、走线的宽度W、走线的间距、叠层选取的材质的介电常数Er、阻焊的厚度。 一般来说,介质厚度、线距越大阻抗值越大;介电常数、铜厚、线宽、阻焊厚度

2020-09-07 17:54:12

制作的线路板的铜线),相对某一参考层(也就是常说的屏蔽层、影射层或参考层),其高频信号或电磁波在传播过程中所受的阻力称之为特性阻抗,它实际上是电阻抗、电感抗、电容抗等一个矢量总和。2、控制PCB

2016-10-10 14:38:27

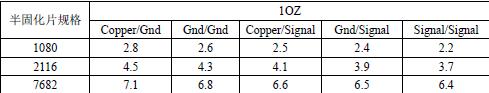

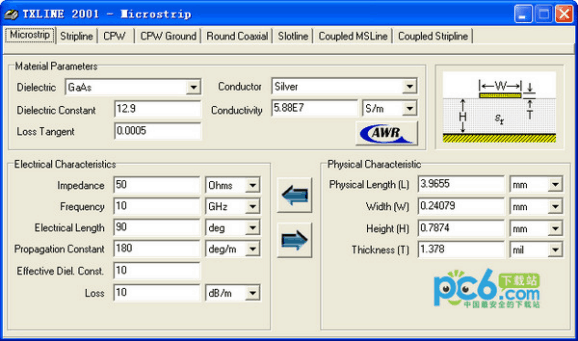

线宽的计算,然后根据计算好的线宽来进行布线,即可达到控制特性阻抗的效果。如图1-21所示,1.6MM的厚度的PCB板的层压结构。 图1-21 1.6MM的厚度的PCB板的层压结构 第一步,如图

2020-09-07 17:52:55

PCB阻抗怎么来的?如何计算?

2021-03-18 06:27:04

应该是另作它用,与PCB制板时的阻抗控制是两回事。因此在设计PCB时,依然要控制阻抗,就像DDR的时钟那样。这么理解对吗?

2017-11-20 10:21:31

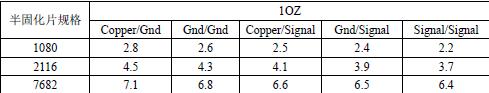

PCB设计时,注意控制走线时的阻抗控制,往往可以做到很好的匹配。 对于通常的聚酯胶片PCB 来说,传输线的长度和微带线 Stub 效应是需要考虑的, 在本设计指南里面,主要是针对 4 层的 1080+2116 聚酯胶片PCB 进行相关的阻抗匹配控制。

2019-05-17 10:40:14

越来越多的厂商要求指定PCB板上的DC迹线阻抗。以下从设计商的角度道出了指定和

2006-04-16 20:23:26 606

606 在正常的PCB设计条件下,主要以下几个因素由PCB制造对阻抗产生影响: 1、介

2006-04-16 21:44:51 2179

2179 传输线阻抗计算中的有关问题

结合目前我公司PCB板加工厂家的工艺能力,在用polar公司阻抗计算器CITS25计算PCB板上迹线特性阻抗时,

2009-09-28 14:54:20 2005

2005

阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,我对这个问题有了一些粗浅的认识,愿和大家分享。

2011-05-06 11:28:46 4254

4254

随着PCB 信号切换速度不断增长,当今的PCB 设计厂商需要理解和控制PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线。

2016-03-24 14:48:57 0

0 PCB阻抗设计方面的干货。

2017-01-13 17:13:49 0

0 PCB高级设计之共阻抗及抑制

2017-01-24 16:29:19 0

0 时,若导线的长度接近信号波长的1/7, 此时的导线便成为信号传输线,一般信号传输线均需做阻抗控制。PCB制作时,依客户要求决定是否需管控阻抗,若客户要求某一线宽需做阻抗控制,生产时则需管控该线宽的阻抗。

2017-07-27 11:20:07 0

0 阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。在高速 PCB 设计中,阻抗的匹配与否关系到信号的质量优劣。PCB 走线什么时候需要做阻抗匹配?

2017-08-28 16:33:23 26

26 随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。相应于现代数字电路较短的信号传输时间和较高的时钟速率,PCB 迹线不再是简单的连接,而是传输线

2017-11-26 14:28:01 1036

1036 PCB阻抗设计与阻抗类型图解

2018-01-20 10:45:33 0

0 本文主要介绍的是阻抗匹配,首先介绍了阻抗匹配条件,其次阐述了如何理解阻抗匹配及常见阻抗匹配的方式,最后介绍了pcb阻抗匹配如何计算,具体的跟随小编一起来了解一下。

2018-05-02 17:11:28 38669

38669

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2018-10-14 09:28:00 1441

1441 PCB迹线的阻抗将由其感应和电容性电感、电阻和电导系数确定。影响PCB走线的阻抗的因素主要有: 铜线的宽度、铜线的厚度、介质的介电常数、介质的厚度、焊盘的厚度、地线的路径、走线周边的走线等。PCB阻抗的范围是 25 至120 欧姆。

2019-08-08 15:23:43 3818

3818

端接传输线迹线阻抗过高会导致接收器产生常见的模式问题。

3. 精密迹线串联会使信号大幅衰减

如果迹线阻抗过高,LVDS和千兆位以太网等长精密迹线和高速串行总线会使信号大幅衰减。

2019-06-24 15:14:58 723

723 达到稳态,这也是不实际的因为通常这样做会增加PCB板层,成本提高很多。此外缩短走线在某种情况下在物理上也是不可能的。

第三个方法就是在传输线的两端用等于线的特征阻抗的阻抗端接传输线以排除反射。

2019-05-27 14:01:27 1883

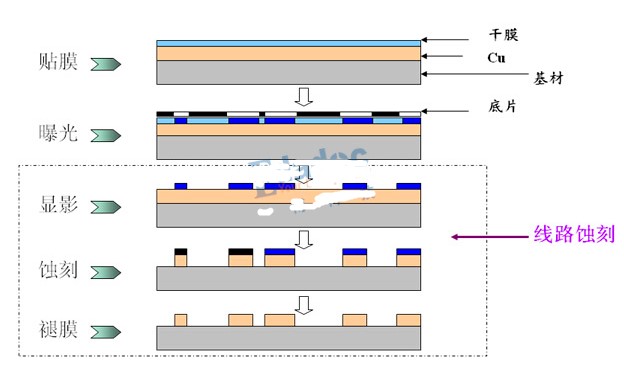

1883 具有高精度控制特性阻抗性的PCB制造,是整体把握的设计技术所保证。而这一系统的整体设计技术,主要包括了基板材料的介电特性、部品特性、设计方法、PCB制造特性、组装方法等的技术。正如图1所描述那样,高精度控制特性阻性的PCB有着三大方面(高精度层压技术、高精度电镀技术、高精度图形形成技术)的要素技术。

2019-05-23 14:41:46 518

518 。不仅搭载RIMM的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的PCB板件的特性阻抗控制精度不在局限于原来的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,这对PCB制造厂来说确实是很大的挑战。

2019-05-21 14:47:01 818

818

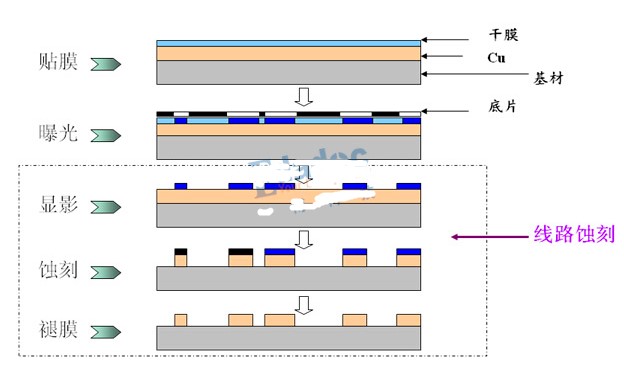

为什么常规阻抗控制只能是10%的偏差,那一定要了解加工步骤,其中包括层压、蚀刻及PCB覆铜板材公差及PCB阻焊工序的制作。

2019-04-19 15:48:04 5655

5655

在高速PCB设计时为了防止反射就要考虑阻抗匹配,但由于PCB的加工工艺限制了阻抗的连续性而仿真又仿不到,在原理图的设计时怎样来考虑这个问题?

2019-06-21 17:03:47 6432

6432 我的第一块PCB远离高速数字设备。它只是单层PCB上的放大器电路,控制阻抗甚至不是事后的想法。一旦我开始研究需要高采样率的电光系统,控制阻抗始终是一个关键的设计问题。电路板上的受控阻抗是PCB布局问题,我在处理PCB一段时间后感觉不太舒服。

2019-07-25 09:13:38 1760

1760 阻抗控制PCB 在高频应用中,信号不会因为它们在PCB中的路径而降级。 在PCB设计中通过叠层计算阻抗控制时需要注意的四个问题 在高速PCB设计过程中,堆栈设计和阻抗计算是迈向顶端的第一步。阻抗

2019-07-29 14:02:17 2435

2435

阻抗控制线是否会增加PCB板的成本?是的,会增加PCB的制造成本设计。但是,有3个主要元素可以控制PCB制造成本。

2019-07-31 11:09:56 2860

2860 、PCB供应商反馈信息等,而最终得出此推荐设计。适用于大部分PCB供应商的制程工艺标准和具有阻抗控制要求的PCB板设计。

2019-08-01 17:45:55 0

0 没有阻抗控制的话,将引发相当大的信号反射和信号失真,导致设计失败。

2019-10-14 14:47:58 4073

4073

随着 PCB 信号切换速度不断增长,当今的 PCB 设计厂商需要理解和控制 PCB 迹线的阻抗。

2019-08-30 08:45:40 3032

3032 阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-09-06 11:52:29 12487

12487

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-10-04 17:17:00 10392

10392

在阻抗控制的早期,使用了固定增益的PD控制,这种方法实现简单,但在机器人位形、速度变化时无法保持理想阻抗。经过学者们的努力,发展了多种阻抗控制方法,总的看来有两类实现阻抗控制的方法,一类是基于动力学模型的阻抗控制方法,另一类是基于位置的阻抗控制方法。

2019-09-25 09:28:58 15980

15980 常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内存、LVDS信号等,均需要进行阻抗控制。阻抗控制最终需要通过PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-12-31 15:42:08 2238

2238

PCB设计为何一般控制50欧姆阻抗?

2020-01-15 16:17:41 9751

9751 PCB线路板阻抗,指的是电阻和对电抗的参数,对交流电所起着阻碍作用。在PCB线路板生产中,阻抗处理是必不可少的,PCB线路板为什么要做阻抗?

2020-02-24 11:02:21 4798

4798 本文档的主要内容详细介绍的是PCB的结构和加工流程线路阻抗控制线路阻抗计算的详细资料简介。

2020-02-28 08:00:00 0

0 没有阻抗控制的话,将引发相当大的信号反射和信号失真,导致设计失败。常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内VDS信号等,均需要进行阻抗控制。阻抗控制最终需要通过PCB

2020-07-14 10:25:00 6

6 的是,阻抗控制使 PCB设计 人员和制造商可以管理这种现象。 什么是阻抗? 阻抗测量交流 电流 过 电路 时的 电阻 。它是高频电路的 电容 和感应的结合。像电阻一样,阻抗的单位是欧姆。但是,由于电阻是直流电的特性,因此请勿混淆这两个值。当信号

2020-09-03 19:04:58 6540

6540 还可以确保沿着互连的一致的传播延迟,从而允许并行高速 PCB 信号(例如 PCIe 中的信号)的长度精确匹配以防止歪斜。 由于阻抗控制的布线需要精确制造 PCB 互连件,因此制造商已花费大量精力完善蚀刻工艺,以确保迹线几何形状与 PCB 设计软件中使用

2020-09-25 18:59:16 1530

1530 迹线阻抗控制是正确确定迹线大小的简单问题。当单独考虑一条走线时,其阻抗将具有明确定义的值。但是,当靠近另一个走线或导体时,由于意外耦合,走线的阻抗将不同于其设计值。这种令人讨厌的事实会导致沿互连

2021-02-17 05:32:00 3111

3111

迹线阻抗控制是正确确定迹线大小的简单问题。当单独考虑一条走线时,其阻抗将具有明确定义的值。但是,当靠近另一个走线或导体时,由于意外耦合,走线的阻抗将不同于其设计值。这种令人讨厌的事实会导致沿互连

2021-02-13 07:06:00 1199

1199

在 PCB 设计阶段要注意阻抗控制,这一点很重要。阻抗控制涉及为 PCB 上的走线和传输线指定所需的阻抗。这对于高速信号尤其重要,并且可能会受到您的影响。基材,铜线宽度和布线。即使在布置好电路板

2020-10-09 21:12:57 1297

1297 更高速的动作。不仅搭载 RIMM 的计算机产品,而且很多的电子产品也需要基板上的电路能很好地与之匹配,一些客户相应使用的 PCB 板件的特性阻抗控制精度不在局限于原来的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,这对 PCB 制造厂来说确实是很大的挑战。本文主要针对如何满足客户

2023-02-03 14:02:05 791

791 众所周知,阻抗控制是我们做高速设计最基本的原则,各大板厂在PCB加工也会保证10%左右的阻抗误差。看似那么轻松的一个板厂的承诺,要是出现了阻抗在误差范围以外的时候,客户和板厂到底谁是出问题的一方

2021-03-24 09:48:19 4576

4576 在PCB制造中,迹线代表导体,层压板代表绝缘体,平面代表屏蔽。因此,印刷电路板的阻抗取决于制造过程中使用的尺寸和材料。

2021-02-27 10:26:01 2180

2180 PCB布线短是为了尽量忽略信号在传输过程中的反射,那为什么会产生反射呢?

实际上反射的原因是互连线中阻抗发生了突然变化,那什么叫做阻抗,影响阻抗的因素又是什么呢?

通俗来讲:传输线上某一点处的电压与电流的比值表示在这个位置信号感受到的阻抗。

2021-01-05 17:02:00 35

35 为了很好地对PCB进行阻抗控制,首先要了解PCB的结构。

2021-03-22 14:30:38 0

0 在 STM32 无线系列产品的 PCB 设计中,需要对射频部分电路进行阻抗控制,良好的阻抗控制可以减少信号衰减、反射和 EMC 辐射。本篇 LAT 主要介绍印制电路板(PCB)上射频走线阻抗仿真计算

2022-06-16 16:36:21 5063

5063 单面PCB,没有地平面,采用双侧都有地线的共面波导结构,就能实现布线阻抗控制:

2022-08-12 14:58:43 1347

1347 、PCB供应商反馈信息等,而最终得出此推荐设计。适用于大部分PCB供应商的制程工艺标准和具有阻抗控制要求的PCB板设计。

2022-10-12 10:23:17 5063

5063 随着高速信号传输,对高速 PCB设计提出了更高的要求,阻抗控制是高速PCB设计常规设计,PCB加工十几道工序会存在加工误差,当前常规板厂阻抗控制都是在10%的误差。理论上,这个数值是越小越好

2023-06-22 08:10:02 486

486

决于选择的PCB叠层结构。 由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。 PCB叠层设计 “ 层的定义设计原则 1、主芯片相临层

2023-07-19 07:45:02 543

543 决于选择的PCB叠层结构。由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。 一、PCB叠层设计 层的定义设计原则: 1)主芯片相临层

2023-08-01 07:45:01 1760

1760

阻抗控制pcb

2023-09-18 10:40:37 595

595 通孔的阻抗控制对PCB信号完整性会触发什么样的影响?

2023-10-17 11:56:11 254

254

一站式PCBA智造厂家今天为大家讲讲PCB设计阻抗不连续怎么办?PCB设计阻抗不连续问题的解决方法。大家都知道PCB设计阻抗要连续。但是PCB设计也总有阻抗不能连续的时候。怎么办?下面深圳PCBA

2023-09-22 09:32:05 634

634

从理论到实践之pcb阻抗控制表的使用

2023-09-26 10:34:15 324

324 电路板中的PCB阻抗CBA

2023-10-13 11:15:19 622

622 什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配? 阻抗匹配是指在电路传输信号时,控制电路中信号源、传输线和负载之间的阻抗相等的过程,从而确保信号的完整性和可靠性。在高速PCB设计中,阻抗

2023-10-30 10:03:25 919

919 PCB阻抗设计及计算简介

2022-12-30 09:20:41 11

11 如何设置PCB迹线角度?最好是45度还是圆弧?90度直角接线可以吗?

2023-11-30 18:18:39 753

753

没有阻抗控制的话,将引发相当大的信号反射和信号失真,导致设计失败。常见的信号,如PCI总线、PCI-E总线、USB、以太网、DDR内存、LVDS信号等,均需要进行阻抗控制。

2023-12-18 15:52:33 142

142

pcb电路板阻抗设计,确保最佳性能

2023-12-28 10:27:22 245

245 里,对交流电所起的阻碍作用叫做阻抗。阻抗常用Z表示。阻抗由电阻、感抗和容抗三者组成,但不是三者简单相加。阻抗的单位是欧姆。 PCB中的阻抗是指电路板上导线、电源、负载和其他元件之间的电阻抗。PCB阻抗控制是设计PCB电路板的重要环节,以

2024-01-05 08:45:02 219

219

所起的阻碍作用叫做阻抗。阻抗常用Z表示。阻抗由电阻、感抗和容抗三者组成,但不是三者简单相加。阻抗的单位是欧姆。PCB中的阻抗是指电路板上导线、电源、负载和其他元件之间的

2024-01-05 10:44:00 304

304

pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷电路板)设计和制造过程中,通过优化电气特性和信号完整性,确保设计满足特定的阻抗要求。在高速数字和模拟电路中,阻抗控制

2024-01-17 16:38:04 722

722 一站式PCBA智造厂家今天为大家讲讲如何解决pcb设计阻抗不连续的问题?解决PCB设计中的阻抗不连续的方法。当涉及到PCB(Printed Circuit Board)设计时,阻抗一直是一个非常重要

2024-03-21 09:32:59 86

86

电子发烧友App

电子发烧友App

评论