Allegro中如何进行颜色设置

在ALLEGRO中,如何对网络设置颜色?比如对POWER网络,我想让它显示为红颜色!怎么做?RichardLC网友回复:我想你

2008-03-22 16:40:44 11362

11362

我在走差分线的时候出线一定要走一段平行线然后才能转角度,在空间比较有限的地方很不方便,太占地方了。有些PCB的差分线在出线后马上就可以转角度,有什么地方可以设置吗?

2016-06-29 20:45:47

自己总结下差分对规则的设置

2016-03-01 01:48:30

一般的,需要自己先提前计算好层叠,阻抗,计算好单端和差分的线宽,线距,计算之前,需要自己根据BGA间距,走线密度等,做一个预估,这样,计算出来的更有针对性,也更容易一次成功。

2019-05-22 06:57:53

我画的差分电路板有差分线,需要用蛇形线让他们等长,可是我的蛇形线只能一根线一根线的画,怎样让一对差分线同时画出蛇形线?是不是哪里的设置需要更改?

2012-07-11 20:24:14

差分线能走GHz以上的频率,差分线为什么能走高速?是否与抗干扰能力强有关?为何?

2015-11-08 14:10:40

的变化,一时让很多硬件工程师头疼不已。问题的分析:造成HDMI辐射超标的原因有多种可能,就不一一分析了,这里只重点谈谈与差分线传输线长度差有关的问题。理想情况下,差分信号是正负对称的,其共模份量为零

2020-11-04 09:40:06

差分线对等长补偿,请问这个走线里面ABC三个地方不等长,请问如何补偿?是在abc三个地方分别补偿还是在ab之间补偿。B到C的距离超过了600mil。

2023-11-02 15:09:48

差分线对的PCB设计要点

2012-08-20 14:52:39

差分线抗干扰能力强,信噪比高,辐射小,带宽容量大等众多优点,所以在目前的高速电路设计中,都选取差分线作为通信方式。差分线使用两根走线传输一路信号,两根线上携带的信息是相同的,但是信号的相位差是180

2020-10-29 08:56:44

记得在刚学习差分线(对)的时候,总是对一些概念把握不准,很多概念都会混淆,比如差分(很多人还会误解成差模)、共模、奇模与偶模,以及由此延伸出的差分阻抗、共模阻抗、奇模阻抗与偶模阻抗,光是这些概念

2019-08-07 08:44:05

,尤其是串扰以及损耗等问题。为了解决这些问题,一种全新的数据传输方式应运而生,如图1所示,他就是-----差分(差分线、差分互联)。

2019-07-23 07:52:10

差分线绕线方法比较

2017-12-05 14:25:56

差分线绕线方法比较差分线抗干扰能力强,信噪比高,辐射小,带宽容量大等众多优点,所以在目前的高速链路设计中,都选取差分线作为通信方式。 差分线使用两根走线传输一路信号,两根线上携带的信息是相同

2014-04-15 10:51:05

差分线要注意什么问题?

2015-06-29 00:31:58

差分线阻抗为什么要是85Ω呢?

2016-01-31 20:25:50

有一组线:里面有多对差分线对,有多根单端线,差分线对的走线规则已经设置了(线宽5MIL,线距5mil),请问如何设置差分线对与差分线对之间间距(比如我想要的线对之间间距10mil)?如何设置差分对与单端线之间的距离(比如我想要间距8mil)?

2019-11-19 14:17:31

我想问一下差分信号length tuning中,gap,amplitude increasegap increase如何设置,和差分线的width和gap是什么关系

2019-09-06 05:35:21

PCB布线中,有着许多需要注意的点,比如:1.高频时钟线需要蛇形走线2.有些信号线需要设置差分对,差分走线

2019-05-31 06:23:05

`各位大佬,ORCAD PCB (16.3~16.6)在设计PCB时候,需要画差分线和差分的等长要求,请教各位如何设置;谢谢!`

2018-04-14 09:54:03

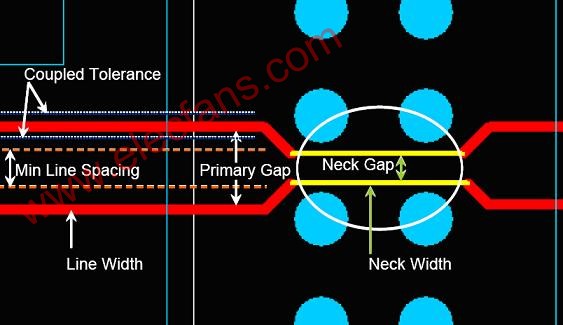

Properties,如下图所示。(3)在弹出的对话框中,可设置相应的线宽及线距,此处分别设置为8与6(8:8:6)。点击OK,即完成差分对的定义。线宽及线距影响差分线的阻抗,其值可由Polar

2015-01-12 15:38:59

差分信号在高速电路设计中应用越来越广泛,如USB、HDMI、PCI、DDR*等,承载差分信号的差分线主要优势有:抗干扰能力强,能有效抑制EMI、时序定位精确等,对于PCB工程师来说,最关注的是如何确保在实际走线中能完全发挥差分线的这些优势。

2019-05-20 09:32:55

RT,按F3 交互布线时 差分只出了一端,不知道是什么地方设置的问题,从网络的另一端可以。正常的差分交互布线时两个差分线应该能同时引出来,但是有个芯片就是不行,只能引出一根。别的板子上同样的芯片是可以的,差分设计规则也设成了同样的。求教还有其他的地方设置不合理会导致这种现象的出现么?

2013-11-19 22:43:05

按F3 交互布线时 差分只出了一端,不知道是什么地方设置的问题,从网络的另一端可以。正常的差分交互布线时两个差分线应该能同时引出来,但是有个芯片就是不行,只能引出一根。别的板子上同样的芯片是可以的,差分设计规则也设成了同样的。求教还有其他的地方设置不合理会导致这种现象的出现么?

2019-04-07 21:33:41

1234是四对差分线,其中1是clock,234是信号对,那么这四对差分线总长不一样可以吗?

2018-08-10 08:44:43

PCB设计中差分线怎么设置,还有就是等长分析

2019-08-19 09:47:36

请教大家,一下PCI-E和BGA之间的差分线因到BGA时长度不一致,需要走蛇形线.但蛇形线又走的太长,相当与整个长度的一半了,该怎样走好一些呢?

2009-04-10 22:01:48

USB通讯是差分传输,那可以像485那样,只用两个差分线传输吗?

2022-03-20 11:05:08

1、先用鼠标选中要调整的差分线,选中后线的颜色会有变化 2、再点击图示左边的快捷按钮,此时会弹出相关的调整选项,选好你需要的选项 3、鼠标放在刚才选中的线上拉出一个方框,方框内就会显示线

2020-09-03 17:54:04

` 本帖最后由 cooldog123pp 于 2019-8-10 22:50 编辑

差分线,布线的时候经常会遇到,在AD里面,怎么进入布差分线的模式中呢。快捷键组合p+i,或者点击菜单Place

2016-09-26 17:11:37

本帖最后由 cooldog123pp 于 2019-8-10 22:49 编辑

设置差分对,有好几种方法,下面我就来一一介绍方法一:原理图中直接设置好,然后导入到PCB中,如图,给要设置的差

2016-09-27 09:19:50

Pairs Editor”,进入差分对编辑器,如图10-6所示,可以看到这里总共有3个差分类。① All Differential Pairs:默认包含了PCB上所设置的所有差分线。② 90OM:刚才在

2021-03-29 15:12:01

各位,为什么不同层差分线的间距不一样啊?

2019-09-06 05:36:01

为什么我看到被人的样板为什么高频差分线不包地这是为什么

2015-01-07 09:45:00

介绍反向偏置差分线性传感器的主要应用是测量轴和轴向位移等线性运动,本文以Allegro ATS344LSP 反向偏置差分线性传感器 IC为例介绍了其传感原理,其磁性配置的优点,并给出了典型的用户

2020-07-30 09:41:49

什么是差分线差分线有什么用哪些地方用到差分线高速差分线设计的硬件要求

2021-02-25 06:26:18

老师,这个差分线走到一半怎样单独走线呢?

2019-09-19 22:58:05

差分对组距之间。差分组与差分组之间的间距。差分线与其它信号之间的间距如何设置

2019-09-10 22:57:20

请问这种交叉的差分线如何处理

2019-09-17 05:35:54

差分信号在高速电路设计中应用越来越广泛,如USB、HDMI、PCI、DDR*等,承载差分信号的差分线主要优势有:抗干扰能力强,能有效抑制EMI、时序定位精确等,对于PCB工程师来说,最关注的是如何确保在实际走线中能完全发挥差分线的这些优势。

2019-05-24 06:32:02

记得以前设计过一块多层板,电路上有一个屏,是用几对差分线驱动的。调试硬件的时候,系统能正常跑起来,但是屏点不亮。后来经过排查,发现有一对差分线用错了,这个方案有四路差分线模式和两路差分线模式,本项

2022-02-18 09:48:47

allegro中内差分怎么单独绕?

2019-07-18 05:35:18

图中左边是差分线,右边也是差分线。求教这两端差分线号S1和S2是什么关系?这个是电平转换吗?求教

2015-01-28 14:30:42

在AD中,差分线等长知道用TOOLS/Interactive Length Tuning操作,表现出来差分中一条线作蛇形线。请教下:1.如何让两条线都作蛇形线??2.不同组别的差分线要等长?这两个要求有会的吗?急!!

2015-07-10 12:32:41

①在元件布局(PCB Layout)时,应将USB2.O芯片放置在离地层最近的信号层,并尽量靠近USB插座,缩短差分线走线距离。②差分线上不应加磁珠或者电容等滤波措施,否则会严重影响差分线的阻抗。

2019-05-23 08:54:17

编译差分线时出现错误怎么办?错误:number of nets in differential parts EXT_CS_DPN is 1 instead of 2

2015-04-30 09:50:28

请教各位大神, allegro 差分对与差分对之间的间距如何设置?谢谢! 版本16.6。我在网上看到可以在class to class中设置,尝试后发现需要为每一对差分对设置一个NetClass属性

2017-02-24 14:21:34

差分线何时要考虑线的等长?如果要考虑使用等长线的话,两根信号线之间的长度之差最大不能超过多少?如何计算?

2019-05-20 05:35:12

请教大家一个问题。 芯片采用的差分线传输数字数据,芯片输出一共有10对LVDS差分走线,两对时钟,8对数据线。截图是芯片手册中提到的内容。 问题1:它是说明每一对之间相差长度吗?我举例解释一下

2019-01-04 10:00:40

差分线拐这么多次对信号影响大吗????

2019-06-12 21:19:07

差分线组内等长 命令是哪个?

2019-07-26 05:35:14

我的图中是一对差分线,不过走线过程中得放置过孔,使用了快捷键shift+ctrl+滚轮放置过孔换层,测的两个过孔之间间距30多mil,请问放置这两个过孔时的间距可以设置吗,再不改变过孔大小的情况下。

2019-09-25 02:48:42

求助dxp2004中如何布50欧姆的差分线,还有一些布线规则都怎么设置

2020-03-13 04:22:20

DS90UB913Q-Q1和DS90UB914Q-Q1采用STP的方式始终调不通,差分LVDS信号从913上出来后串了0.1uf的电容,然后进入914,这种连接方式是否正确,再LVDS差分线是是否要串上100Ω的电阻?谢谢!

2019-06-19 08:08:08

封装上12号和1号引脚离得比较远 ,这样怎么画差分线啊?

2019-04-24 06:22:15

差分对应该是推一根线,另一根线应该跟着推才是,可是现在这个选项没有勾,为什么起不到这个作用

2019-05-28 02:49:17

焊盘间距比差分规则的间距大,差分线走不出来,怎么办?

2019-09-10 23:04:40

走差分线可以设置等长吗

2019-07-31 05:35:12

我想知道连接CPU的控制信号要用等长线?哪些控制信号要布差分线?知道10G是什么概念吗?波导级!

2023-04-07 17:41:11

差分线对的工作原理是使接收到的信号等于两个互补并且彼此互为参考的信号之间的差值,因此可以极大地降低信号的电气噪声效应。而单端信号的工作原理是接收信号等于信号与电源或地之间的差值 ,因此信号或电源

2018-09-04 16:31:34

上一期我们介绍了高速PCB设计软件allegro16.6差分信号的设定在高速PCB布线前需要对差分信号的规则进行设置因此本期重点介绍在电气规则和物理规则下是如何建立差分信号的规则1、在电气规则下建立

2017-01-06 09:46:41

allegro16.2过孔设置方法.图解教程。

2010-03-18 15:06:38 0

0 allegro规则设置里常见缩写词的含义,Dsn Design整个设计

2011-11-22 10:51:53 5136

5136 allegro pcb editor在规则设置之前,必须了解allegro pcb editor规则设置类别优先顺序,

2011-11-22 10:53:16 5429

5429

本内容介绍了Allegro中尺寸标注文字的设置,这里我们介绍文字参数的设置。

2012-06-26 15:03:51 6046

6046

Allegro中尺寸标注有很强大的功能,包括线性标注,角度标注,引线标注等。下面介绍一下Allegro中尺寸标注参数的设置

2012-06-26 15:09:10 17869

17869

allegro_差分线等长设置,有需要的下来看看

2016-02-22 16:15:35 62

62 allegro16.2过孔设置方法,有需要的下来看看。

2016-02-22 16:21:27 11

11 本文档的主要内容详细介绍的是AD中关于差分线的设置和走线的方法详细资料说明。

2019-02-11 08:00:00 0

0 DDR4布线之allegro约束规则设置综述

2021-09-08 10:34:29 0

0 ALLEGRO约束规则设置步骤(以DDR为例)

2022-12-30 09:19:29 10

10

电子发烧友App

电子发烧友App

评论