弥补此不足。这也是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一(在vcc引脚上通常并联一个去藕电容,这样交流分量就从这个电容接地。)1.2有源器件在开关时产生的高频开关噪声将沿电源线传播。

2019-08-26 09:41:50

PCB PDN design guidelines (PCB电源完整性设计指导) ------PCB平面图指南一、 不带电源平面1.为每个有源设备至少提供一个“本地”去耦电容器,并为板上分布的每个

2021-12-28 06:07:45

什么是PCB中的板级去耦呢?如何设计板级去耦。

2021-01-22 06:28:39

可以说现在电路板有很多颜色,不仅有经常见到的绿色,还有黑色、白色、红色、蓝色等。但是绿色用的最多的,也用有一定的历史年限了的,现在的流通市面见得最多的PCB板,其实开始用绿色PCB主要是由于制造工艺

2019-06-27 04:20:11

的电路板维修都没有图纸材料,因此很多人对电路板维修持怀疑态度,虽然各种电路板千差万别,但是不变的是每种电路板都是由各种集成块、电阻、电容及 其它器件构成的,所以电路板损坏一定是其中某个或某些个器件损坏造成

2018-04-18 10:44:17

(如:晶振或钟振)要尽量靠近用到该时钟的器件; ⑥. 在每个集成电路的电源输入脚和地之间,需加一个去耦电容(一般采用高频性能好的独石电容);电路板空间较密时,也可在几个集成电路周围加一个钽电容

2018-01-23 09:59:41

PCB电路板上,大大小小的元器件们各执其责,任何一个器件出现问题都会导致整个电路板出错!所以我们有必要了解电路板上这些器件容易犯错的具体情况,才能在出错时候第一时间去应对问题!

2020-11-02 07:08:02

) 尽量在关键元件,如ROM、RAM等芯片旁边安装去耦电容。实际上,印制电路板走线、引脚连线和接线等都可能含有较大的电感效应。大的电感可能会在Vcc走线上引起严重的开关噪声尖峰。防止Vcc走线上开关噪声

2018-09-11 16:05:35

PCB电路板是对零散的电子元件进行组合,可以保证电路设计的规则性,并很好的避免人工排线与接线容易造成的混乱及错误问题。PCB电路板的设计是电路板生产制造的基础,下面我们来看看PCB电路板的设计流程

2019-04-15 07:35:02

面(在电路板组装后)。在电路板上下表面充分应用丝网印刷技术能够减少重复工作并精简生产过程。9、必选去耦电容。不要试图通过避免解耦电源线并依据元件数据表中的极限值优化你的设计。电容器价格低廉且坚固耐用

2019-03-12 09:17:05

PCB制版之--PCB电路板相关操作1.板层、工作层面、原点相关前期设置板层设置 Design——Layer stack manager 图层堆栈管理器——默认条件下是二层板(two layer

2014-12-24 11:27:26

PCB单面电路板指的是在最基本的PCB上,零件集中在其中一面,导线则集中在另一面上,导线只出现在其中一面的意思。因为PCB单面电路板在设计线路上有许多严格的限制(因为只有一面,布线间不能交*而必须绕独自的路径。

2019-09-23 09:00:33

2.4厘米。不同的电容,谐振频率不同,去耦半径也不同。对于大电容,因为其谐振频率很低,对应的波长非常长,因而去耦半径很大,这也是为什么我们不太关注大电容在电路板上放置位置的原因。对于小电容,因去耦半径很小,应尽可能的靠近需要去耦的芯片,这正是大多数资料上都会反复强调的,小电容要尽可能近的靠近芯片放置。

2018-08-28 14:41:28

1.6nH,那么其安装后的谐振频率为125.8MHz,谐振周期为7.95ps。假设信号在电路板上的传播速度为166ps/inch,则波长为47.9英寸。电容去耦半径为47.9/50=0.958英寸,大约

2018-09-12 10:46:08

有时我们会忽略使用去耦的目的,仅仅在电路板上分散大小不同的许多电容,使较低阻抗电源连接到地。但问题依旧:需要多少电容?许多相关文献表明,必须使用大小不同的许多电容来降低功率传输系统(PDS)的阻抗

2020-11-18 09:18:02

有时我们会忽略使用去耦的目的,仅仅在电路板上分散大小不同的许多电容,使较低阻抗电源连接到地。但问题依旧:需要多少电容?许多相关文献表明,必须使用大小不同的许多电容来降低功率传输系统(PDS)的阻抗

2022-05-07 11:30:38

在电路设计过程中,应用工程师往往会忽视印刷电路板(PCB)的布局。通常遇到的问题是,电路的原理图是正确的,但并不起作用,或仅以低性能运行。在本篇文章中,牛人工程师将跟大家介绍如何正确地布设运算放大器

2021-03-28 07:00:00

在电路设计过程中,应用工程师往往会忽视印刷电路板(PCB)的布局。通常遇到的问题是,电路的原理图是正确的,但并不起作用,或仅以低性能运行。在本篇文章中,牛人工程师将跟大家介绍如何正确地布设运算放大器

2022-08-03 14:33:47

之一上放置尽可能多的高速IC(让我们说它是顶部)。布置电源和接地层,使它们相邻并靠近顶层。将所有去耦帽放在顶层,使它们与平面有短连接。 通过分离减少通孔分离的第一种方法是使用较小的去耦电容。在我的电路板

2018-07-27 11:59:50

对于电容的安装,首先要提到的就是安装距离。容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置。容值稍大些的可以距离稍远,最外层放置容值最大的。但是,所有对该芯片去耦的电容都尽量

2018-09-18 15:56:26

2.4厘米。不同的电容,谐振频率不同,去耦半径也不同。对于大电容,因为其谐振频率很低,对应的波长非常长,因而去耦半径很大,这也是为什么我们不太关注大电容在电路板上放置位置的原因。对于小电容,因去耦半径很小,应尽可能的靠近需要去耦的芯片,这正是大多数资料上都会反复强调的,小电容要尽可能近的靠近芯片放置。

2018-09-17 17:40:22

PCB抗干扰设计,电源线、地线、去耦电容如何配置?

2021-03-17 07:04:11

(库仑)与它的电位V(伏特,相对于大地)成正比,即有, 所以C就是该导体的PCB设计之电容量。PCB设计之电容的单位是法拉(F)。在两块平行的金属板之间插入绝缘介质,且引出电极就成为了PCB设计之电容

2019-08-13 10:49:30

电容在集成电路电源和地之间的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声。数字电路中典型的去耦电容值是 0.1μF。这个电容的分布电感的典型值是 5μH。0.1μF 的去耦

2011-02-24 14:30:32

在直流电源回路中,负载的变化会引起电源噪声。例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。配置去耦电容可以抑制因负载变化而产生

2014-11-19 11:26:03

。对于小电容,因去耦半径很小,应尽可能的靠近需要去耦的芯片,这正是大多数资料上都会反复强调的,小电容要尽可能近的靠近芯片放置。 PCB布局时去耦电容摆放技巧与安装 尖峰电流的抑制方法 1、在电路板

2023-04-11 16:26:00

` 本帖最后由 eehome 于 2013-1-5 10:08 编辑

去耦电容和旁路电容的区别`

2012-08-14 11:49:42

信号完整性之去耦电容与旁路电容

2019-11-19 14:52:05

去耦电容分为哪几种?如何去放置去耦电容呢?在设计中如何防止上电及正常工作时出现总线冲突呢?

2021-11-03 07:17:04

个局部的直流电源给有源器件,以减少开关噪声在板上的传播和将噪声引导到地。 摘引自伦德全《电路板级的电磁兼容设计》一文,该论文对噪声耦和路径、去耦电容和旁路电容的使用都讲得不错。请参阅。 从电路来说

2012-03-08 23:42:09

电子线路中的同一个电容,有时候会称它去耦电容,有时候又会称它为旁路电容。 电子电路中,去耦电容和旁路电容都是起到抗干扰的作用,但是,当我们从不同的角度去看时,它所起的作用是不同的,所以才有

2021-05-25 06:14:19

器(C1 和C2)情况下用于驱动 R-C 负载的缓冲电路。我们注意到,在不使用去耦电容器的情况下,电路的输出信号包含高频 (3.8MHz) 振荡。对于没有去耦电容器的放大器而言,通常会出现稳定性低、瞬态响应

2018-09-20 15:44:35

在担任应用工程师之前,我是 IC 测试开发工程师。我的项目之一是对 I2C 温度传感器进行特性描述。在编写一些软件之后,我手工焊接了一个原型设计电路板。由于时间仓促,我省去了比较麻烦的去耦电容

2018-12-26 14:19:56

去耦电容在PCB板设计中的应用在板设计中应充分考虑电磁兼容方面的问题,合理地使用去耦电容在PCB板防止电磁干扰中具有重要作用, 本文就去耦电容的容量及其具体应用作了较为全面、详细的叙述,同时还介绍了增强去耦电容效果的一些实用方法。[hide][/hide]

2009-12-09 14:08:29

去耦电容的有效使用方法之一是用多个(而非1个)电容进行去耦。使用多个电容时,使用相同容值的电容时和交织使用不同容值的电容时,效果是不同的。

2019-08-02 06:56:29

。假设信号在电路板上的传播速度为 166ps/inch,则波长为 47.9 英寸。电容去耦半径为 47.9/50=0.958英寸,大约等于 2.4 厘米。本例中的电容只能对它周围 2.4 厘米范围内

2015-08-26 21:56:00

)也应该连在G上。一个双电源运放电路会有另外对于负电源的去耦电容,同样应该连在G上。有一个方案可以建立一个具有上述节点G接地特性的电路板。规则很简单——输入端的地到电阻R1的线路应该是一条干净的路径

2018-09-20 16:31:25

在高速时钟电路中,尤其要注意元件的RF去耦问题。究其原因,主要是因为元件会把一部分能量耦合到电源/地系统之中。这些能量以共模或差模RF的形式传播到其他部件中。陶瓷片电容需要比时钟电路要求的自激

2018-11-27 15:19:23

一个原型设计电路板省去了比较麻烦的去耦电容器;但获得的任何结果都无法与预期结果相匹配。最后,添加一个去耦电容器,问题解决了。什么我们需要使用去耦电容器?它的作用到底是什么?

2021-04-02 07:46:38

在做高速电路设计的时候,为什么要有那么多去耦电容?到底什么是去耦?到底需要多大的去耦电容呢?为什么是很多个小电容并联而不是用一个大电容(值是一样大的啊)?为什么说小电容要靠近电源管脚而大电容可以

2019-05-07 06:22:23

因为电容器的基本功能是储存电荷,所以理想的去耦电容器可以提供逻辑装置进行状态变换时所需的所有电流。 其中,ΔI为转换电流;ΔV为允许供电电压的改变(波动);ΔT为切换时间。 例:如果设计中允

2018-11-23 16:00:55

去耦旁路电路,不同规格的电容在PCB布局时该怎么摆

2021-03-17 07:33:04

,只是在电路上的位置不同而已。 旁路一般位于信号输入端,去耦一般位于信号输出端。 所以旁路电容滤除的是前级电源的干扰,一般是滤除高频噪声,在输入电源管脚上加小容值电容,一般是0.1uF

2021-01-11 16:31:51

对于已经知道了电容的具体特性和适用范围,以及去耦原理,那么就知道了去耦的具体方法了吗?不是的,下面我们将讲解一下,具体安装到电路板上之后的去耦原理以及具体如何防止电容的准则!

2021-03-04 08:11:41

一块电路板上形成电容当高阻抗模拟走线贴近数字走线时,种电容可能会在敏感的混合讯号电路中造成问题。例如 (图二)中的电路就可能会面临这类问题。注:以三个8位数字电位计和三个运算放大器组成之输出电压达 6万

2016-01-22 14:45:45

) 考虑pcb板在机箱中的位置和方向; (6) 缩短高频元器件之间的引线。 4、去耦电容的配置 (1) 每10个集成电路要增加一片充放电电容(10uf); (2) 引线式电容用于低频,贴片式电容

2018-09-20 11:12:35

电路板级的EMC设计(3) PCB布线技术文章目录电路板级的EMC设计(3) PCB布线技术文档简介第三部分:印制电路板的布线技术1.PCB基本特性2.分割3.局部电源和IC间的去耦4.基准面的射频

2021-11-12 08:43:48

现在在画一个ColdFire54455的板子,DDR2去耦电容这里有几个不明白的问题,还望大家不吝赐教,万分感激。DDR2我用的是MT47H32M16,官方Demo原理图用的MT47H64M8,用了

2016-12-13 09:34:14

`各位大神,请问FPGA去耦电容如何布局、布线?1.根据文档,一般去耦电容的数量都少于电源引脚,那么去耦电容要放到哪些管脚旁边呢?2.以下三种方案哪种好?2.1电容放在PCB top层FPGA外围

2017-08-22 14:57:10

想为cyclone V 系列的5CEFA7F27这款FPGA设计去耦电容电路,但是不知道该如何下手。参考了altera公司的一块开发板,给出的FPGA的去耦电容电路如下所示,但是感觉这个去耦电容电路

2016-07-09 10:11:21

其内部电源干扰会导致器件工作不连续,原因是内部节点未获得正确的偏置。 PCB板中去耦电容的分类去耦电容在补偿集成片或电路板工作电压跌落时能起到储能作用。它可以分成整体的、局部的和板间的三种。整体去耦电容又称旁路电容,它工作于低频(

2019-05-15 04:24:21

耦合。Decoupling,即是减弱耦合的意思。因此, 去耦电容是在电路中发挥去耦作用的电容。我们经常提到像去耦、耦合、滤波等说法,是从电容器在电路中所发挥的具体功能的角度去称呼的,这些称呼属于同一个

2022-11-04 22:29:20

射频(RF)电路板设计虽然在理论上还有很多不确定性,但RF电路板设计还是有许多可以遵循的法则。不过,在实际设计时,真正实用的技巧是当这些法则因各种限制而无法实施时,如何对它们进行折衷处理,本文将集中

2023-05-30 11:18:42

对其他敏感模拟电路模块如ADC造成干扰。大多数问题发生在较低的工作频段(如27MHz)以及高的功率输出水平。用RF去耦电容(100pF)连接到地来去耦敏感点是一个好的设计习惯。(7)在板环形天线的特别考虑

2018-12-27 23:02:26

什么是PCB中的板级去耦呢?如何设计板级去耦?

2021-01-25 06:33:18

引起如电源电压下跌、电路板接插件打火、电路板内电压上升慢等问题。PCB布局时去耦电容摆放对于电容的安装,首先要提到的就是安装距离。容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置

2016-08-27 11:11:57

集成电路电源和地之间的去耦电容的作用是什么?印刷电路板的抗干扰设计原则有哪些?

2021-07-11 07:54:53

方式干扰形成的三个基本方式: 干扰源、耦合途径、敏感源。下面分别从这几个方面进行阐述。2.1 PCB电路板干扰耦合途径PCB 电路板上干扰主要有共模干扰和差模干扰。差模干扰是由信号回路产生的,共模干扰是由

2011-07-16 11:50:08

`请问医疗PCB电路板与普通PCB板的区别有哪些?`

2020-03-27 15:18:37

、去耦电容的引线不能太长,尤其是高频旁路电容不能带引线。四 器件配置:1、时钟发生器、晶振和CPU的时钟输入端应尽量靠近且远离其它低频器件。2、小电流电路和大电流电路尽量远离逻辑电路。3、印制板在机箱中

2012-09-06 11:25:33

通过遵循一些在PCB布局中放置去耦电容器的准则,了解如何减少二次谐波失真。 在上一篇文章中,我们讨论了需要对称的PCB布局以减少二次谐波失真。 在本文中,我们将看到,如果没有适当的去耦,我们

2023-04-21 15:24:03

中,去耦电容存储电荷并将电荷输送给IC,以补偿由半导体开关动作产生的瞬态干扰。在低工作频率下,电容器有足够的时间放电,然后再充电,直到IC需要另一次电流突发。但是,随着频率的增加,电路板设计者必须

2023-04-14 16:51:15

的影响。形成悬浮地或是悬浮电源,在复杂的系统中完成各部分地线或是电源的协调匹配,有源器件在开关时产生的高频开关噪声将沿着电源线传播。去耦电容的主要功能就是提供一个局部的直流电源给有源器件,以减少开关噪声在

2020-12-02 09:34:28

在电路设计过程中,应用工程师往往会忽视印刷电路板(PCB)的布局。通常遇到的问题是,电路的原理图是正确的,但并不起作用,或仅以低性能运行。在本篇博文中,我将向您介绍如何正确地布设运算放大器的电路板以

2019-07-31 04:45:01

抄板也叫克隆或仿制,是对设计出来的PCB板进行反向技术研究;目前全新的定义:从狭义上来说,抄板仅指对电子产品电路板PCB文件的提取还原和利用文件进行电路板克隆的过程;从广义上来说,抄板不仅包括

2021-07-19 07:45:34

会非常大,会导致器件在需要电流的时候,不能被及时供给。而去耦电容可以弥补此不足。这也是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一(在vcc引脚上通常并联一个去藕电容,这样交流分量就从

2012-02-10 17:10:05

, John。“高速印刷电路板布局实用指南”。《模拟对话》39-09,2005年9月。指南MT-100,试验板和原型制作技术。ADI公司,2009年。指南MT-101,去耦技术。ADI公司,2009年

2018-10-19 10:49:11

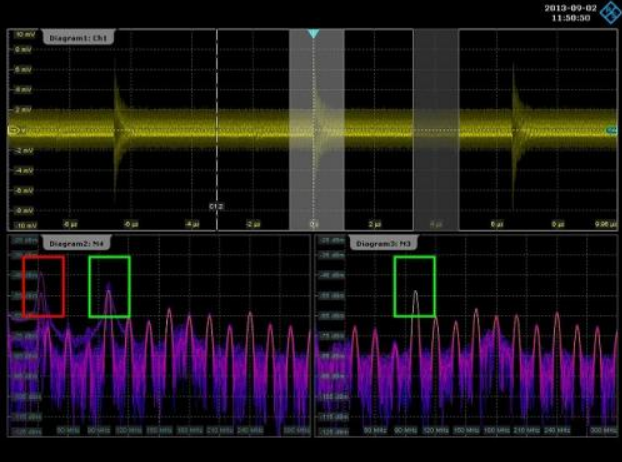

均是利用评估板获得。左侧曲线显示正确去耦的响应,右侧曲线显示同一电路板上去除去耦电容后的响应。两种情况中,输出负载均为100 Ω。示波器图说明,没有去耦时,输出表现出不良响铃振荡,这主要是因为电源电压

2018-10-19 10:58:00

一段距离,即便距离不长,在频率很高的情况下,阻抗Z=i*wL+R,线路的电感影响也会非常大,会导致器件在需要电流的时候,不能被及时供给。而去耦电容可以弥补此不足。这也是为什么很多电路板在高频器件VCC管脚处

2018-12-07 09:39:59

电路板时,通常会在负载芯片周围放置很多电容,这些电容就起到电源退耦作用。其原理可用图1说明。图1 去耦电路当负载电流不变时,其电流由稳压电源部分提供,即图中的I0,方向如图所示。此时电容两端电压与负载

2013-03-08 16:33:18

是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一(在Vcc引脚上通常并联一个去耦电容,这样交流分量就从这个电容接地。(2)有源器件在开关时产生的高频开关噪声将沿着电源线传播。去耦电容的主要功能就是

2018-02-05 15:13:14

耦电容可以弥补此不足。这也是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一(在vcc引脚上通常并联一个去藕电容,这样交流分量就从这个电容接地。) 2)有源器件在开关时产生的高频开关噪声将

2019-01-02 15:31:11

电容可以弥补此不足。这也是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一(在 VCC引脚上通常并联一个去耦电容,这样交流分量就从这个电容接地)。2)有源器件在开关时产生的高频开关噪声将沿着

2012-04-04 23:29:40

偶电容可以抑制因负载变化而产生的噪声,是印制电路板的可靠性设计的一种常规做法。配置规则:电源输入端跨接一个10~100uf 的电解电容,如果印制电路板位置允许,采用100uf以上的电解电容抗干扰...

2021-12-31 08:05:14

瓷片电容、钽电容、电解电容区别---电源设计中的去耦电容应用实例转自:张飞实战电子电源往往是我们在电路设计过程中最容易忽略的环节。其实,作为一款优秀的设计,电源设计应当是很重要的,它很大程度影响了

2021-11-11 08:12:14

。假设信号在电路板上的传播速度为166ps/inch,则波长为47.9英寸。电容去耦半径为47.9/50=0.958英寸,大约等于2.4厘米。 本例中的电容只能对它周围2.4厘米范围内的电源噪声进行

2019-09-06 18:13:24

用钽电容或聚碳酸酯电容。 去耦电容的选用并不严格,可按C=1/F,即10MHz取0.1μF,100MHz取0.01μF。 分布电容是指由非形态电容形成的一种分布参数。一般是指在印制板或其他形态的电路形式

2017-05-04 10:48:07

的低阻抗路径。图4所示为我们的最终布局。[img=600,0][/img]图4:最终布局下一次当您布设印刷电路板时,务必遵循以下布设惯例:尽量缩短倒相引脚的连接。让去耦电容器尽量靠近电源引脚。如果使用了

2018-08-09 18:09:44

; 高速电路板上使用最多的是什么东西? 去耦电容!&

2009-03-27 14:55:46

什么是传输线效应?高速DSPs的PCB电路板该怎样去设计?

2021-04-25 06:27:07

我司定制生产各种柔性FPC电路板,硬性PCB电路板,单层电路板,多层电路板,双层电路板,刚柔一体电路板等。 打样周期7天左右,批量生产周期15天内。 主要应用于手机,便携计算机

2022-09-20 18:11:35

不论是PCB喷码机、FPC喷码机、电路板喷码机,我们都曾经听过很多,特别是电路板行业内的厂家、制造商企业,很多都开端应用油墨打码或激光打标来替代人工,俭省人力本钱和进步效率,今天潜利就和大家分享一下

2023-07-07 16:34:27

不论是PCB喷码机、FPC喷码机、电路板喷码机,我们都曾经听过很多,特别是电路板行业内的厂家、制造商企业,很多都开端应用油墨打码或激光打标来替代人工,俭省人力本钱和进步效率,今天潜利就和大家分享一下

2023-08-17 14:35:11

接触式印刷方法将油墨涂到印刷电路板表面。它们可以快速有效地创建高分辨率标记,但与激光打标机相比,由于使用油墨,可能需要更多的维护。 机械雕刻机:机械雕刻机

2023-08-18 10:05:35

PCB线路板溯源镭雕机,电路板追溯码机,简易溯源码镭雕机,激光打码机,涂层打码机,溯源标识机,PCB溯源码制作流程,激光打码机怎样调试性能特征 维品科技适用于

2023-09-18 21:16:16

切片分析技术在电子元器件行业中是最常见的也是重要的分析方法之一,通常被用作品质判定和品质异常分析、检验PCB电路板、电容品质的好坏、电容电阻质量检测、寻找失效的原因与解决方案、评估制程改进,做为客观

2021-04-28 11:39:56 2682

2682

电子发烧友App

电子发烧友App

评论