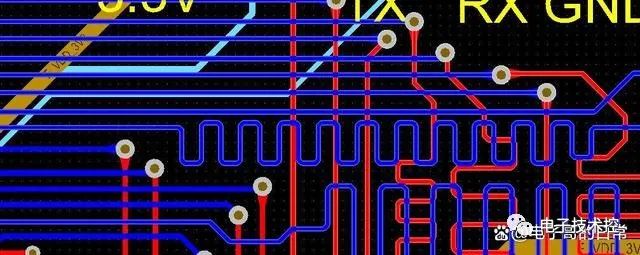

下面从直角走线、差分走线、蛇形线三个方面来阐述PCB LAYOUT的走线。

2021-03-17 07:25:46

本帖最后由 maskmyself 于 2017-7-10 10:08 编辑

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速

2017-07-07 11:45:56

PCB Layout中的走线策略

2012-08-04 16:32:25

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2014-08-13 15:44:05

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-08-05 06:40:24

新人,求PCB布局走线资料,谢谢!

2014-08-02 19:19:40

PCB中走线有几种这几种分别有什么作用?哪种对信号的影响最好?

2012-11-13 15:49:21

我们通常需要快速地估计出印刷电路板上一根走线或一个平面的电阻值,而不是进行冗繁的计算。虽然现在已有可用的印刷电路板布局与信号完整性计算程序,可以精确地计算出走线的电阻,但在设计过程中,我们有时候还是希望采取快速粗略的估计方式。

2019-09-11 11:52:28

pcb走线时,会影响到已经布完的线。之前正在布的线不会对已经布完的线产生影响,现在不知道怎么恢复。

2019-09-25 03:58:46

PCB走线宽度、电流关系计算工具:PCB走线宽度、电流关系计算工具.zip (850.77 KB )

2019-10-09 01:16:38

1. 一般规则 1.1 PCB板上预划分数字、模拟、DAA信号布线区域。 1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。 1.3 高速数字信号走线尽量短。 1.4

2018-11-28 17:06:35

PCB走线电流计算工具

2021-03-12 13:36:29

好的图像质量的保证。 PCB走线如果可能的话,信号走线使用6mil, 走线间距使用6mil. 放置0.1uF的退耦电容在对应的DSP电源脚上,并尽可能的靠近。它的走线尽可能的粗。电源正极的走线最少要

2023-04-13 16:09:54

求高手贡献PCB设计走线经验!及相关技术

2013-01-11 20:02:07

1.PCB走线线宽的重要性 PCB载流能力的计算一直缺乏权威的技术方法、公式,经验丰富CAD工程师依靠个人经验能作出较准确的判断。但是对于CAD新手,不可谓遇上一道难题。 对于大电流电源走线

2023-04-12 16:02:23

`为什么下图中PCB走线正反面不同。孔与孔之间为直接通路。为什么背面的走线环绕迂回。小白菜提问,求高手详解。谢谢`

2018-10-29 08:46:46

经验公式来计算: C=61W(Er)1/2/Z0 在上式中,C就是指拐角的等效电容(单位:pF),W指走线的宽度(单位:inch),εr指介质的介电常数,Z0就是传输线的特征阻抗。举个例子,对于一个

2014-11-18 17:29:31

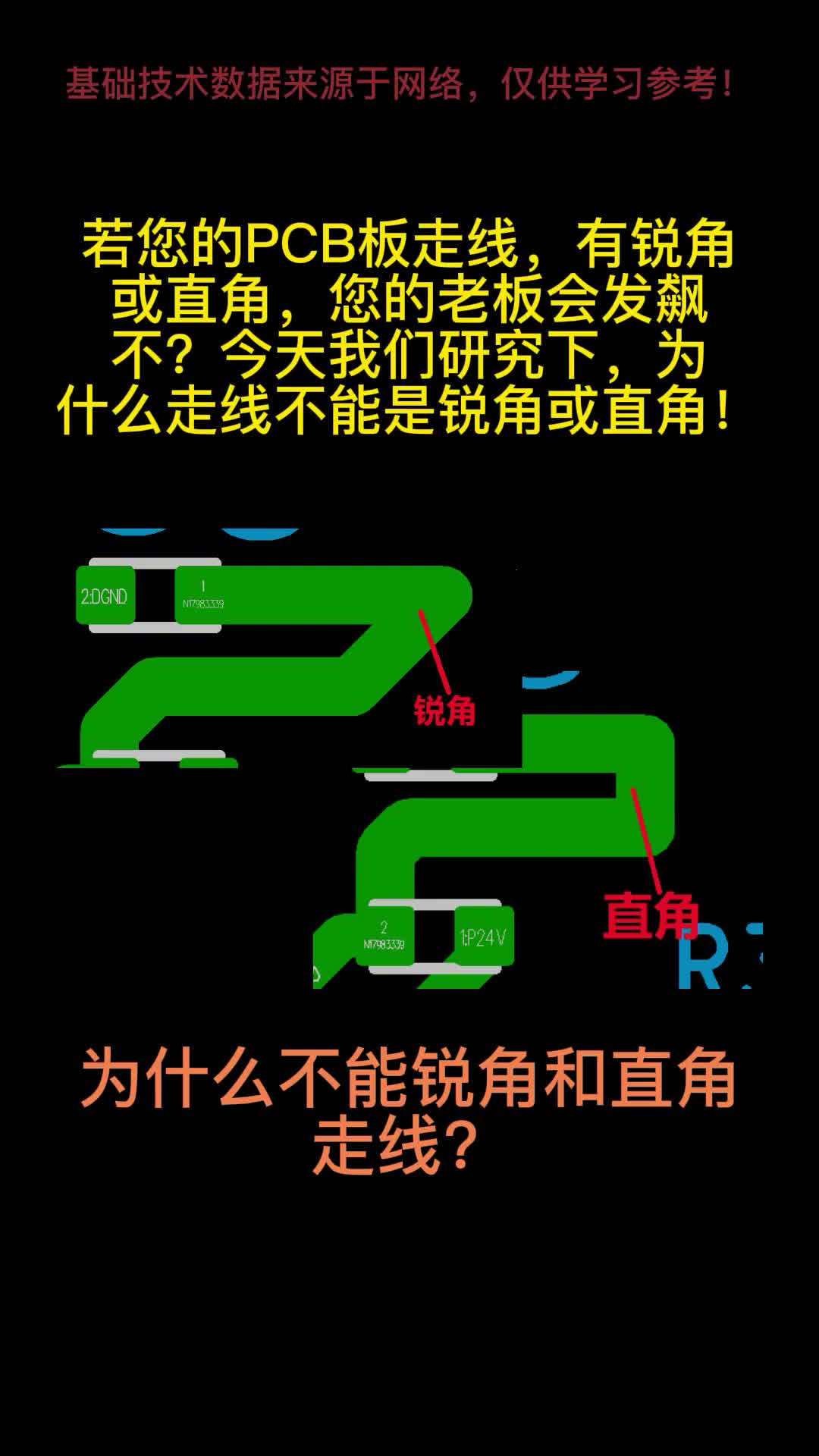

采访过苹果公司CEO的B站up主-何同学,近期更新一条视频中,有出现过他自己设计的PCB图。很多人说他不应该直角走线。PCB为什么不能直角走线呢?一般在高速信号线中,直角线会带来阻抗的不均匀

2022-09-08 16:54:17

`用altium 画PCB 对称电路时走线没有走对称,看起来有点别扭。像这种对称电路走线一般要怎么处理比较好呢?像我这样画对电器想能有没有什么影响?要怎么画才比较合理?希望大家指点指点`

2017-01-07 11:20:13

对角线之间的距离为78.74mil(4)计算线宽、间隙及过孔。若两个焊盘之间走一条线,两个焊盘之间平行布线区域为19.2910mil,考虑到余量计算采用17.2910mil进行。若线宽5mil,间隙

2020-07-06 15:58:12

经常听说“PCB走线间距大于等于3倍线宽时可以抑制70%的信号间干扰”,这就是3W原则,信号线之间的干扰被称为串扰。那么,你知道串扰是怎么形成的吗?当两条走线很近时,一条信号线上的信号可能会在另一

2022-12-27 20:33:40

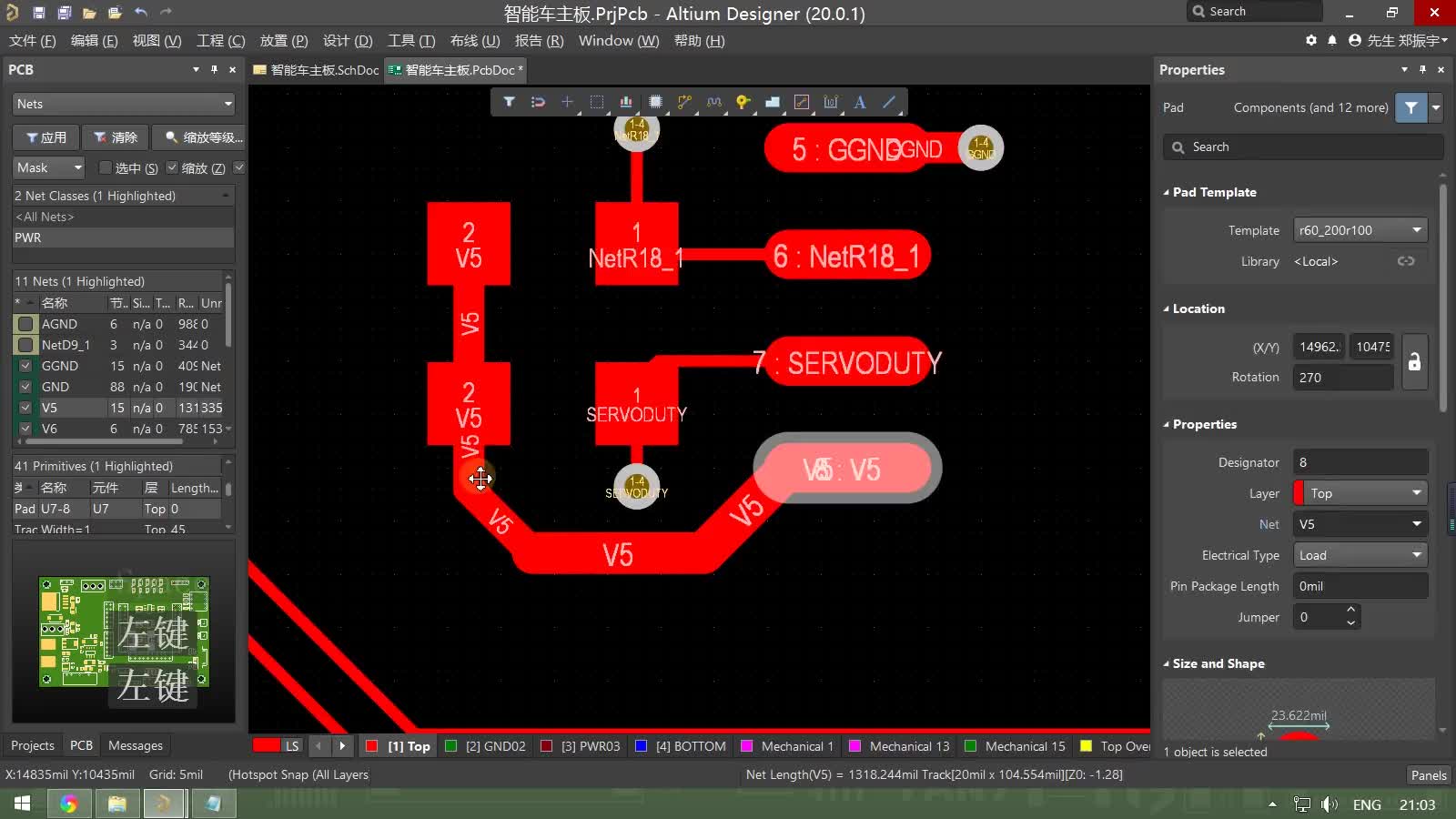

在pcb的设计过程中,元器件的布局和走线的调整是非常重要的一个步骤。恰当的布局可以简化布线的难度,更重要的是可以提高PCB的电气性能,减少EMC,EMI。 下面是同一个原理图对应的两种不同的布局和走

2019-10-17 04:37:54

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟

2017-11-22 20:04:14

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2018-08-30 10:14:44

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2020-07-14 18:02:17

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处?;最典型的就是

2018-09-20 11:05:23

PCB电容引脚之间可以走线吗?

2023-04-13 16:25:48

直角走线一般是pcb布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实

2014-10-28 15:08:55

1.1 PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。1.3 高速数字信号走线尽量短。1.4 敏感模拟信号走线尽量短。1.5

2019-05-30 06:58:19

PCB设计走线的宽度与最大允许电流有何关系?PCB设计走线的宽度与铜厚有何关系?

2021-10-11 09:49:14

PCB设计走线的规则是什么

2021-03-17 06:36:28

在高频电路中的数据线。没有计算蛇形线电感量的公式或经验值? 、specctra可以编程设定网络走线的阻抗匹配规则和差分线走线规则, 帮助里面讲了一些一般的设计原则,有时也兼作电阻作用。 实际是一个分布

2014-11-19 11:54:01

PCB能不能以锐角走线pcb layout能不能以90°走线

2021-02-26 08:14:21

1. 一般规则1.1 PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。1.3 高速数字信号走线尽量短。1.4 敏感模拟信号走线尽量

2014-03-14 17:44:44

pcb走线为什么直接连不到芯片引脚上呢?

2023-04-10 16:29:30

pcb走线线宽和电流的关系

2012-07-16 16:48:57

pcb布局,走线方面,有什么建议吗,该怎么怎么走,怎么提高效率

2016-10-15 14:51:34

;=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等

2019-05-22 02:48:05

`请问各路大神,从电阻内部走线会有什么影响?高频情况下有坏的影响?如果有影响的话,请详细、具体解释下。`

2015-11-06 15:38:25

请问大神,用这个打开PCB工程文件的时候鼠标所指的同一网络的走线不会高亮显示,这要怎么解决?

2017-08-27 10:42:29

PCB设计时,有时候需要在不增加PCB走线宽度的情况下提高该走线通过大电流的能力(载流能力),通常的方法是给该导线镀锡(或者上锡);下面以在PCB顶层走线镀锡为例,使用AD09软件,简单介绍如何走线上锡处理:1、 选择TopLayer层,确定需要走线的地方,画一条导线;(图文详解见附件)

2019-09-06 15:57:30

PCB设计:通常的BGA器件如何走线?

2021-02-26 06:13:16

PCB Layout中的走线策略布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见

2009-08-20 20:58:49

是至关重要的。下面将针对实际布线中可能遇到的一些情况,分析其合理性,并给出一些比较优化的走线策略。主要从直角走线,差分走线,蛇形线等三个方面来阐述。01直角走线直角走线一般是PCB布线中要求尽量避免

2018-07-08 13:28:36

cadence PCB 怎么取消走线?***用过,取消很容易,cadence没发现这个功能!

2016-01-25 22:57:46

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走线一侧是VCC,另一侧是GND,那么哪个是参考平面?要弄清楚这个问题,必须对了解传输线的概念。我们知道,必须使用传输线来分析

2014-11-17 10:07:29

会说:PCB走线怎么会那么奇形怪状?但是往往需要计算走线电阻的是电源信号,电源信号有时通过覆铜实现,形成一些不规则形状。总结如下:●六个为1的全正方形=6个等效方块;两个为0.14的连接器方块

2019-09-14 07:00:00

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-03-18 21:38:12

为什么PCB走线中不能出现锐角和直角?而且走线也不能和IC的PIN脚垂直?会影响到什么?

2023-04-11 16:31:28

是PCB布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,锐角、直角走线会使传输线的线宽发生变化,造成阻抗的不连续。线宽变化导致阻抗

2017-08-12 15:09:54

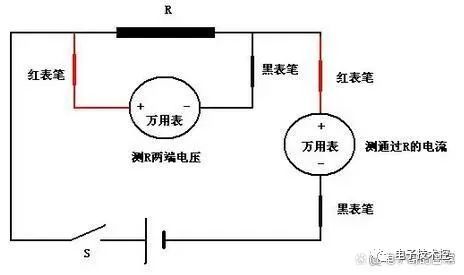

如何计算pcb走线上的电流大小?我电路板上的走线的特性阻抗为50,加了个33的限流电阻,芯片采用的3.3V电压,则走线的电路为3.3/(50+33) A吗?

2014-11-07 09:50:36

如何利用PCB走线设计一个0.05欧姆的采样电阻?

2021-02-03 07:10:52

AD里PCB多根走线时怎么改变线宽

2019-09-12 04:20:46

如何在altium designer 的PCB图里画出 粗细渐变的走线

2019-09-04 04:21:32

我们通常需要快速地估计出印刷电路板上一根走线或一个平面的电阻值,而不是进行冗繁的计算。虽然现在已有可用的印刷电路板布局与信号完整性计算程序,可以精确地计算出走线的电阻,但在设计过程中,我们有时候还是

2015-03-10 10:12:14

射频线PCB走线屏蔽孔,都有什么要求???求解

2016-01-13 14:40:40

做设计的都明白一个事情,很多时候需要的是一个估算值,印刷电路板也一样,通常需要很快的估算出PCB走线电阻的阻值,绕过那些繁杂的计算。本文就借着一个复杂的例子介绍一种快速估算出PCB走线电阻的方法

2019-05-26 08:30:00

PCB上面用更细的走线做保险有什么具体的公式算法,我有两种电流规格,一种是2A的持续电流,一种是0.1A的持续电流,如果用表层走线做保险丝,要用多宽的走线,铜厚1OZ

2019-08-21 21:45:15

怎样计算PCB布线中走线允许的最大长度?走线太长了都有哪些影响呢?

2023-04-10 17:10:25

宽,距电源/地越近,或隔离层的介电常数越高,特征阻抗就越小。 11、PCB板上的走线可等效为串联和并联的电容、电阻和电感结构。串联电阻的典型值0.25-0.55 ohms/英尺。并联电阻阻值通常很高

2014-12-16 09:47:09

如何控制PCB走线的直流电阻?

2019-07-19 14:32:04

电源布局、网口电路、音频走线的PCB设计

2021-03-04 06:10:24

Ω。 因此,从A到B的总电阻为3.98mΩ(3mΩ+0.14mΩ+0.84mΩ)。 有的朋友会说:PCB走线怎么会那么奇形怪状?但是往往需要计算走线电阻的是电源信号,电源信号有时通过覆铜实现,形成一些不规则

2019-10-02 08:00:00

A 到 B 的总电阻为 3.98mΩ(3mΩ+0.14mΩ+0.84mΩ)。 有的朋友会说:PCB 走线怎么会那么奇形怪状?但是往往需要计算走线电阻的是电源信号,电源信号有时通过覆铜实现,形成一些

2019-10-26 07:30:00

直角走线一般是pcb布线中要求尽量避免的情况,也几乎成为衡量布线好坏的标准之一,那么直角走线究竟会对信号传输产生多大的影响呢?从原理上说,直角走线会使传输线的线宽发生变化,造成阻抗的不连续。其实

2014-11-07 09:40:54

PCB走线线间距能不能走5mil?

2019-09-26 05:35:53

PCB长距离走线和短距离加个过孔走线哪种走线更合理?

2019-09-25 22:11:32

AD18 ,PCB,走线,任意走线,在哪里设置?

2019-03-07 01:36:59

HDMI差分对PCB怎么走线?要计算匹配阻抗吗?差分对走多长有要求吗?四对差分对要走一样长吗?

2019-05-31 05:35:21

TI人员你好:运放避免不了加反馈,在PCB Layout的时候,这个反馈回路的走线,最好的走线是怎样的?具体一点就是: 这条走线 是直接连接在芯片的输出端管脚的焊盘上? 还是 要与输出管脚有一定的距离,画在输出端的线上或者是输出端那个补偿电阻靠近输出口的那一端?

2019-05-07 13:51:27

PCB走线之问会产生串扰现象,这种串扰不仅仅会在时钟和其周围信号之间产生,也会发生在其他关键信号上,如数据、地址、控制和输入/输出信号线等,都会受到串扰和耦合影响。为了解决这些信号的串扰

2018-11-27 15:26:40

的EMI,如果不对差分信号进行恰当的平衡或滤波,或者存在任何共模信号,就可能会产生EMI问题;其次是和单端信号相比,传输差分信号需要双倍的信号线。 如图2所示为差分对走线在PCB上的横截面。D为两个差

2018-11-27 10:56:15

电子发烧友App

电子发烧友App

评论