在Protel的硬件开发中,PCB设计中的3W和20H原则很重要,本文就介绍了是3W原则、20H原则、五五规则,这些值得借鉴。

2016-07-05 14:25:35 6513

6513

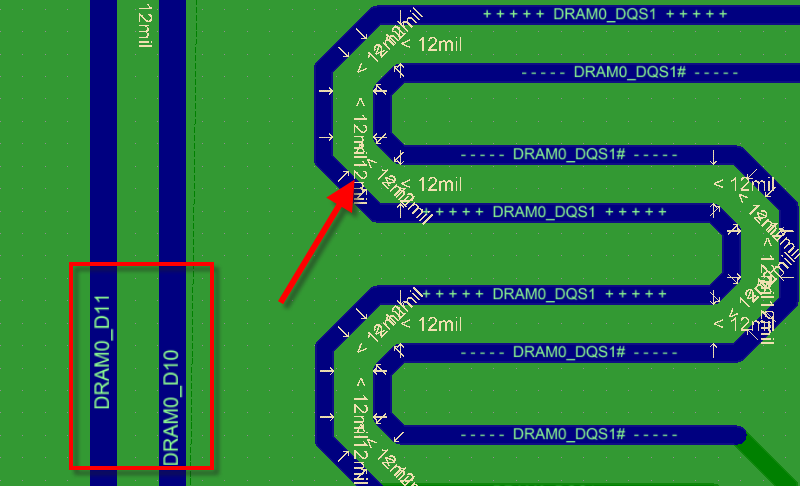

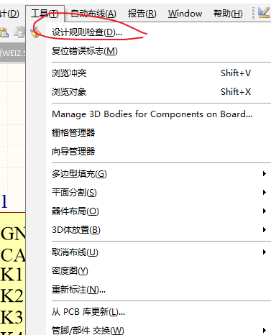

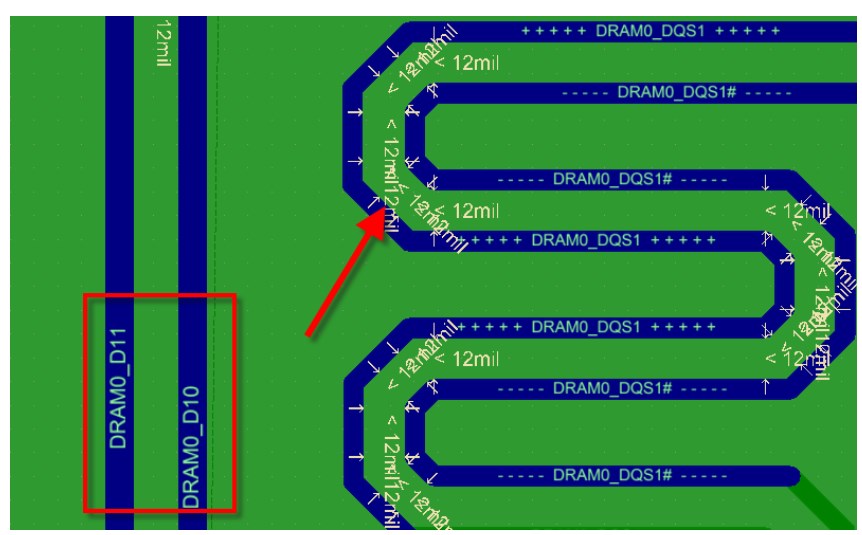

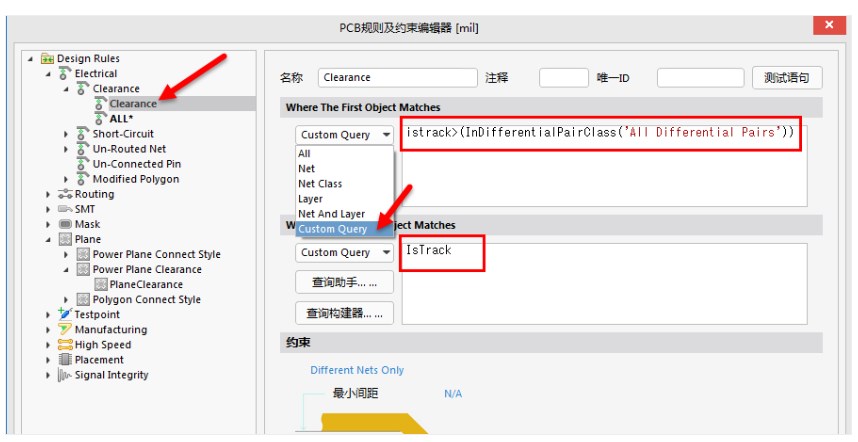

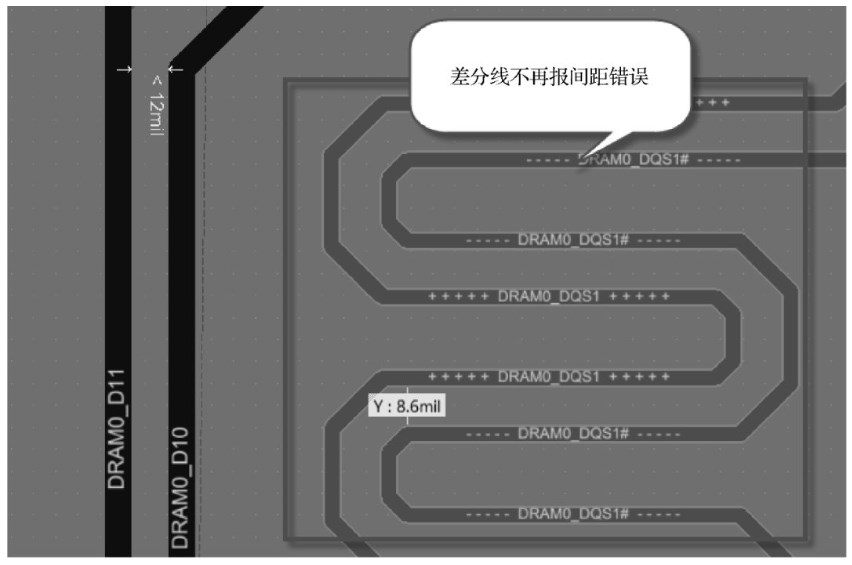

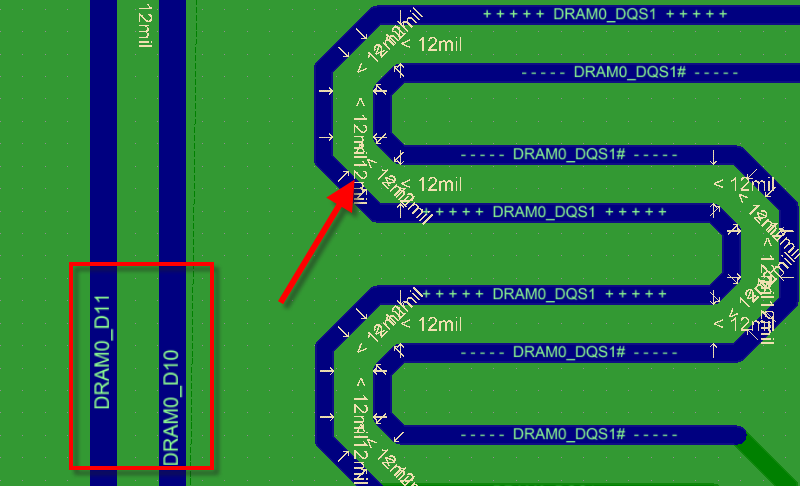

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则

2020-04-22 15:26:26 15164

15164

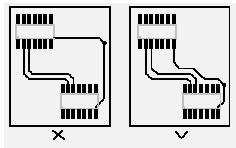

布线是PCB设计的重要组成部分,也是整个PCB设计中工作量最大和最耗时间的部分,工程师在进行PCB布线工作时,需要遵循一些基本的规则,如倒角规则、3W规则等。

2022-10-31 14:30:32 1100

1100 本文主要介绍PCB设计中常见的“3W原则”。 什么是“3W原则” 在PCB设计时,为了减少线间串扰,经常会听说“3W原则”、“20H原则”、“五五规则”等,下面就具体来介绍一下3W原则。3W原则其实

2020-12-09 14:39:24 14430

14430

3W规则是什么?20H规则是什么?五---五规则是什么

2021-04-27 06:09:43

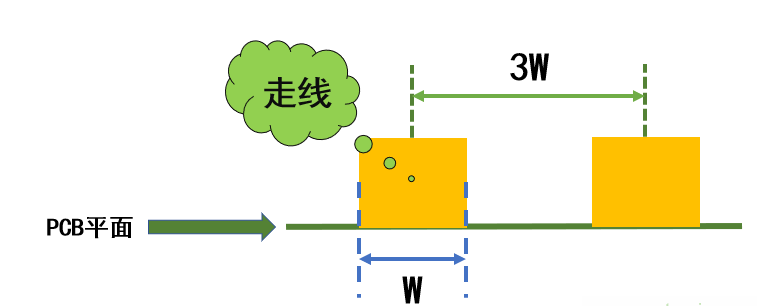

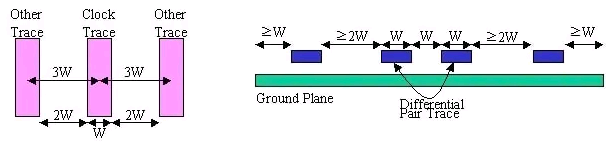

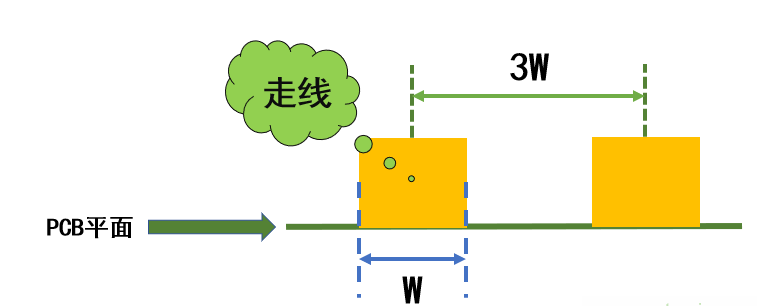

3W原则在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。3W原则是指多个高速信号线长距离走线的时候,其间距...

2022-01-26 06:50:22

3W原则:4 A2 [3 F4 A. C这里3W是线与线之间的距离保持3倍线宽。你说3H也可以。但是这里H指的是线宽度。不是介质厚度。是为了减少线间串扰,应保证线间距足够大,如果线中心距不少于3倍

2014-10-28 15:29:44

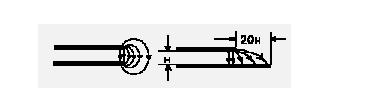

保证线间距足够大,如果线中心距不少于3倍线宽时,则可保持70%的线间电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W规则。针对EMI20H原则:是指电源层相对地层内缩20H

2012-01-17 14:21:41

需要直角拐角的情况下,可以采取两种改进方法:一是将90°拐角变成两

器件去耦规则

在印制版上增加必要的去耦电容,滤除电源上的干扰信号,使电源信号稳定。

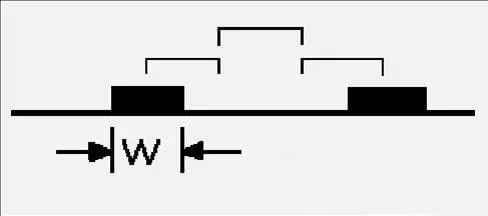

3W规则

为了减少线间串扰,应保证线间距足够大,当

2023-11-14 16:06:37

本帖最后由 hxing 于 2014-3-6 14:59 编辑

3W规则为了减少线间窜扰,应保证线间距足够大,当线中心距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到

2014-03-06 14:54:15

PCB板布线设计完成后,需认真检查布线设计是否符合设计者所制定的规则,同时也需确认所制定的规则是否符合PCB板生产工艺的需求,一般检查有如下几个方面: (1)线与线,线与元件焊盘,线与贯通孔,元件

2016-11-27 22:04:50

的串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。3W规则可保持70%的电场不互相干扰,使用10W的间距时,可以达到98%的电场不互相干扰。3、电源

2022-12-15 16:28:19

@[TOC]PCB设计经验(1)#PCB设计规则#PCB走线经验#快捷键的使用#易犯错误汇总

2021-11-10 08:19:25

请问PCB设计规则怎样设置?怎样设置PCB的电气规则检查?比如说线宽,焊盘间的距离,线与线之间的间距,焊盘与线之间的间距怎样定义设置?

2016-08-13 16:57:56

本帖最后由 gk320830 于 2015-3-7 13:19 编辑

PCB设计规则检查器编写技巧本文简单阐述一种编写pcb设计规则检查器(DRC)系统方法。利用电路图生成工具得到PCB设计后

2013-10-16 11:36:12

本帖最后由 gk320830 于 2015-3-7 14:14 编辑

PCB设计规则检查器编写技巧本文简单阐述一种编写pcb设计规则检查器(DRC)系统方法。利用电路图生成工具得到PCB设计后

2013-10-08 11:24:40

本文简单阐述一种编写pcb设计规则检查器(DRC)系统方法。利用电路图生成工具得到PCB设计后,即可运行DRC以找到任何违反PCB设计规则故障。这些操作必须在后续处理开始之前完成,而且开发

2018-09-14 16:27:19

PCB设计规则你知几何,20个PCB设计规则送给你。

2021-11-11 07:16:18

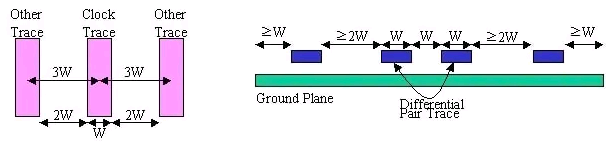

?对串扰有一个量化的概念将会让我们的设计更加有把握。1.3W规则在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如(图1

2014-10-21 09:53:31

`3W原则在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。3W原则是指多个高速信号线长距离走线的时候,其间距应该遵循

2020-09-27 16:49:19

应在1MM以上。 4、离电路板边缘一般不小于2MM.电路板的最佳形状为矩形,长宽比为3:2或4:3.电路板面尺大于200MM乘150MM时,应考虑电路板所能承受的机械强度。 PCB设计设置

2018-09-17 17:36:11

应在1MM以上。 4、离电路板边缘一般不小于2MM.电路板的最佳形状为矩形,长宽比为3:2或4:3.电路板面尺大于200MM乘150MM时,应考虑电路板所能承受的机械强度。 PCB设计设置

2018-09-17 17:38:21

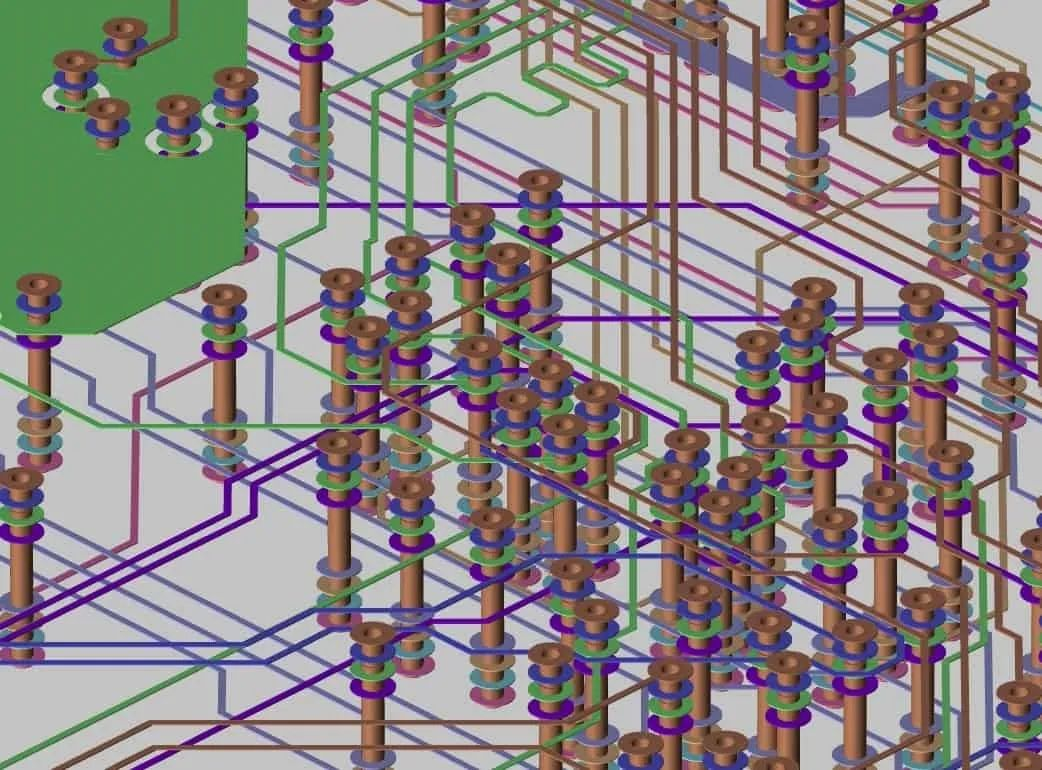

PCB设计流程PCB规则设置设计规则的单位跟随画布属性里设置的单位,此处单位是mil。导线线宽最小为10mil;不同网络元素之间最小间距为8mil;孔外径为24mil,孔内径为12mil;线长不做

2022-01-11 06:14:06

PCB设计中的3W规则主要是为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰, 称为3W规则。 如要达到98%的电场不互相干扰, 可使用10W的间距。

2019-05-21 09:40:51

PCB设计是指印制电路板设计。印制电路板的设计是以电路原理图为根据,实现电路设计者所需要的功能。印刷电路板的设计主要指版图设计,需要考虑外部连接的布局、内部电子元件的优化布局、金属连线和通孔的优化

2017-06-03 16:55:26

PCB设计走线的规则是什么

2021-03-17 06:36:28

前一期对物理规则和间距规则进行了设置,本期板儿妹继续给大家介绍区域约束规则设置。用PCB设计工具进行画板,对于不同的走线,线宽与线距要求是不同的,比如电源走线、时钟走线、差分走线等,但是这些走线

2016-12-28 10:45:56

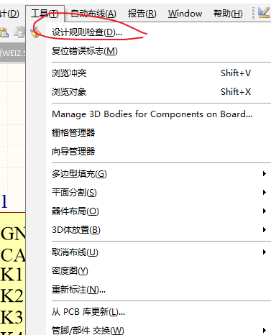

设计中的元件装配方面问题。检查对象包括:元件间距、引脚跨距、焊盘跨距轴向、过孔及测试点等。在可装配性检查时,PCB设计中与约束不一致时将会以DRC形式标示出来。在AllegroPCB工作界面中执行

2019-06-07 06:00:00

的。画好区域规则后:下面我们来设规则:在design>rules(快捷键D+R)弹出下面对话框: 根据上图所示,来设计线间距规则,线宽规则,过孔规则在设计规则选择Advanced(Query),点击

2019-07-05 08:24:27

里的,导线间距、铜箔与导线间距都为5,布线优先级为2,查看了下默认规则的间距为6,优先级3。现象是画出来的线间距为5,但是和铜箔的间距为6,USB类规则里导线和铜箔安全间距为5的约束为什么不起作用呢?先谢过各位大侠!

2019-04-02 20:53:59

cadence pcb布线怎么实现3w原则的? 找不到规则设定的命令 求前辈指点一下

2016-01-25 22:48:42

本帖最后由 cooldog123pp 于 2019-8-10 22:44 编辑

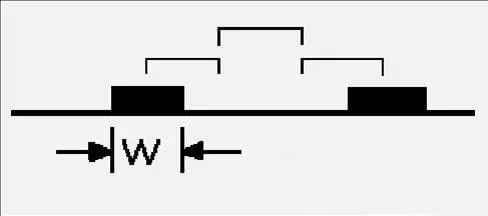

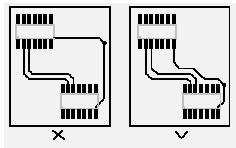

3W规则:3w就是两条线的间距是线宽的两倍 如图1 图1为了减少线间串扰,应保证线间距足够大,当线中心间距

2015-12-12 20:37:31

规则: 3w就是两条线的间距是线宽的两倍 如图1 图1为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相

2016-09-06 14:43:52

为什么运行规则检查的时候会出现这样的情况?

2019-08-29 05:35:06

在allegro pcb的设计过程中,设计约束规则包括时序规则、间距规则、信号完整性规则以及物理规则等,本期主要详细讲解与物理、间距与电气约束中的线宽、线间距物理规则的设置。一、线宽设置(1)设置

2016-12-23 17:08:25

最近学习PCB布线,其他人的板子好像线与线之间距离能满足3W原则,这个规则到底是在哪里设置的呢?

2016-01-09 20:50:03

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。如下图所示。满足3W原则能使信号间的串扰减少70%,而满足10W则能

2019-05-08 08:30:00

请问大神怎样去编写属于自己的PCB设计规则检查器?

2021-04-26 06:32:11

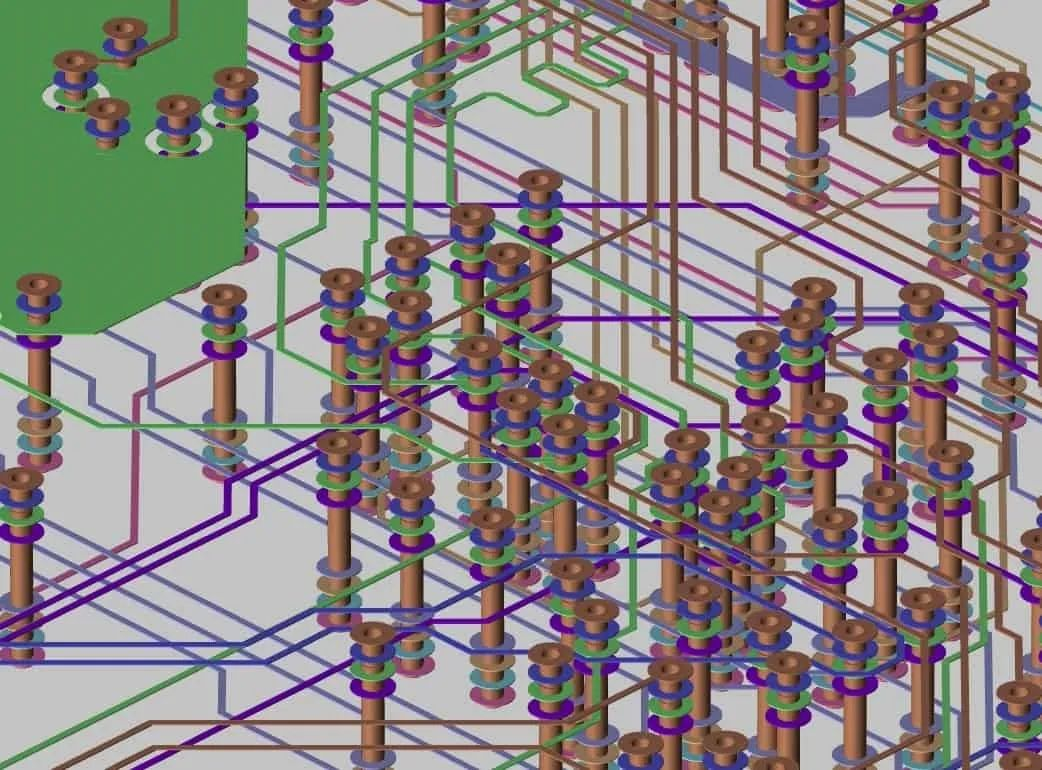

在DDR走线过程中如何对数据线D0-D15这十六条线进行他们之间的3W规则设置

2019-06-17 05:18:13

。 7、3W规则 为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。 8、地线回路规则

2023-04-18 15:04:04

倒角规则 器件去耦规则 器件布局分区/分层规则 孤立铜区控制规则 电源与地线层的完整性规则 重叠电源与地线层规则 3W规则 20H 规则 五——五规则二、规则详细解释1.地线回路规则[/url

2015-02-03 14:44:13

本帖最后由 gk320830 于 2015-3-7 11:59 编辑

编写PCB设计规则检查器技巧本文阐述了一种编写pcb设计规则检查器(DRC)系统方法。利用电路图生成工具得到PCB设计后

2013-10-29 11:28:30

本文阐述了一种编写pcb设计规则检查器(DRC)系统方法。利用电路图生成工具得到PCB设计后,即可运行DRC以找到任何违反设计规则故障。这些操作必须在后续处理开始之前完成,而且开发电路图生成工具

2018-09-10 16:28:09

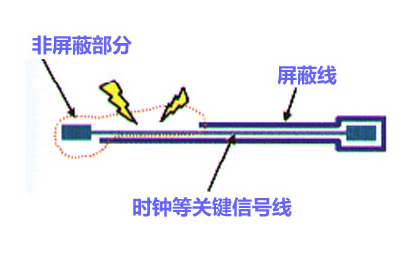

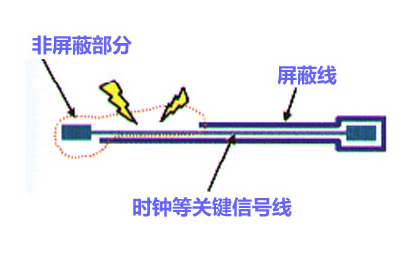

的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。规则二:高速信号的走线闭环规则由于PCB板的密度越来越高

2017-11-02 12:11:12

请问一下,电源线与信号线的间距,不同电源线间的间距要不要遵循3W的规则?

2019-06-13 05:35:18

规则设置是否Ok? 8是否设计模拟、电源、RF、热设计等部分,需要由信号完整型工程师确认 9异型PCB尺寸? 10禁布区域设置,2h/3W原则考虑是否合理 11特殊网络走线设置(线宽、间距、走线层等

2015-11-11 16:01:42

`请问高速PCB设计规则有哪些?`

2020-02-25 16:07:38

本节继续讲解PCB设计的约束管理器之线间距设置。(1)设置默认间距规则单击 Spacing,再点击 All Layers,如下图所示。右边有一个DEFAULT 就是默认规则,可以修改其值。按住

2017-07-21 10:44:52

本节继续讲解PCB设计中差分信号的规则设置。差分信号的规则可以在电气规则下面建立,也可以在物理规则下面建立;电气规则下建立的差分信号规则是全局性的,不受区域规则的约束,在BGA等需要密集出线的地方

2017-08-15 10:27:49

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地

2016-01-19 22:50:31

上一期我们介绍了高速PCB设计软件allegro16.6差分信号的设定在高速PCB布线前需要对差分信号的规则进行设置因此本期重点介绍在电气规则和物理规则下是如何建立差分信号的规则1、在电气规则下建立

2017-01-06 09:46:41

通过串音预测对PCB布线的3W规则进行验证:在传输线理论的基础上,利用有限元(FEM)法计算分层介质中微带线上场的分布,并通过SPICE仿真对其等效电路在不同频率电源激励下产生

2009-09-21 08:26:13 0

0 PCB设计中20H规则的验证方法:随着电路工作频率的上升,PCB设计面临越来越多的电磁辐射问题。20H规则是减小电路板辐射的设计规则之一。

2009-09-26 08:30:43 0

0 PCB设计时应该遵循的规则

1) 地线回路规则:

环路最小

2007-12-12 14:48:15 1096

1096

什么是3W规则 20H规则 五五规则

3W规则:

2007-12-12 15:33:29 5025

5025

编写PCB设计规则检查器技巧

本文阐述了一种编写PCB设计规则检查器(DRC)系统方法。利用电路图生成工具得到PCB设计后,即可运

2009-11-17 14:03:10 1019

1019 编写属于自己的PCB设计规则检查器

编写属于自己的PCB设计规则检查器具有很多优点,尽管设计检查器并不那么简单,但也并非高不可攀,因为任何熟悉现有编程或脚本

2009-12-27 13:31:01 811

811

AD9上PCB布线规则检查合理设置好,可以帮助我们提高布线效率以及辅助我们检查相应错误

2015-10-29 16:22:50 0

0 Protel硬件开发PCB设计的3W和20H原则及五五规则,感兴趣的小伙伴们可以瞧一瞧。

2016-10-26 15:55:29 0

0 规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有

2017-11-25 07:43:00 7508

7508

会按下表依次列出: 以上的规则检查项对应的中文翻译、具体的规则设置、约束的具体PCB内容讲解如下: 1. Clearance Constraint (Gap=10mil) (All),(All) 间隙约束,也就是约束PCB中的电气间距,比如阻容各类元件的焊盘间距小于规则中的设定值,即报警。 如下图中

2019-01-14 09:17:40 14797

14797 为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。如要达到98%的电场不互相干扰,可使用10W的间距。

2019-06-17 14:43:12 1675

1675

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W原则。

2019-05-11 11:22:32 10413

10413 PADS® HyperLynx® DRC 提供功能强大的定制 PCB 设计电气规则检查器。不同于走线间距和线板边缘边界等传统 PCB 检查,PADS HyperLynx DRC 包括一套完整的规则集,可用来识别出经常导致 EMI 或 SI 问题的 Layout 疏漏。

2019-05-21 06:08:00 5935

5935 为了迎台市场的需求,大多数加工厂的工艺都在不断进步,对于目前的工艺来说生产线间距等于甚至小于0.1mm的产品已经不是难事。考虑到开关电源所采用的元器件及生产工艺,一般双面板最小线间距设为0.3mm

2019-05-20 15:55:45 15543

15543 PCB板布线设计完成后,需认真检查布线设计是否符合设计者所制定的规则,同时也需确认所制定的规则是否符合PCB板生产工艺的需求。

2019-08-12 12:35:05 2957

2957 layout完成后,需要对PCB进行规则检查,选择Tools--Quick Reports,依次检查 shape Dynamic state,Unconnect Pins Report,Design ruler Check(DRC) Report。

2019-08-21 08:40:17 10349

10349 高速PCB设计EMI有什么规则

2019-08-21 14:38:03 807

807

在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W原则。

2019-08-21 15:00:54 4646

4646 刚果民主共和国垫®HyperLynx®提供了一个可定制的和强大的PCB设计电气规则检查。代替传统的PCB检查如道间间距和trace-to-board边缘边界,垫HyperLynx刚果(金)包括一个全面的规则集,确定布局经常引起电磁干扰或SI的疏忽的问题。

2019-11-06 07:08:00 3675

3675 编写属于自己PCB设计规则检查器具有很多优点,尽管PCB设计检查器并不那么简单,但也并非高不可攀,因为任何熟悉现有编程或脚本语言PCB设计人员完全能够PCB设计检查器,这项工作好处是不可估量。

2020-03-27 14:08:51 3354

3354 ,x是最小走线宽度,y是最小走线间隔。例如, 8/10规则指示最小走线宽度为8密耳,最小走线间隔为10密耳。在制造PCB时,需要最小的走线间距和最小的走线宽度。如果在制造过程中使走线小于此最小宽度,则走线可能会打开。如果两条走线比制造过程中的

2020-09-02 18:14:17 3652

3652 PCB设计取决于一套规则和约束条件,这些规则和约束条件决定了电路板的布局方式。这些规则涵盖了各个方面,从组件之间的紧密程度到特定网络的布线厚度。但是,成功的唯一方法是为每个作业专门设计规则。以前可行

2021-01-13 13:32:17 3649

3649 在 PCB 设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于 3 倍线宽时,则可保持大部分电场不互相干扰,这就是 3W 规则。 3W 原则是指多个高速信号线长距离走线的时候,其间距应该

2020-12-16 14:49:00 23

23 检查的项目有通用PCB设计图检查项目、PCB电气特性检查项目、PCB物理特性检查项目、PCB机械设计因素、PCB印制板的安装要求、印制板的拨出要求、PCB机械方面的考虑、PCB电气考虑、PCB布线路径和定位、PCB宽度和厚度、PCB导线间距、PCB导线图形检查、PCB设计项目检

2021-08-17 16:45:00 26850

26850 PCB设计规则你知几何,20个PCB设计规则送给你。

2021-11-06 15:36:00 63

63 3W原则在PCB设计中为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持大部分电场不互相干扰,这就是3W规则。3W原则是指多个高速信号线长距离走线的时候,其间距...

2021-12-01 19:21:10 44

44 AD pcb设计规则检查报错Silk To Solder Mask Clearance Constraint报错原因处理方法一:改变规则中的最小间距:方法二:直接取消这一项的检查:结果软件版

2021-12-04 15:21:05 26

26 本期Xpedition入门指南进行规则的设置,规则设置贯穿在全流程当中,比如原理图设计阶段就可以进行规则的设计,布局布线阶段可详细设计高速规则,所以要了解PCB设计流程非常重要,可以建立清晰的设计思路,随时平衡和变化策略以应对复杂的设计。

2022-04-29 13:35:04 6232

6232 最近在总结学习PCB设计规则的相关知识,在一些消费类或者速率要求不高的产品上,还在沿用着“3W原则”。所谓“3W原则”,就是保证线与线的间距,保持线与线中间间距不小于3倍线宽,这样可保证大部分电场串扰在合理范围内。

2023-03-03 12:13:44 6011

6011

一站式PCBA智造厂家今天为大家讲讲PCB设计布局规则有哪些?PCB设计布局规则及技巧。

2023-05-04 09:05:20 1554

1554 我们平时在PCB布线的时候,对于比较重要的信号都要做特殊处理,比如包地或者时“3W”,所谓3w指的是线与线之间的间距要满足三倍的线宽,那么我们怎么理解这个3W原则呢,他是如何降低信号之间的串扰的呢?

2023-05-04 15:58:10 1360

1360

如何理解PCB布线的3W规则?

2023-07-15 08:55:06 1462

1462 由于DRC必须遍历 PCB设计整个电路图,包括每个符号、每个引脚、每个网路、每种属性,如有必要还能创建数目不限“附属”文件。如4.0节所述,DRC可以标示出任何违反设计规则细微偏差。

2023-10-13 14:58:18 209

209 由于DRC必须遍历 PCB设计整个电路图,包括每个符号、每个引脚、每个网路、每种属性,如有必要还能创建数目不限“附属”文件。如4.0节所述,DRC可以标示出任何违反PCB设计规则细微偏差。例如

2023-10-31 15:06:37 159

159 对于Altium Designer来说,在所有的布局,布线,铺铜都完成之后,也就完成了初步的设计工作,接下来就是进行电气规则的检查了。 什么是电气规则的检查呢? 电气规则检查包括很多内容,比如说丝印

2023-11-06 15:17:35 912

912

一站式PCBA智造厂家今天为大家讲讲 pcb设计常见布线规则有哪些?PCB设计常见布线规则。

2023-11-14 09:17:55 606

606

PCB设计中,如何使用规则高效管理过孔

2023-12-06 15:54:54 200

200

在PCB设计中,电压是其中一个最重要的参数。高电压可能会导致电弧放电、电晕、电路之间电耦和干扰等问题,而电路之间的布线间距是决定电压分布的一个重要因素。本文将详尽地阐述PCB布线间距与电压之间的关系

2023-12-20 11:24:00 3243

3243 的不良影响。在进行PCB布线设计时,需要遵循一定的规则和原则,下面我们将会介绍PCB设计中的六大布线规则。 PCB设计六大布线规则 一:按照传输信号速度分类 在布线时需要按照信号传输速度的不同进行分类布线。一般来说,传输速度越快的信号需要

2024-01-22 09:23:53 495

495

电子发烧友App

电子发烧友App

评论