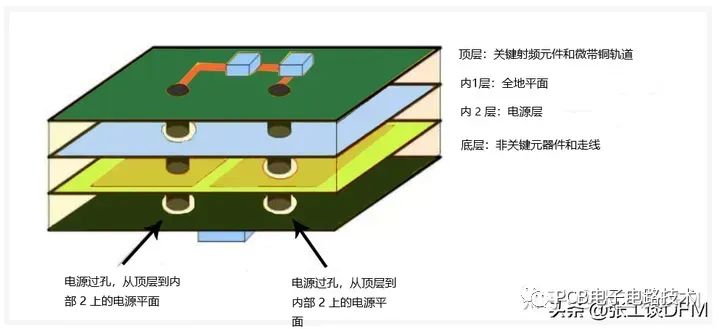

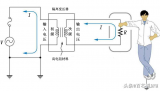

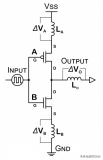

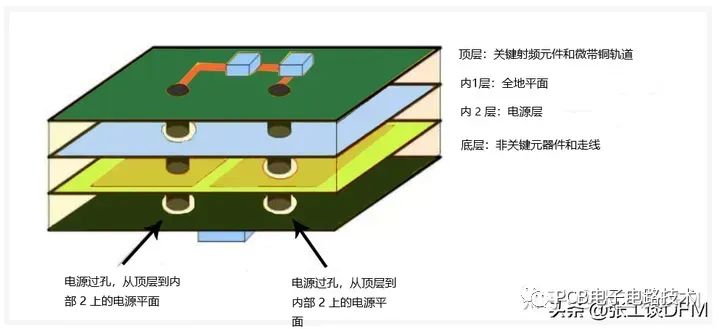

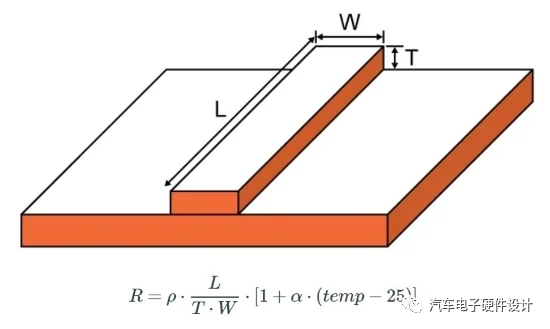

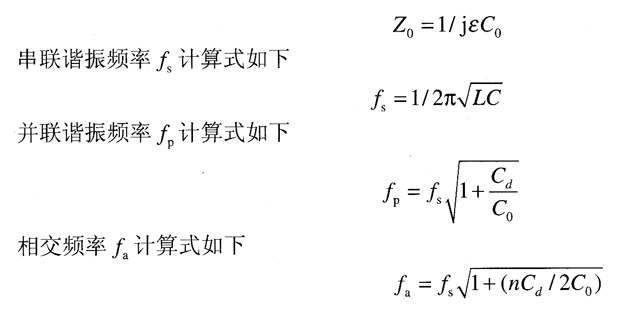

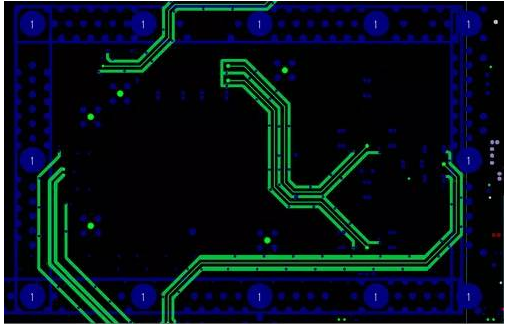

要设计出合格的PDS,需要使用各种电容(见图1)。PCB上使用的典型电容值只能将直流或接近直流频率至约500 MHz范围的阻抗降低。高于500 MHz频率时,电容取决于PCB形成的内部电容。注意,电源层和接地层紧密叠置会有帮助。

2022-07-21 15:38:14 1321

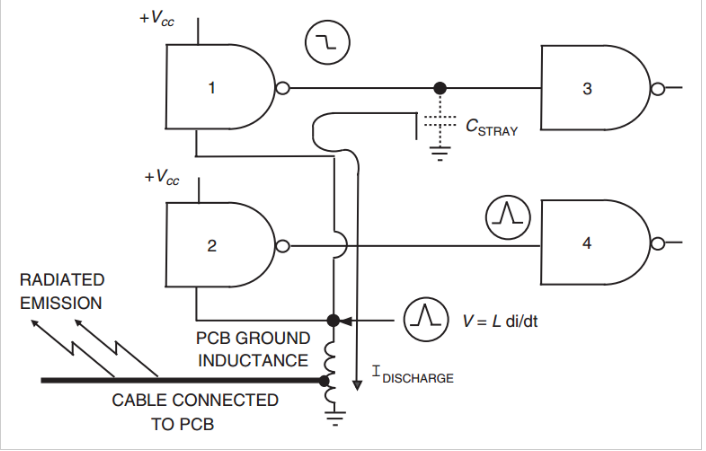

1321 信号返回:常规信号也需要返回,对于高速设计,它们在地平面上有一条清晰的返回路径非常重要。如果没有这种清晰的返回路径,这些信号可能会对PCB的其余部分产生大量干扰。

2022-10-08 10:34:13 2496

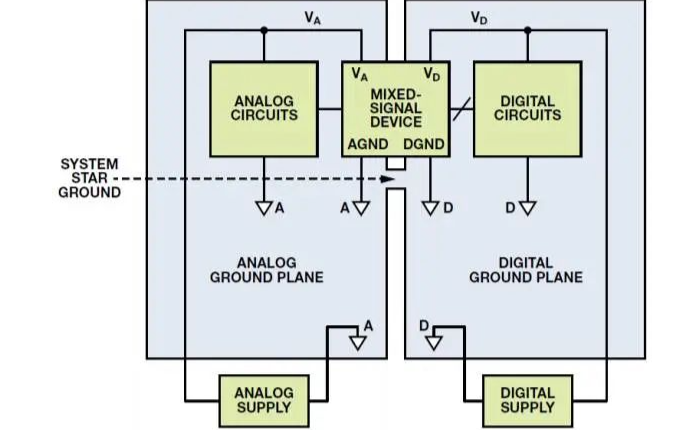

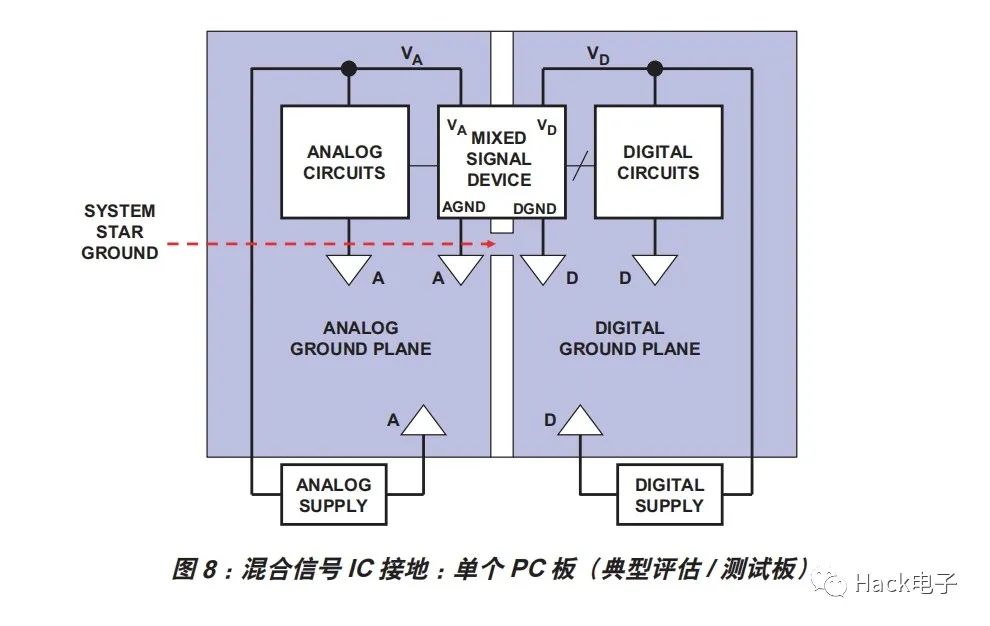

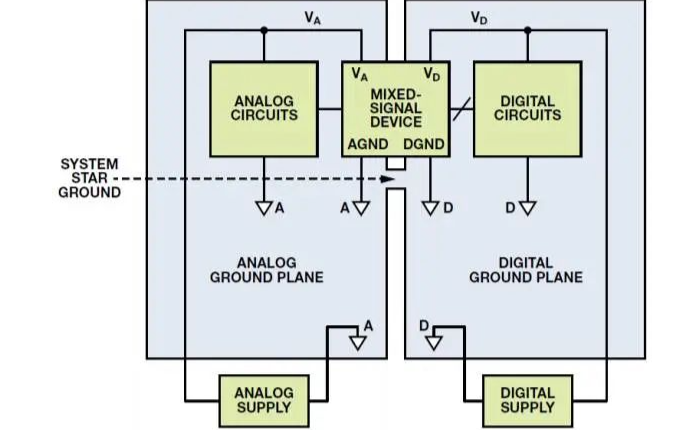

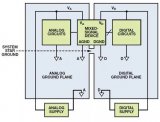

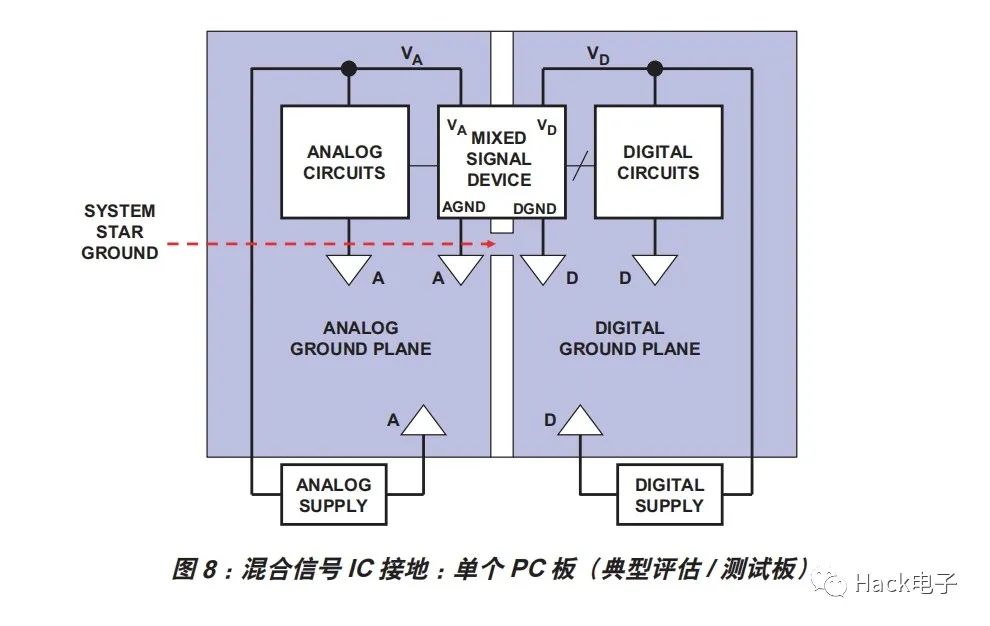

2496 大多数ADC、DAC和其他混合信号器件数据手册是针对单个PCB讨论接地,通常是制造商自己的评估板。将这些原理应用于多卡或多ADC/DAC系统时,就会让人感觉困惑茫然。通常建议将PCB接地层分为模拟

2022-10-17 10:04:05 494

494 根据经验,在信号走线下方添加一个公共接地层,这样可以确保PCB中任意2个接地点之间的阻抗最小。

2023-11-16 12:26:42 679

679

经常说要把PCB的接地层与底盘连接,请问这是为什么啊?还有说要通过CR network将PCB接地与底盘连接,这样会有什么好处?谢谢各位大侠赐教!

2015-06-16 11:42:57

,那么外部数字地电流所产生的额外噪声基本上不会构成问题。接地层接地层的使用与上文讨论的星型接地系统相关。为了实施接地层,双面PCB(或多层PCB的一层)的一面由连续铜制造,而且用作地。其理论基础是大量金属

2014-11-20 10:52:04

去耦至PC板的数字接地层。请注意,模拟与数字接地层间的任何噪声均可降低转换器数字接口上的噪声裕量。由于数字噪声抗扰度在数百或数千毫伏水平,因此一般不太可能有问题。模拟接地层噪声通常不高,但如果数字接地层

2014-11-20 10:57:15

接地层上的ADC。两层之间的接地噪声直接添加到时钟信号,并产生过度抖动。抖动可造成信噪比降低,还会产生干扰谐波。图7. 从数模接地层进行采样时钟分配。混合信号接地的困惑根源大多数ADC、DAC和其他混合

2014-11-20 10:58:30

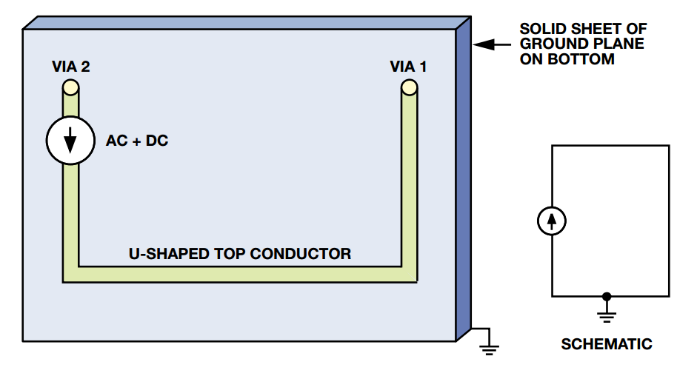

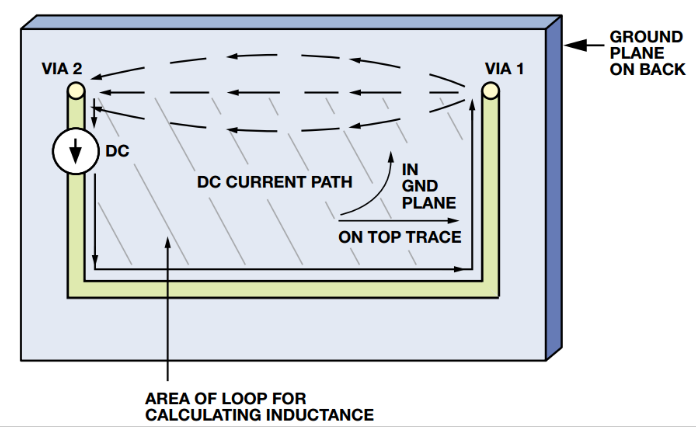

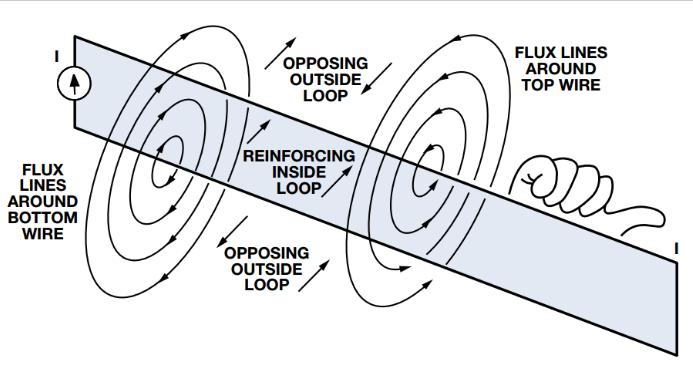

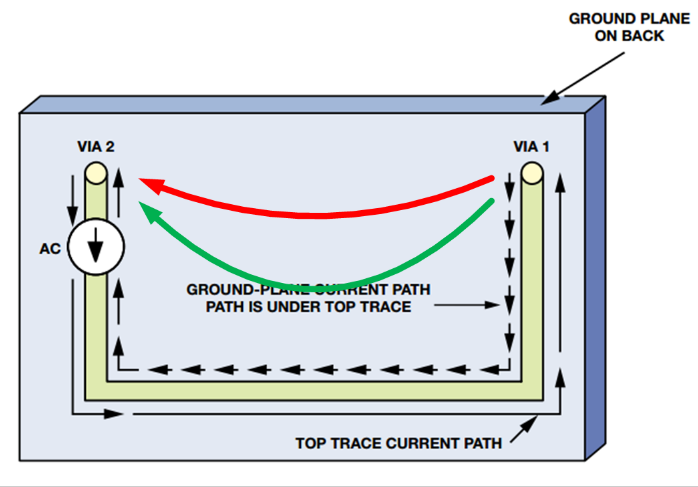

实际问题所在,并找到消除高频布局接地噪声的方法。图10. 图9所示PCB的直流电流的流动。图10所示的直流电流的流动方式,选取了接地层中从过孔1至过孔2的电阻最小的路径。虽然会发生一些电流扩散,但基本上

2014-11-20 11:00:35

时,提供尽可能多的选项会很有帮助。PC板必须至少有一层专用于接地层!初始电路板布局应提供非重叠的模拟和数字接地层,如果需要,应在数个位置提供焊盘和过孔,以便安装背对背肖特基二极管或铁氧体磁珠。此外,需要

2014-11-20 11:05:20

PCB设计的小型化。目前,解决串扰问题的主要方法是进行接地层管理,在布线之间进行间隔和降低引线电感(stud capacitance)。降低回损的主要方法是进行阻抗匹配。此方法包括对绝缘材料的有效管理

2009-03-25 11:49:47

电子设备的灵敏度越来越高,这要求设备的抗干扰能力也越来越强,因此PCB设计也变得更加困难,如何提高PCB的抗干扰能力成为众多工程师们关注的重点问题之一。本文将介绍PCB设计中降低噪声与电磁干扰的一些

2018-09-18 15:40:54

设计:降低噪声与电磁干扰的24个窍门》为PCB设计中降低噪声与电磁干扰提供了非常实用的建议,值得筒子们阅读收藏。

2019-05-31 06:39:14

PCB设计中为什么要求电源层紧靠地层,有什么作用吗?

2014-10-24 14:22:08

电子设备的灵敏度越来越高,这要求设备的抗干扰能力也越来越强,因此PCB设计也变得更加困难,如何提高PCB的抗干扰能力成为众多工程师们关注的重点问题之一。本文将介绍PCB设计中降低噪声与电磁干扰

2018-11-28 17:05:55

电子设备的灵敏度越来越高,这要求设备的抗干扰能力也越来越强,因此PCB设计也变得更加困难,如何提高PCB的抗干扰能力成为众多工程师们关注的重点问题之一。本文将介绍PCB设计中降低噪声与电磁干扰的一些

2018-12-21 09:29:36

。如上所述,根据IC的PSR,这会产生各种类型的性能降低。通过使用尽可能短的连接,将适当类型的局部去耦电容直接连接到电源引脚和接地层之间,可以最大限度地降低对功率噪声和纹波的灵敏度。去耦电容用作瞬态电流

2018-10-19 10:49:11

方法是进行接地层管理,在布线之间进行间隔和降低引线电感(studcapacitance)。降低回损的主要方法是进行阻抗匹配。此方法包括对绝缘材料的有效管理以及对有源信号线和地线进行隔离,尤其在状态发生

2018-09-13 15:53:21

降低噪声与干扰1) 能用低速芯片就不用高速的,高速芯片用在关键地方。(2) 可用串一个电阻的办法,降低控制电路上下沿跳变速

2010-02-26 11:42:31

电子设备的灵敏度越来越高,这要求设备的抗干扰能力也越来越强,因此PCB设计也变得更加困难,如何提高PCB的抗干扰能力成为众多工程师们关注的重点问题之一。本文将介绍PCB设计中降低噪声与电磁干扰的一些

2019-01-26 22:53:49

在多卡系统中,降低接地阻抗的最佳方式是使用“母板”PCB 作为卡间互连背板,从而为背板提供连续接地层。PCB 连接器的引脚应至少有 30 至 40% 专用于接地,这些引脚应连接到背板母板上的接地层

2018-10-25 09:24:22

在多卡系统中,降低接地阻抗的最佳方式是使用“母板”PCB 作为卡间互连背板,从而为背板提供连续接地层。PCB 连接器的引脚应至少有 30 至 40% 专用于接地,这些引脚应连接到背板母板上的接地层

2018-12-06 09:07:35

技巧

技巧1:将PCB接地

降低EMI的一个重要途径是设计PCB接地层。第一步是使PCB电路板总面积内的接地面积尽可能大,这样可以减少发射、串扰和噪声。将每个元器件连接到接地点或接地层时必须特别小心,如果

2023-12-19 09:53:34

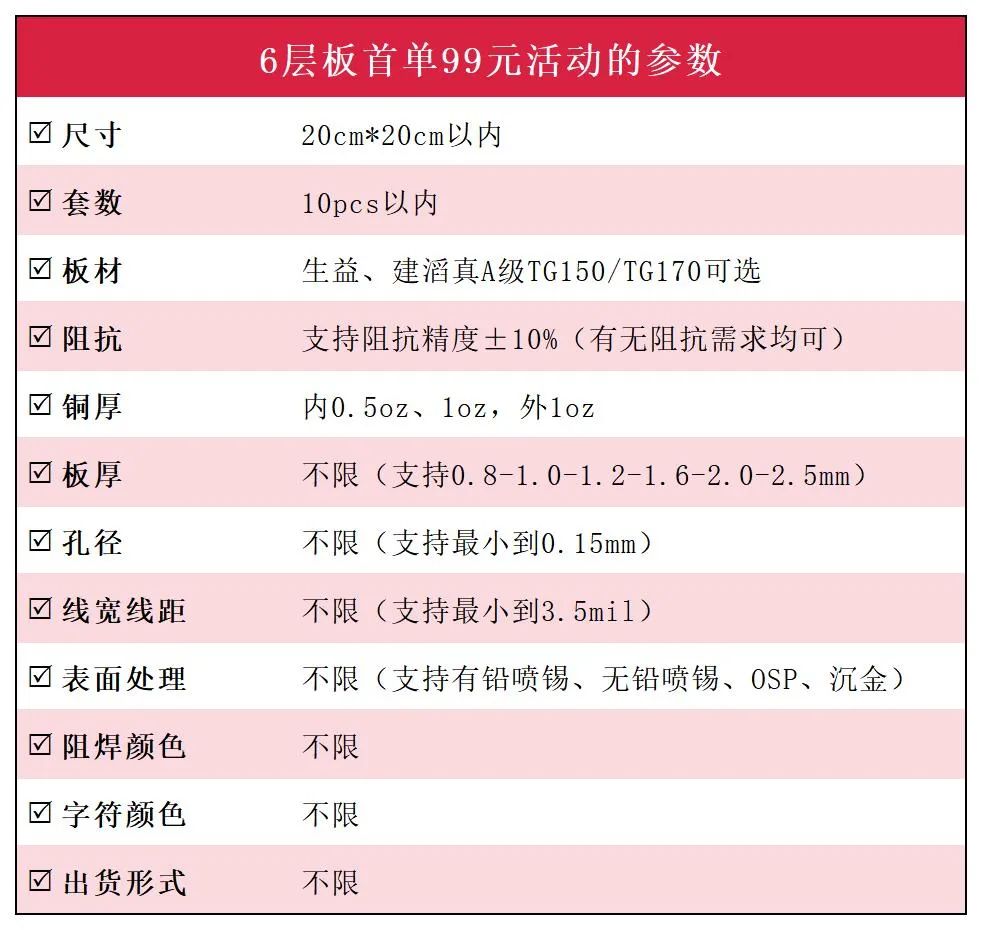

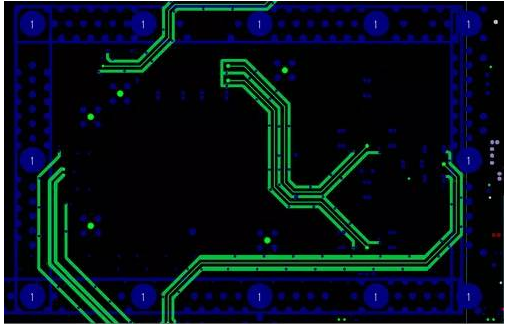

,以换来了更好的布局效果——每个信号层、电源层均与地层相邻。其中S2作为优先布局的重要信号,其次是S3,再是S1。

6层板PCB中有2个地层可以更好地隔离和吸收来自其他层的噪声和干扰,提供更好的电磁兼容

2023-12-08 10:49:19

电子设备的灵敏度越来越高,这要求设备的抗干扰能力也越来越强,因此PCB设计也变得更加困难,如何提高PCB的抗干扰能力成为众多工程师们关注的重点问题之一。本文将介绍PCB设计中降低噪声与电磁干扰的一些

2018-03-10 21:32:11

电子设备的灵敏度越来越高,这要求设备的抗干扰能力也越来越强,因此PCB设计也变得更加困难,如何提高PCB的抗干扰能力成为众多工程师们关注的重点问题之一。本文将介绍PCB设计中降低噪声与电磁干扰的一些

2019-02-01 22:35:31

直接耦合到放大器输入端,造成干扰。在PCB布线时,要注意电源线与弱信号线不要贴近平行走线,线净距大于线宽的3倍(3W原则),并在电源线或数字信号线与模拟小信号线之间加地线隔离。接地处理不当,噪声通过

2018-03-28 17:14:04

,以换来了更好的布局效果——每个信号层、电源层均与地层相邻。其中S2作为优先布局的重要信号,其次是S3,再是S1。

6层板PCB中有2个地层可以更好地隔离和吸收来自其他层的噪声和干扰,提供更好的电磁兼容

2023-12-08 10:34:06

,分离接地层只会增加返回电流的电感,它所带来的坏处大于好处。从公式V = L(di/dt)可以看出,随着电感增加,电压噪声会提高。而随着开关电流增大(因为转换器采样速率提高),电压噪声同样会提高。因此

2014-09-12 11:11:00

,分离接地层只会增加返回电流的电感,它所带来的坏处大于好处。从公式V = L(di/dt)可以看出,随着电感增加,电压噪声会提高。而随着开关电流增大(因为转换器采样速率提高),电压噪声同样会提高。因此

2018-10-17 15:24:17

,模拟与数字接地层间的任何噪声均可降低转换器数字接口上的噪声裕量。由于数字噪声抗扰度在数百或数千毫伏水平,因此一般不太可能有问题。模拟接地层噪声通常不高,但如果数字接地层上的噪声(相对于模拟接地层)超过

2019-12-29 08:30:00

本文将讨论分割接地层的利弊,还解释了多转换器和多板系统接地。

2021-04-06 08:56:37

南华大学黄智伟 利用接地平面降低MSP430系统的地线噪声

2013-04-05 19:54:03

问题:在哪里连接开关稳压器的接地层

2019-02-28 09:43:23

。由于内层拼接电容能够构建低电感结构,因此最具优势。在整体PCB区域受限的情况下,采用多层PCB就是很好的方式。采用尽可能多的层数切实可行,同时尽可能多的交叠电源层和接地层(参考层)。图1为一个堆叠示例

2018-11-01 10:47:27

N9 RADI PCB接地设计宝典上说“对于高性能混合信号电路而言,使用至少具有一个连续接地层的双面或多层PCB无疑是最成功的设计方法之一。通常,此类接地层的阻抗足够低,允许系统的模拟和数字部分共用一

2014-10-28 14:25:23

板,第一层和第七层是GND层,这样问题就出现了,这两个地平面也就是两个GND层是数字地还是模拟地?ADI PCB接地设计宝典上说“对于高性能混合信号电路而言,使用至少具有一个连续接地层的双面或多层

2014-11-07 09:32:10

板,第一层和第七层是GND层,这样问题就出现了,这两个地平面也就是两个GND层是数字地还是模拟地?ADI PCB接地设计宝典上说“对于高性能混合信号电路而言,使用至少具有一个连续接地层的双面或多层

2015-11-14 20:59:03

,LC型滤波元件地......)和数字地DGND和模拟地AGND。建议作中间地层分割处理,每种地信号间隔2mm即可,然后所有地信号在接地螺丝边上共地。在元器件布局时,尽量让有连大地元件靠近接地螺丝孔

2018-09-13 16:10:54

如何降低步进电机的噪声?

2021-02-22 06:45:32

电源线不要和信号线捆扎在一起。

小结

在运放电路设计中降低电源噪声的主要措施包括:

通过去耦、滤波等措施降低电源输出的纹波和噪声成分。

改善设计,提高电源电压调整率。

合理电路结构、考究的PCB布线、合理的走线工艺。

选择在敏感噪声频段的PSRR或CMRR较高的器件。

2023-11-21 06:27:27

到放大器输入端,造成干扰。在PCB布线时,要注意电源线与弱信号线不要贴近平行走线,线净距大于线宽的3倍(3W原则),并在电源线或数字信号线与模拟小信号线之间加地线隔离。接地处理不当,噪声通过公共阻抗

2017-10-19 23:34:27

;使用1000p电容射频多点接地,可以兼顾EMC和低频信噪比的需求;对敏感电路加屏蔽,注意屏蔽层连接到被保护信号的参考地;走线设计上注意电源线不要和信号线捆扎在一起。小结在运放电路设计中降低电源噪声的主要

2018-12-29 10:10:32

如何正确使用带有接地层的开关稳压器

2021-03-12 07:36:49

EMI的一个重要途径是设计PCB接地层。第一步是使PCB电路板总面积内的接地面积尽可能大,这样可以减少发射、串扰和噪声。将每个元器件连接到接地点或接地层时必须特别小心,如果不这样做,就不能充分利用可靠

2022-06-07 15:46:10

误差。 显示了模拟接地回路中流动的高噪声数字电流如何在输入模拟电路的电压V IN 中产生误差。将模拟电路地和数字电路地连接在同一点(如下方的正确电路图所示),可以在某种程度上缓解上述问题。接地层在当

2019-06-13 04:20:08

的作用。另外,电容必需具有较低的接地阻抗,从而降低电容的高频阻抗。电容的接地引脚应直接到接层,不要通过一段引线后接地。5.将所有不使用的PCB区域覆铜,作为地层两片铜箔彼此靠近时,它们之间就会形成一个

2015-01-07 15:37:20

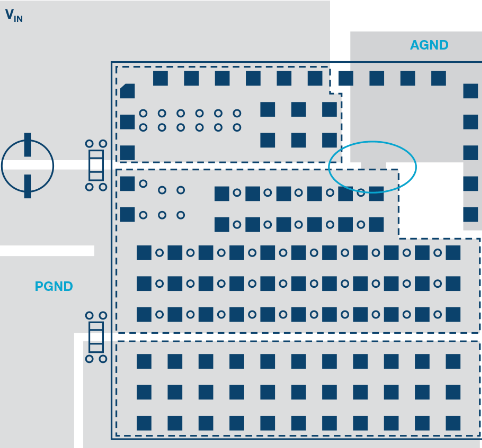

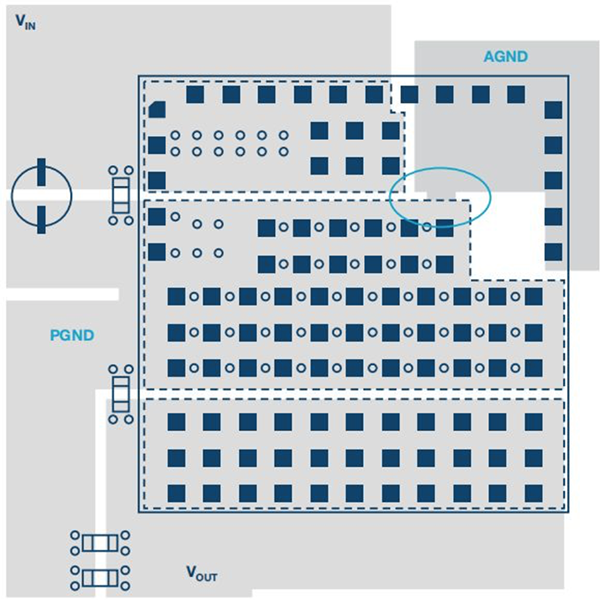

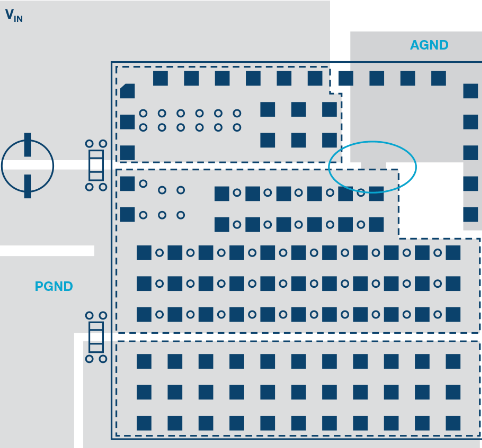

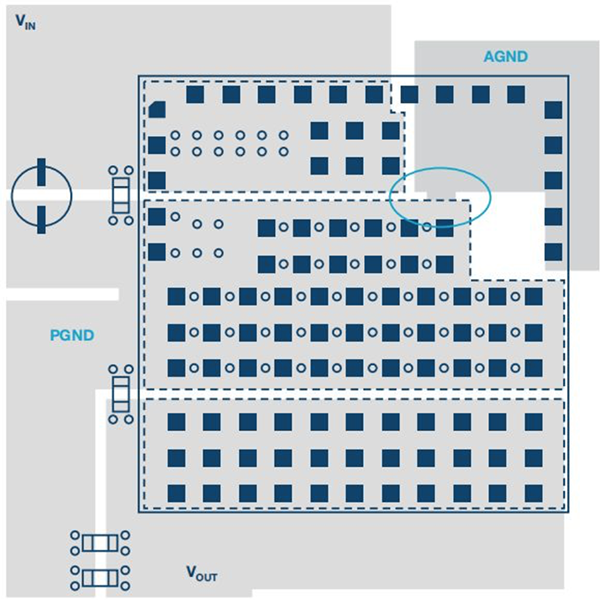

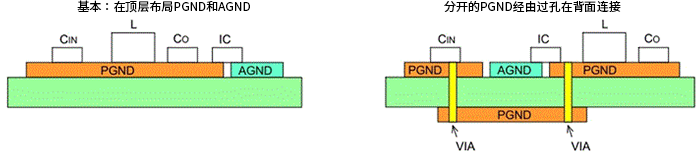

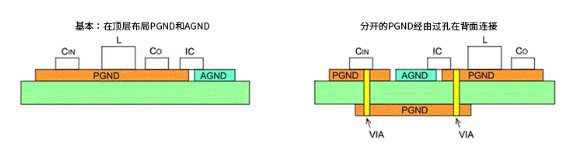

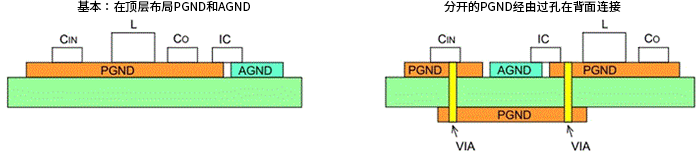

你平时是如何使用带有模拟接地层(AGND)和功率接地层(PGND)的开关稳压器的?如果习惯于处理数字接地层和模拟接地层,在涉及功率GND时,你有木有手足无措的感觉呢?

2019-08-09 08:22:42

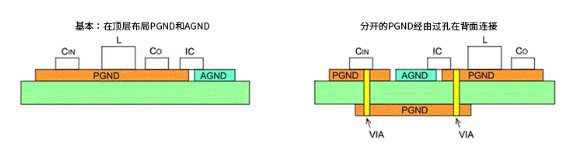

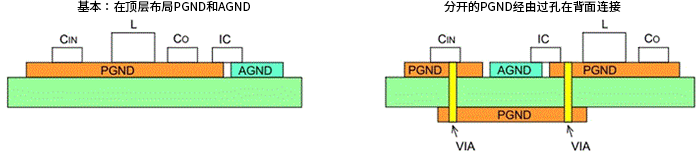

如何使用带有模拟接地层(AGND)和功率接地层(PGND)的开关稳压器?这是许多开发人员在设计开关电源时会问的一个问题。一些开发人员已习惯于处理数字接地层和模拟接地层;然而,涉及到功率GND时,他们的经验往往会失效。设计师通常会直接复制所选开关稳压器的电路板布局,不再思考这个问题。

2019-08-08 07:17:17

如何使用带有模拟接地层(AGND)和功率接地层(PGND)的开关稳压器?这是许多开发人员在设计开关电源时会问的一个问题。一些开发人员已习惯于处理数字接地层和模拟接地层;然而,涉及到功率GND时,他们的经验往往会失效。设计师通常会直接复制所选开关稳压器的电路板布局,不再思考这个问题。

2019-08-08 07:20:21

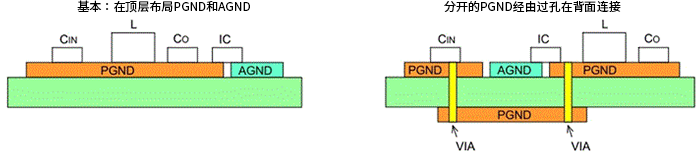

过孔连在一起也会有帮助。图3显示一个4层 PCB设计的顶层、第三层和第四层上均分布有PGND层。 图3. 截面图:连接PGND层以改善散热这种多接地层方法能够隔离对噪声敏感的信号。如图2所 示,补偿器

2021-06-25 06:00:00

问题如何使用带有模拟接地层 (AGND) 和功率接地层 (PGND) 的开关稳压器?这是许多开发人员在设计开关电源时会问的一个问题。一些开发人员已习惯于处理数字接地层和模拟接地层;然而,涉及到功率

2019-05-27 02:59:27

混合信号系统接地常用的术语和接地层,并介绍划分方法

2021-04-07 06:08:45

多层PCB通常包括一对或多对电压和接地层。电源层的功能等同于一个低电感的电容器,能够约束在元件和信道上产生的RF电容。机壳一般会有多个接地点连接到接地层,有助于减小板子的机壳和板间、板中的电压

2018-11-23 16:05:28

,模拟与数字接地层间的任何噪声均可降低转换器数字接口上的噪声裕量。由于数字噪声抗扰度在数百或数千毫伏水平,因此一般不太可能有问题。模拟接地层噪声通常不高,但如果数字接地层上的噪声(相对于模拟接地层

2018-10-19 10:40:59

某种程度上缓解上述问题。图4. 模拟电路和数字电路使用单点接地可降低高噪声数字电路引起的误差效应。接地层在当今系统中必不可少在无焊试验板中,甚至在图3所示的采用总线结构的电路板中,能够用来降低接地阻抗

2020-04-29 08:45:31

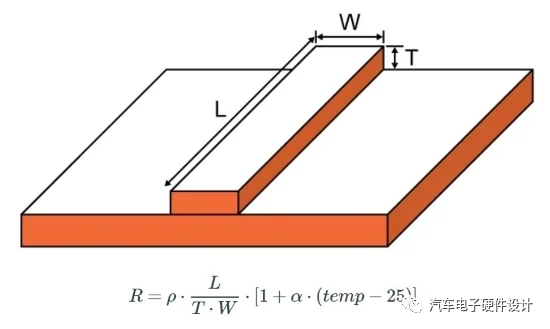

。 减小的返回路径电阻是将接地层集成到PCB中的根本好处。它减少了由返回电流变化引起的噪声,并建立了更均匀的接地电压(因为更少的电阻意味着更少的电压降落在接地网的物理分离部分之间)。通过将整个层接地

2023-04-14 16:32:11

问:使用高速转换器时,有哪些重要的PCB布局布线规则? 答:本RAQ的第一部分讨论了为什么AGND和DGND接地层未必一定分离,除非设计的具体情况要求您必须这么做。第二部分讨论印刷电路板(PCB

2018-09-12 15:05:36

分离的接地层上。最终,PCB上往往会有一个连接点成为返回电流通过而不会导致性能降低的最佳位置。此连接点通常位于转换器附近或下方。 设计电源层时,应使用这些层可以使用的所有铜线。如果可能,请勿让这些层

2018-09-12 15:04:59

PCB设计考虑EMC的接地技巧

PCB设计中,接地是抑制噪声和防止干扰的重要措施。根据电路的不同,有不同的接地方法,只有正确

2009-11-17 09:10:49 1326

1326 如何使用带有模拟接地层(AGND)和功率接地层(PGND)的开关稳压器?这是许多开发人员在设计开关电源时会问的一个问题。一些开发人员已习惯于处理数字接地层和模拟接地层;然而,涉及到功率GND时,他们的经验往往会失效。设计师通常会直接复制所选开关稳压器的电路板布局,不再思考这个问题。

2019-04-10 10:44:23 3438

3438

PCB设计中,接地是抑制噪声和防止干扰的重要措施。

2019-10-25 17:22:07 2777

2777 中间地层分割处理后,Top layer 和 Bottom layer作敷铜处理的必要性就降低了;如果要作,也需要映射中间地层分割作同样的Top和Bottom敷铜分割。

2020-03-26 15:16:33 5069

5069 的空间,可优化组件的位置,并提供足够的接地层以降低噪声。 结果,多层 PCB 趋于更紧凑,从而使设计人员能够将更多功能集成到更小的外形尺寸中,而在当今世界中,对更小,更强大的电子产品的需求一直在增长,这是至关重要的元素。 但是,尽管与单层板相比,这些多层板

2020-09-18 23:43:59 2718

2718 大多数ADC、DAC和其他混合信号器件数据手册是针对单个PCB讨论接地,通常是制造商自己的评估板。将这些原理应用于多卡或多ADC/DAC系统时,就会让人感觉困惑茫然。通常建议将PCB接地层分为模拟

2021-01-03 17:49:00 590

590

这样就基本在混合信号器件上产生了系统“星型”接地。所有高噪声数字电流通过数字电源流入数字接地层,再返回数字电源;与电路板敏感的模拟部分隔离开。系统星型接地结构出现在混合信号器件中模拟和数字接地层连接在一起的位置。

2021-01-07 16:04:24 1747

1747

你平时是如何使用带有模拟接地层(AGND)和功率接地层(PGND)的开关稳压器的?如果习惯于处理数字接地层和模拟接地层,在涉及功率GND时,你有木有手足无措的感觉呢?

PGND是较高脉冲电流

2022-02-22 11:32:19 912

912

本文讨论了适当的接地技术在PCB设计中的重要性。 我不否认可以在不使用接地层的情况下设计PCB,并且在许多情况下,您可以通过这种方式创建功能齐全的电路板(或者至少在良好的环境中运行时可以发挥全部功能

2021-01-26 10:35:22 2673

2673

你平时是如何使用带有模拟接地层(AGND)和功率接地层(PGND)的开关稳压器的?如果习惯于处理数字接地层和模拟接地层,在涉及功率GND时,你有木有手足无措的感觉呢?

PGND是较高脉冲电流

2021-02-21 06:00:18 9

9 本文要点 接地噪声是 PCB 上可能出现的多类信号干扰的总称,所有这些干扰类型都会影响 PCB 的工作方式。 接地噪声会带来信号完整性问题和性能问题,最终会导致 PCB 出现故障。 采用新型基板

2022-05-07 17:43:37 4852

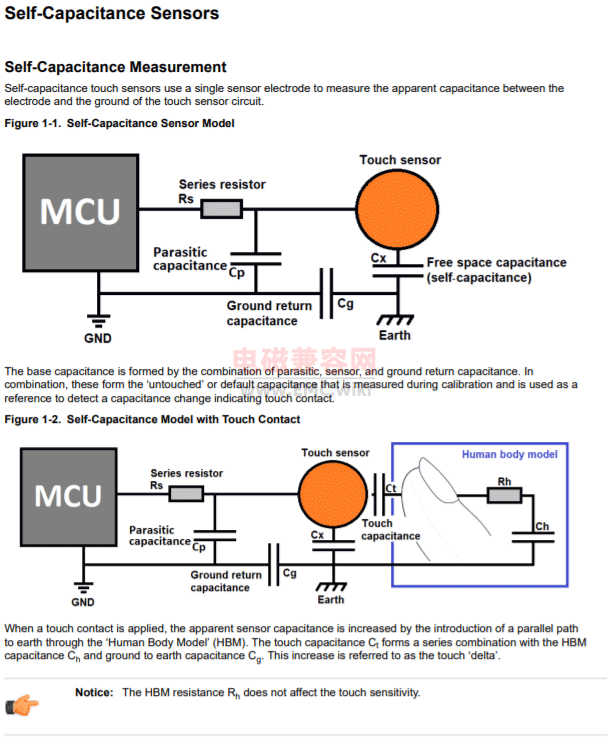

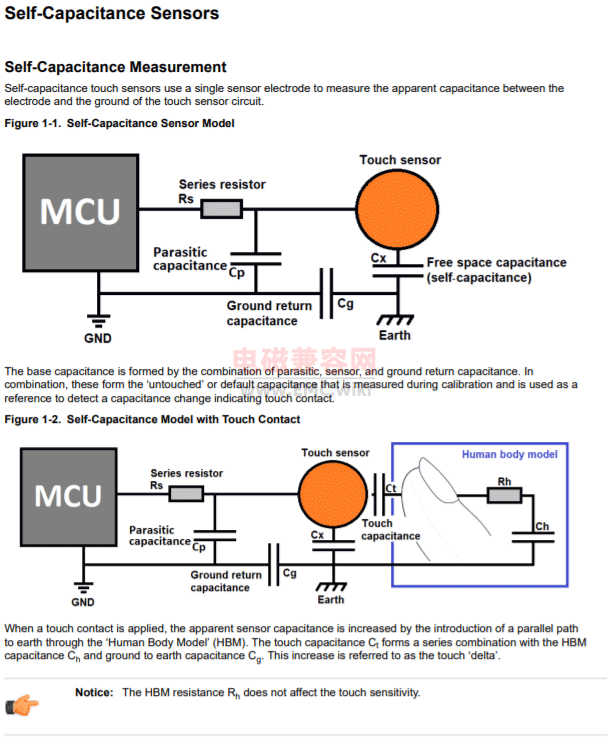

4852 拥有电容感应式触摸按键设备会发出可导致电磁兼容性(EMC)问题的辐射,可使用下列方法来降低辐射干扰。接地层:通常情况下,在 PCB 板上正确放置接地层会降低 RF 辐射和干扰。但是,接近电容触摸

2023-04-10 09:55:20 6039

6039

如果电源接地分开并经由过孔连接在背面,则受过孔电阻和电感器的影响,损耗和噪声将会恶化。旨在屏蔽、散热及减少直流损耗而在内层或背面设置接地层的做法,只是辅助接地。

2023-04-29 17:22:00 246

246

多层板的接地平面可以显着改善电路的噪声性能。对于双面板,我们通常不能有地平面,我们预计会有更多的噪声和辐射。由于这个限制,我们更喜欢多层板,除非成本目标迫使我们使用两层板。

2023-04-29 17:26:00 1093

1093

PCB 接地是PCB Layout工程师一直都会关注的问题,例如:如何在板上规划有效地接地系统,是将模拟、数字、电源地等所有地单独布线还是单点一起布线?如何消除电路板上的接地环路?

2023-05-10 10:35:41 2001

2001

如果电源接地分开并经由过孔连接在背面,则受过孔电阻和电感器的影响,损耗和噪声将会恶化。旨在屏蔽、散热及减少直流损耗而在内层或背面设置接地层的做法,只是辅助接地。

2023-06-06 11:05:52 150

150

如果电源接地分开并经由过孔连接在背面,则受过孔电阻和电感器的影响,损耗和噪声将会恶化。旨在屏蔽、散热及减少直流损耗而在内层或背面设置接地层的做法,只是辅助接地。

2023-06-24 10:33:00 604

604

本文要点接地噪声是PCB上可能出现的多类信号干扰的总称,所有这些干扰类型都会影响PCB的工作方式。接地噪声会带来信号完整性问题和性能问题,最终会导致PCB出现故障。采用新型基板和铜连接器制作PCB

2022-05-24 16:24:28 514

514

降低PCB设计中噪声与电磁干扰24条

2023-07-04 16:57:23 327

327 多层PCB通常包括一对或多对电压和接地层。电源层的功能等同于一个低电感的电容器,能够约束在元件和信道上产生的RF电容。机壳一般会有多个接地点连接到接地层,有助于减小板子的机壳和板间、板中的电压梯度。电压梯度是共模射频场的主要来源,也是机壳到地的射频电源的来源。

2023-08-24 14:11:00 416

416

地弹是一种噪声,当 PCB 接地和芯片封装接地处于不同电压时,晶体管开关器件会出现这种噪声。

2023-09-07 10:07:53 867

867

大多数 ADC、DAC 和其他混合信号器件数据手册是针对单个 PCB 讨论接地,通常是制造商自己的评估板。将这些原理应用于多卡或多 ADC/DAC 系统时,就会让人感觉困惑茫然。通常建议将 PCB

2023-10-20 14:37:18 205

205

一个例子是,在一些应用中,为了符合传统设计要求,必须将脏乱的总线电源或数字电路放在某些区域,同时还受尺寸限制的影响,使得电路板无法实现良好的布局分割,在这种情况下,分离接地层是实现良好性能的关键。

2023-11-06 15:14:13 135

135 PDS的设计目标是将响应电源电流需求而产生的电压纹波降至。所有电路都需要电流,有些电路需求量较大,有些电路则需要以较快的速率提供电流。采用充分去耦的低阻抗电源层或接地层以及良好的PCB层叠,可以将因电路的电流需求而产生的电压纹波降至。

2023-11-06 15:16:02 184

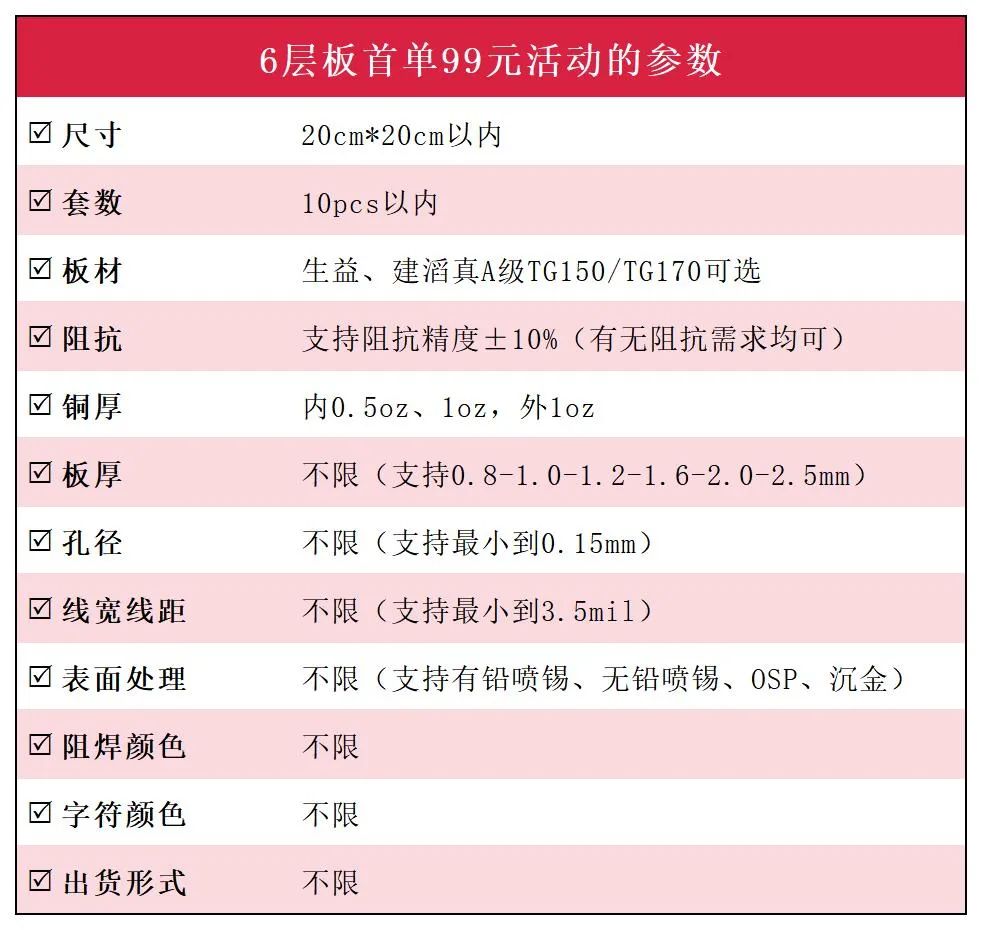

184 提到6层板分层布局,一般业内主流会推荐这个设计方案: 【电源层数1,地层数2,信号层数3】 活动详情: ①、在华秋PCB未付款过6层板订单的用户皆可参与; ②、6层板99元特惠订单,需符合以下活动

2023-12-07 10:40:02 161

161

提到6层板分层布局,一般业内主流会推荐这个设计方案:【电源层数1,地层数2,信号层数3】但从成本方面考虑,我们会希望板子布局越多线路越经济,即信号层越多成本越低。因此,在设计6层板时,电源层和接地层

2023-12-08 11:11:09 226

226

降低EMI的一个重要途径是设计PCB接地层。步是使PCB电路板总面积内的接地面积尽可能大,这样可以减少发射、串扰和噪声。将每个元器件连接到接地点或接地层时必须特别小心,如果不这样做,就不能充分利用可靠的接地层的中和效果。

2024-01-02 15:29:31 82

82 降低EMI的一个重要途径是设计PCB接地层。步是使PCB电路板总面积内的接地面积尽可能大,这样可以减少发射、串扰和噪声。将每个元器件连接到接地点或接地层时必须特别小心,如果不这样做,就不能充分利用可靠的接地层的中和效果。

2024-01-16 15:17:26 151

151

电子发烧友App

电子发烧友App

评论