请教各位大师:FPGA 设计的一块8层板,2层电源,2层地,4sig。 FPGA 信号有80M. 想问一下怎么叠层合适? 电源层有很多空余位置布电源好,还是布地线好?信号层的空余地方要布地线吗? 谢谢。

2015-07-18 11:07:25

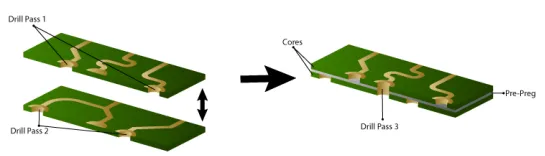

4.3.3 实验设计3:4层PCB 本章将考虑4层PCB叠层的几种不同变体。这些变化中最简单的是基于实验设计2层叠层(第4.3.2节),外加两个额外的内部信号层。假设附加层主要由许多较薄的信号

2023-04-20 17:10:43

的放置顺序。在这一步骤中,需要考虑的因素主要有以下两点。(1)特殊信号层的分布。(2)电源层和地层的分布。总的原则有以下几条。(1)信号层应该与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为

2015-03-06 11:02:46

特性,以及对电磁辐射的抑制,甚至在抵抗物理机械损伤的能力上都明显优于低层数的PCB。一般情况下均按以下原则进行叠层设计:满足信号的特征阻抗要求;满足信号回路最小化原则;满足最小化PCB内的信号干扰要求

2016-05-17 22:04:05

。 对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题; 层的排布一般原则: 1、确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越

2018-09-17 17:41:10

叠结构的相关内容。对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题。层的排布一般原则:1、确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数

2016-08-24 17:28:39

本帖最后由 lee_st 于 2017-10-31 08:48 编辑

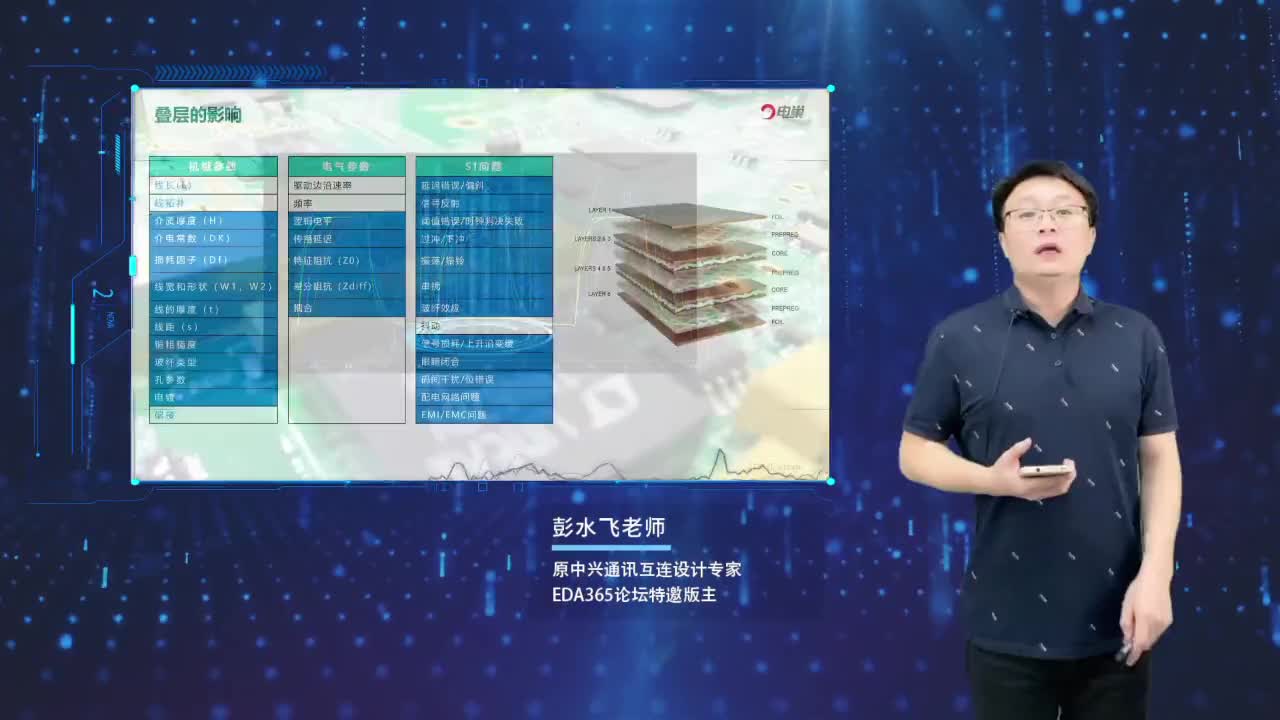

PCB叠层设计及阻抗计算

2017-10-21 20:44:57

PCB叠层设计及阻抗计算

2017-09-28 15:13:07

PCB叠层设计及阻抗计算

2016-06-02 17:13:08

。对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题; 层的排布一般原则: 1、确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于

2018-09-18 15:12:16

对于如何选择设计用几层板和用什么方式的叠层,要根据板上信号网络的数量,器件密度,PIN密度,信号的频率,板的大小等许多因素。对于这些因素我们要综合考虑。对于信号网络的数量越多,器件密度越大,PIN

2020-01-03 08:58:20

、EMC、制造成本等要求有关。对于大多数的设计,PCB的性能要求、目标成本、制造技术和系统的复杂程度等因素存在许多相互冲突的要求,PCB的叠层设计通常是在考虑各方面的因素后折中决定的。高速数字电路和射须电路通常采用多层板设计。

2019-09-17 14:11:49

。 PCB的EMC设计的关键,是尽可能减小回流面积,让回流路径按照我们设计的方向流动。而层的设计是PCB的基础,如何做好PCB层设计才能让PCB的EMC效果最优呢? PCB层的设计思路: PCB叠层EMC

2018-08-08 17:18:29

选择是由电路板设计师决定的,这就是所谓的“PCB层叠设计”。? 正文 ?俗话说的好,最好的实践也是建立在理论知识的基础上,板儿妹在本节中重点给大家分享关于PCB叠层设计概念性的理论知识以及层叠结构

2017-03-01 10:02:08

现在在用AD2018AD2018在PCB板可以提供15个机械层,有的机械层(比如第一层)是元器件安装层,有的机械层(比如第二层)是元件3D层,有的机械层(比如第三层)是元器件外部边框层,有如下两个

2019-05-27 10:17:58

L1和L4信号线,L2地线层,L3电源层。如果L4层上的元器件较少,是主布线层,那么将L2改为电源,L3为地,效果可能会更好些。

2019-05-24 06:01:16

L1和L4信号线,L2地线层,L3电源层。如果L4层上的元器件较少,是主布线层,那么将L2改为电源,L3为地,效果可能会更好些。 6层板:L2和L5为地线层和电源层,其它为信号层。

2019-05-21 10:19:01

4.3.4 实验设计4:4层PCB 将考虑的第二层4层叠层与图8相似,只是第2层已被100%覆盖的平面所取代。这可能代表一个内部的接地平面平面。否则,实验设计将与第2部分相同。结果如图10所示

2023-04-20 17:16:18

4.4.3 实验设计9:通用的4层PCB 通过增加两个内部信号层,实验设计6的2层叠加现在将增加到4层。与以前一样,假设这些层主要由许多较薄的信号走线组成,而不是大面积连续铺铜。 模拟的内部

2023-04-21 15:04:26

PCB电源层走电源是导线走,还是整层铺铜呢?

2011-03-24 14:02:57

PCB线路板叠层设计要注意哪些问题呢?

2021-03-29 08:12:19

PCB设计中叠层算阻抗时需注意哪些事项?

2019-05-16 11:06:01

在高速PCB设计流程里,叠层设计和阻抗计算是登顶的第一梯。阻抗计算方法很成熟,不同软件的计算差别不大,相对而言比较繁琐,阻抗计算和工艺制程之间的一些"权衡的艺术",主要是为了达到

2018-01-22 14:41:32

是电路板设计的一个重要指标,特别是在高频电 路的PCB设计中,必须考虑导线的特性阻抗和器件或信号所要求的特性阻抗是否一致,是否匹配。这就涉及到两个概念:阻抗控制与阻抗匹配,本文重点讨论阻抗控制和叠层设计的问题。

2019-05-30 07:18:53

完美的叠层图,板框图

2019-03-19 09:54:23

本帖最后由 yfsjdianzi 于 2014-5-11 14:23 编辑

叠层电感也就是非绕线式电感,是电感分类的其中一类。外形尺寸小,闭合电路,无交互干扰,适合于高密度安装,无方

2014-05-10 20:04:18

叠层电感在现实中应用也十分广泛,目前叠层电感类产品被广泛用于笔记本电脑数位电视,数位录放影机,列表机,硬式磁碟机,个人电脑和其安一般消费性及电脑主品上输入、输出线路之杂讯消除。

2019-10-17 09:00:27

`叠层电感磁珠可靠性实验项目有哪些?`

2011-10-16 19:34:50

叠层电池的升压电路

2019-11-07 03:31:57

。关于电容器与电感的话题,我们先从电容器开始。近年来,从电源IC的应用电路例来看,推荐称为“MLCC(Multilayer Ceramic Chip Capacitor)”的叠层陶瓷电容器的越来越多。我想

2018-12-03 14:35:18

的放置顺序。在这一步骤中,需要考虑的因素主要有以下两点。(1)特殊信号层的分布。(2)电源层和地层的分布。总的原则有以下几条。(1)信号层应该与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为

2015-02-11 16:25:13

在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。

建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜

2023-12-25 13:46:25

在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。

建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜

2023-12-25 13:48:49

不慌不忙的打开PCB文件,雷豹见Chris直接跳过了检查PCB上的走线这一步,径直的打开了叠层设置,然后给雷豹指一下这个地方,没错,指的就是下面这个红框框的地方。

雷豹感觉好像懂了一点了,原来该客户

2023-06-02 15:32:02

allegro16.5多层PCB板的叠层设计时,内电层设计为正片或负片的选项不知道怎样处理,我原来用的是allegro15.7,allegro15.7设置内电层时,它有个选项,可选为正片或负片,但allegro16.5没看到这个选项,求教知道的人指导一下

2015-09-20 18:45:24

在设计多层PCB时,叠层是必须得考虑的问题,层分布好坏直接影响产品的性能。下面推荐几个使用最稳定的叠层结构:

2020-06-10 20:15:31

您还在为阻抗设计头疼吗?这里有齐全的阻抗参数及叠层结构。有它您无需再去仿真,我们已将其一一列出,如 90ohm线宽线距为7/6mil 或 5/4mil ,结合布线空间选择对应的线宽线距。

2020-06-10 20:54:11

PCB叠层设计的原则简介:多层PCB通常用于高速、高性能的系统,其中一些层用于电源或地参考平面,这些平面通常是没有分割的实体平面。无论这些层做什么用途,电压为多少,它们将作为与之相邻的信号走线的电流

2021-03-26 18:00:20

`高速数字系统设计中,地、电源平面和叠层设计的一些探讨。`

2021-04-02 11:05:42

多层板叠层设计规则,单层、双层PCB板的叠层,推荐设计方式,设计方案讲解。

2021-03-29 11:58:10

`完整的参考平面可以用来保证回路的连续性,宽的线宽可以降低信号的导体损耗,背钻工艺可以减小过孔的Stub,提高信号的完整性,但是这样往往会导致成本的增加。本文章将介绍两种六层板叠层结构。`

2021-03-30 10:42:55

常见的PCB叠层结构,四层板、六层板、八层板十层板叠层设计及注意事项。

2021-03-29 11:49:35

阻抗的电流返回路径最重要的就是合理规划这些参考平面的设计。图1所示为一种典型多层PCB叠层配置。图1 一种典型多层PCB叠层配置回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:18:25

在电路板设计上创建PCB叠层也会遇到类似情况:我们可能不了解最适宜的PCB材料,也不知道如何有效地构建叠层。在作出决定之前,清楚了解我们的需求才能对设计最为有利。优化设计意味着梳理可供考虑和选择

2021-08-04 10:13:17

手机PCB Layout层数选择与叠层设计方案剖析。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:10:24

本文主要介绍多层PCB设计叠层的基础知识,包括叠层结构的排布一般原则,常用的叠层结构,叠层结构的改善案例分析。回复帖子查看资料下载链接:[hide][/hide]

2021-08-04 10:06:58

4.3.6 实验设计6:一个4层的PCB板与热散热过孔 为了完整性,“4层+散热过孔”结构也被实验设计为1层铜的几个尺寸,并再次叠层,如图8所示。结果如图13所示。 (1)单层板。 (2

2023-04-21 14:51:37

本帖最后由 张飞电子学院吕布 于 2021-4-12 16:36 编辑

一到八层电路板的叠层设计方式 电路板的叠层安排是对 PCB 的整个系统设计的基础。叠层设计如有缺陷,将最终影响到整机

2021-04-12 16:35:28

请问一下为什么我的叠层管理器打不开。。

2019-09-02 01:15:06

PCB设计时,在那种情况下会使用跨层盲孔(Skip via)的设计?一般叠构和孔径怎么设计?

2023-11-09 16:21:10

高速叠层设计原则:考虑因素:BGA 扇出、局部布线密度、阻抗控制、顾客要求、SI/PI考虑、成本、电设计源分割、板厚、板厚与孔径比工艺要求:对称性表层与内层不要选择4.0mil以下介质不要选

2022-03-02 06:09:06

PCB设计中层叠结构的设计建议:1、PCB叠层方式推荐为Foil叠法2、尽可能减少PP片和CORE型号及种类在同一层叠中的使用(每层介质不超过3张PP叠层)3、两层之间PP介质厚度不要超过21MIL

2017-01-16 11:40:35

多层PCB如何定义叠层呢?

2023-04-11 14:53:59

搞定叠层,你的PCB设计也可以很高级

2020-12-28 06:44:43

射频板设计PCB叠层时,推荐使用四层板结构,层设置架构如下【Top layer】射频IC和元件、射频传输线、天线、去耦电容和其他信号线,【Layer 2】地平面【Layer 3】电源平面

2022-11-07 20:48:45

普通铁氧体电感、叠层扼流电感及叠层功率电感有何区别?

2011-10-16 20:20:01

贴片电感从制造工艺上可分为:绕线型、叠层型、编织型和薄膜片式电感器,常用的为绕线型电感和叠层型电感,绕线型电感是传统绕线电感器小型化的产物,而叠层型电感采用多层印刷技术和叠层生产工艺制作,体积比绕线

2020-06-02 09:33:23

在片式电容器里用得最多的就是片式叠层陶瓷介质电容器。片式叠层陶瓷电容器(MLCC),简称片式叠层电容器(或进一步简称为片式电容器),是由印好电极(内电极)的陶瓷介质膜片以错位的方式叠合起来,经过

2018-08-06 17:33:24

`叠层电感也就是非绕线式电感,叠层电感是电感按结构不同对电感进行分类的其中一类。特 性: 1.外形尺寸小。 2.闭合电路,无交互干扰,适合于高密度安装。 3.无方向性,规范化的自动贴片安装外形

2013-08-29 17:41:52

电路板的叠层设计是对PCB的整个系统设计的基础,叠层设计若有缺陷,将最终影响到整机的EMC性能。叠层设计是一个复杂的,严谨过程,当然,设计开发,没必要从零开始经过一系列的复杂计算和仿真,来确定设计方案是否合适,仅需要总结前人的经验,选择合适系统的叠层方案。

2021-11-12 07:59:58

画ddr的八层板子这样叠层可以吗?这两个哪个比较好?@chenzhouyu @郑振宇_Kivy @cesc

2019-05-29 03:20:49

工作,其他7组光口通信正常。1、问题点确认根据客户端提供的信息,确认为L6层光口8与芯片8之间的两条差分阻抗线调试不通;2、客户提供的叠构与设计要求改善措施 影响阻抗信号因素分析: 线路图分析:客户

2019-05-29 08:11:41

的应用:该产品被广泛用于微型电视、液晶电视、摄影机、便携式VRC、汽车音响、薄型收音机、电视调谐器、行动电话等。叠层电感与绕线电感叠层的散热性更好,ESR值更小。但耐电流较绕线小。绕线的散热性不如叠层

2012-08-04 11:32:03

实现,在向里的2-3圈Pin需要就地打孔扇出,走线基本上要走L3或L4或Bottom层。4、对此运行400MHz的高速数字电路系统多层板,应不应当进行信号完整性分析及如何分析。5、PCB的叠层顺序。6

2011-10-21 09:48:17

我正在设计一个带有芯片天线的nrf52832 SoC的四层叠层PCB(2450AT18B100:http://www.kynix.com/Detail/744089

2018-10-24 14:34:50

RT,现有一个项目,需要布置八层板,两层信号,因整块板的平均功率达50W,需要布置两层电源,其它层全铺地,最佳的叠层顺序是怎么样较好。

2019-09-24 05:07:43

多层印制板设计基础PCB板的堆叠与分层

2021-03-10 07:06:58

八层板常用的叠层方式有哪几种?

2021-04-25 07:16:59

贴片叠层电感和贴片功率电感的作用和应用有什么不同呢?

2015-09-15 16:27:53

。 对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题; 层的排布一般原则: 1、确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数

2016-08-23 10:02:30

这个叠层图是什么意思呢

2015-06-11 09:23:35

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在

2019-05-30 07:20:55

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在

2022-03-07 16:04:23

在《PCB的筋骨皮》一文中,我们提出了当板厚在1.6mm及以上时,怎样避免使用假八层的叠层,而导致PCB成本增加的问题。感觉大家的回答很踊跃哈,看来这个问题还是比较典型的。本来想截取一些回答放在

2019-05-29 07:26:53

。下面以一个12层的PCB来说明多层PCB的结构和布局,如图6-14所示,其层的用途分配为“T—P—S—P—s—P—S—P—S—s—P—B”。下面是一些关于多层PCB叠层设计的原则。 · 为参考平面

2018-11-27 15:14:59

高速PCB设计的叠层问题

2009-05-16 20:51:30

的设计要求,结合笔者设计经验,按照PCB设计流程,对PCB设计中需要重点关注的设计原则进行了归类。详细阐述了PCB的叠层设计、元器件布局、接地、PCB布线等高速PCB设计中需要遵循的设计原则和设计方法以及需要注意的问题等。按照笔者所述方法设计的高速复杂数模混合电路,其地噪很低,电磁兼容性很好。

2012-03-31 14:29:39

介电常数、及叠层结构。

叠层设计基本原则

对于PCB板厂,一般会跟2-3家材料品牌厂家合作,选择几种类型的PP,及芯板铜箔做为PCB的原材料,根据工厂的制程能力、生产工艺来做叠层设计,并匹配相应阻抗。通常

2023-05-26 11:30:36

电子发烧友App

电子发烧友App

评论