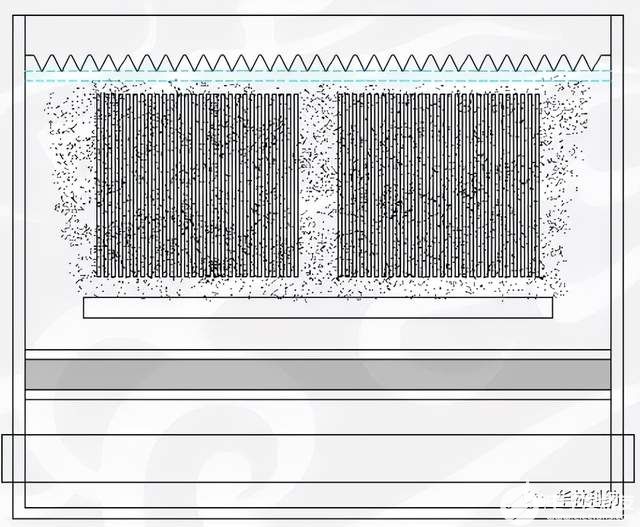

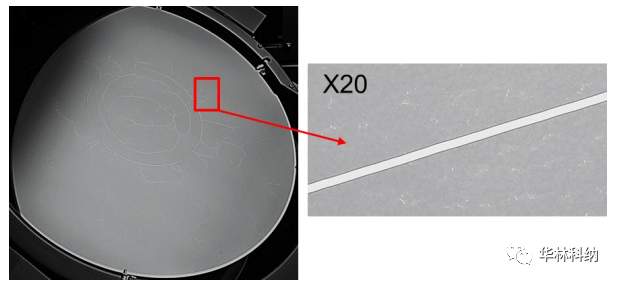

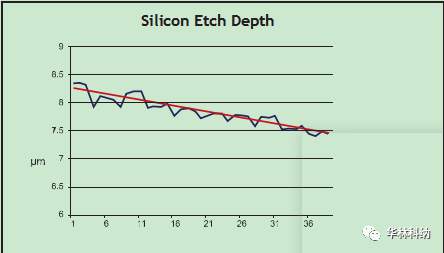

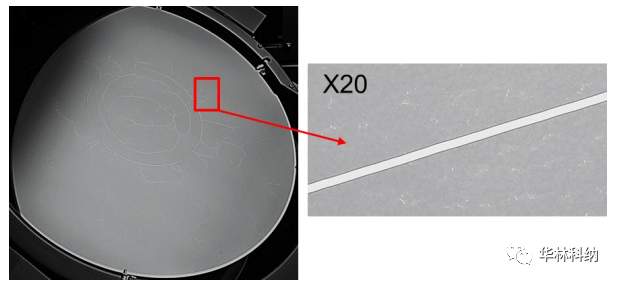

是翻转。翻转晶片进行蚀刻工艺的话,蚀刻均匀度最好在1%以下。因此,如果一面进行工程,工程时间将增加一倍。为了减少工序时间,对在进行顶面工序的同时进行背面工序的方法进行了评价。本研究旨在制作可安装在晶片背面的蚀刻喷

2022-01-05 14:23:20 1067

1067

在本研究中,我们设计了一个150mm晶片的湿蚀刻槽来防止硅片的背面蚀刻,并演示了优化的工艺配方,使各向异性湿蚀刻的背面没有任何损伤,我们还提出了300mm晶圆处理用湿浴槽的设计,作为一种很有前途的工艺发展。

2022-03-28 11:01:49 1943

1943

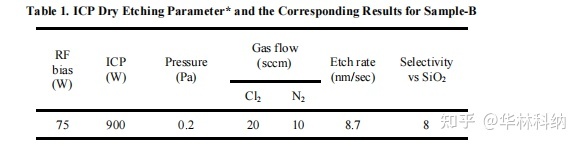

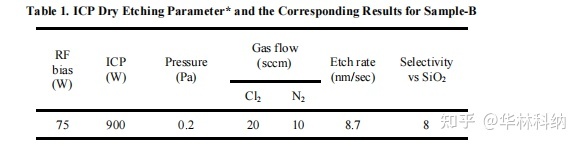

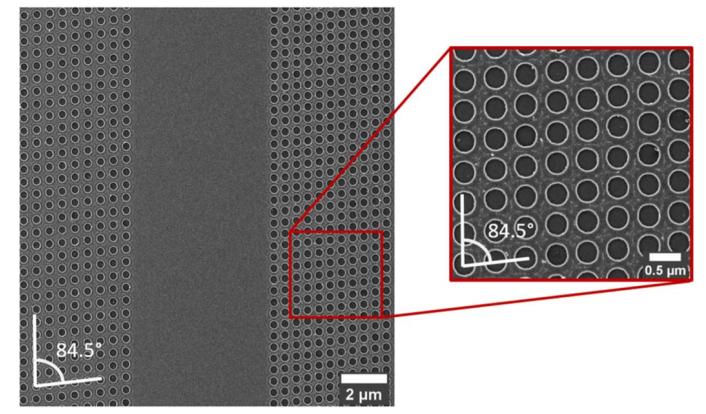

基本化学成分以Cl2为基础,外加用于侧壁钝化的N2。优化的ICP蚀刻工艺能够产生具有光滑侧壁的高纵横比结构。使用670nm波长的激光进行原位反射监测,以高精度在材料界面停止蚀刻。考虑到在基于GaSb

2022-05-11 14:00:42 1024

1024

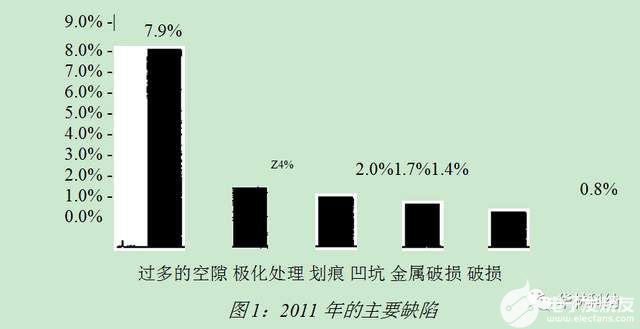

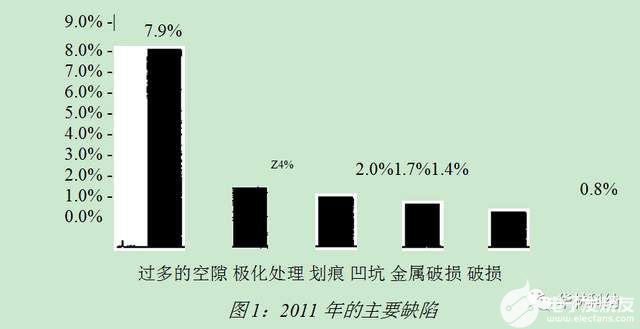

引言 本研究针对12英寸晶圆厂近期技术开发过程中后端一体化(AIO)蚀刻工艺导致的图案失效缺陷。AIO蚀刻直接限定了沟槽和通孔的形状,然而,包括层间介电膜的沉积、金属硬掩模和湿法清洗的那些先前的工艺

2022-06-01 15:55:46 7809

7809

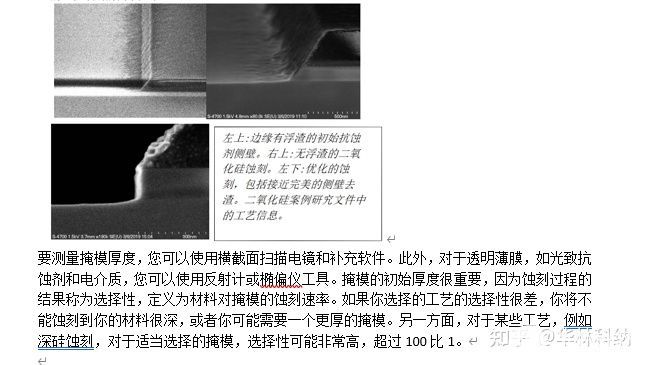

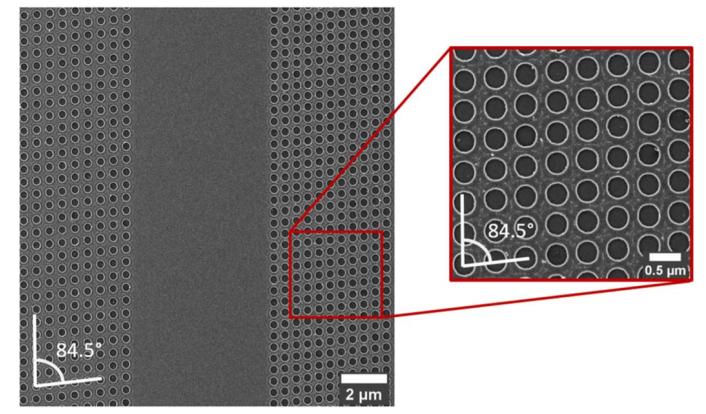

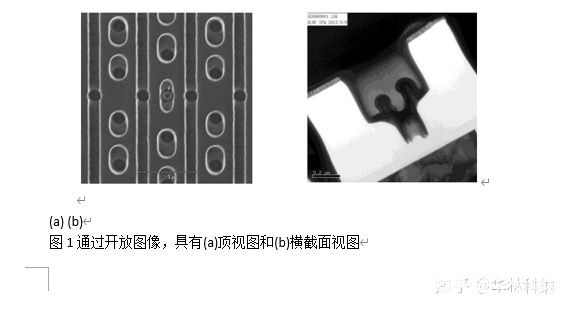

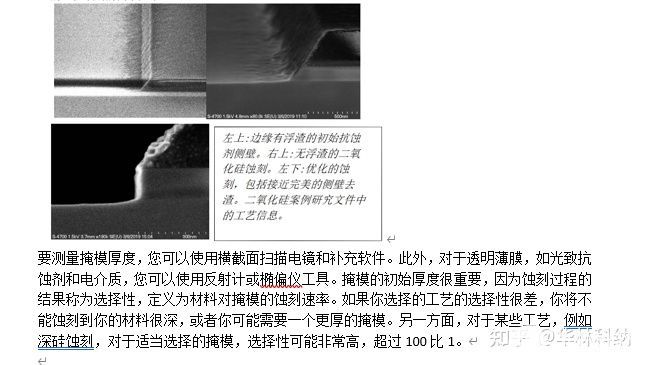

初始屏蔽检查 对蚀刻工艺的良好理解始于理解初始掩模轮廓,无论是光致抗蚀剂还是硬掩模。掩模的重要参数是厚度和侧壁角度。如果可能,对横截面进行SEM检查,以确定适用于您的蚀刻步骤的不同特征尺寸的侧壁角度

2022-06-10 16:09:33 5070

5070

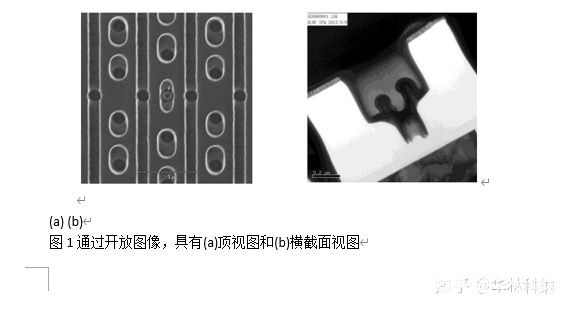

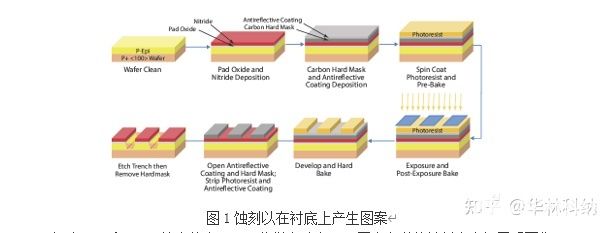

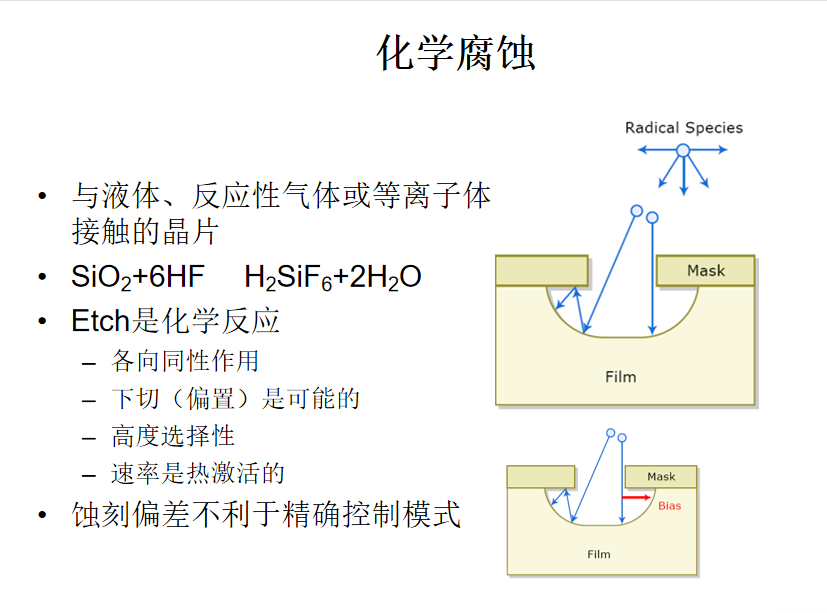

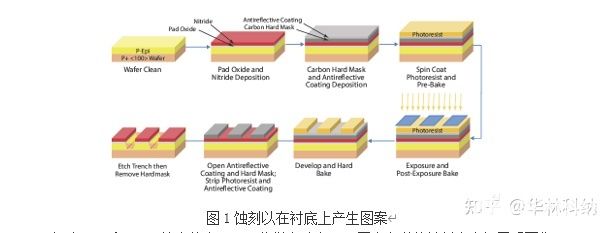

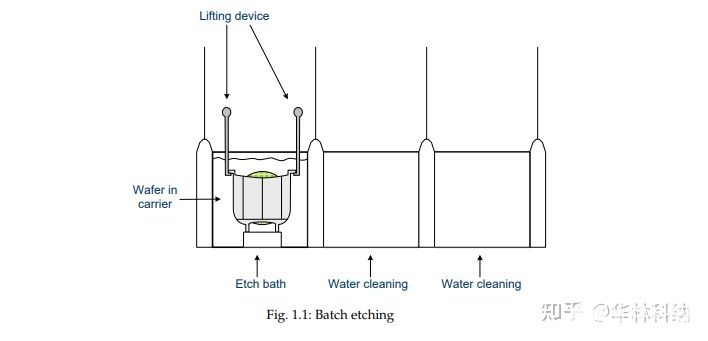

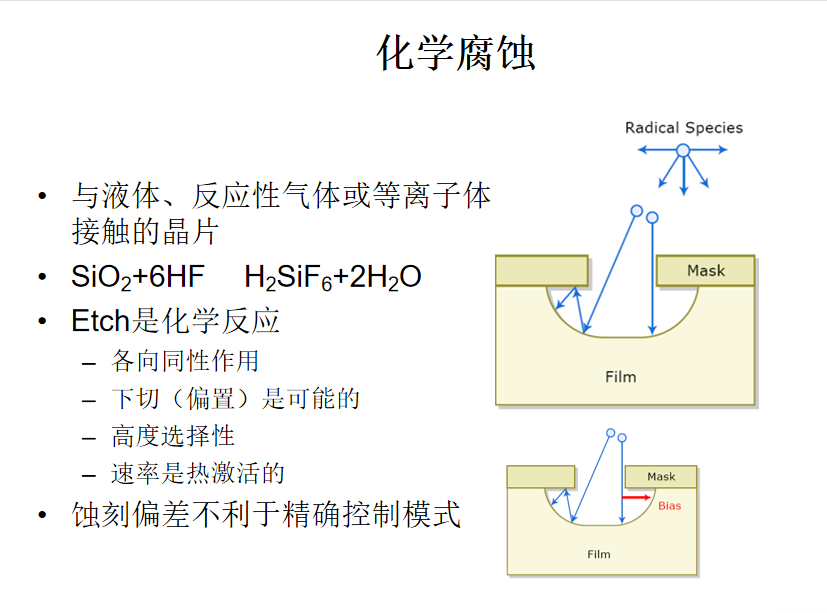

在半导体器件制造中,蚀刻指的是从衬底上的薄膜选择性去除材料并通过这种去除在衬底上产生该材料的图案的任何技术,该图案由抗蚀刻工艺的掩模限定,其产生在光刻中有详细描述,一旦掩模就位,可以通过湿法化学或“干法”物理方法对不受掩模保护的材料进行蚀刻,图1显示了这一过程的示意图。

2022-07-06 17:23:52 2866

2866

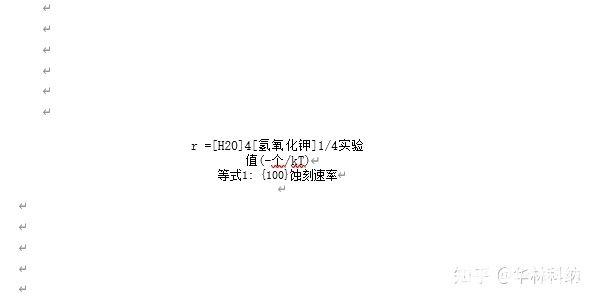

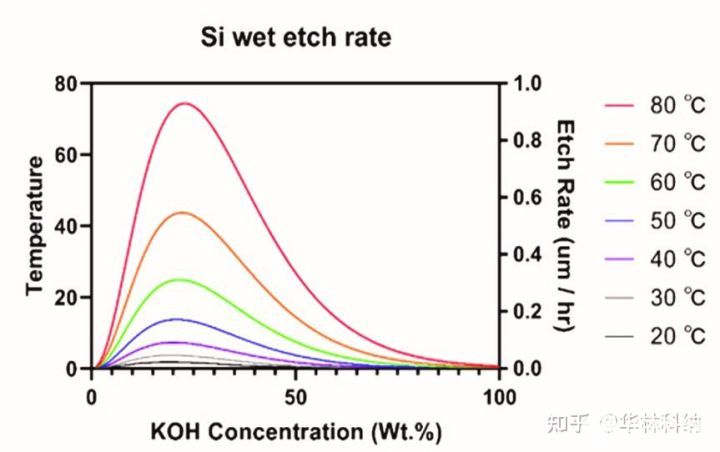

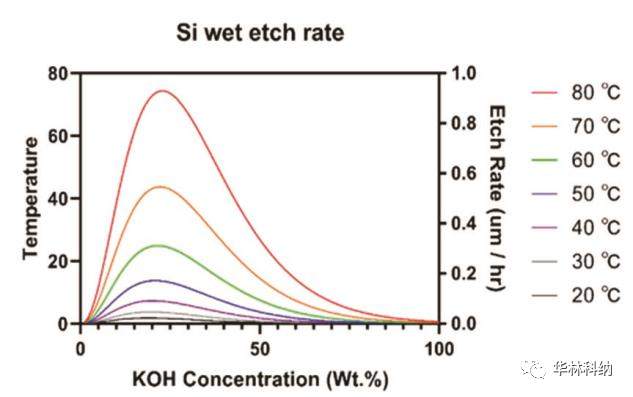

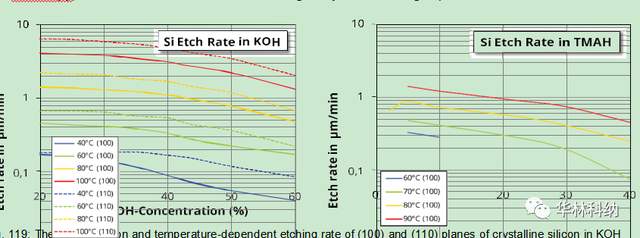

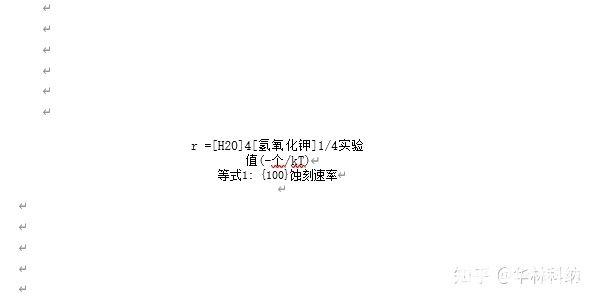

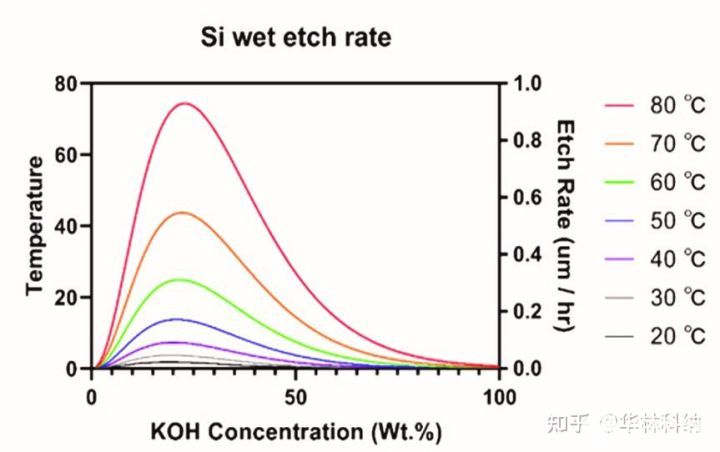

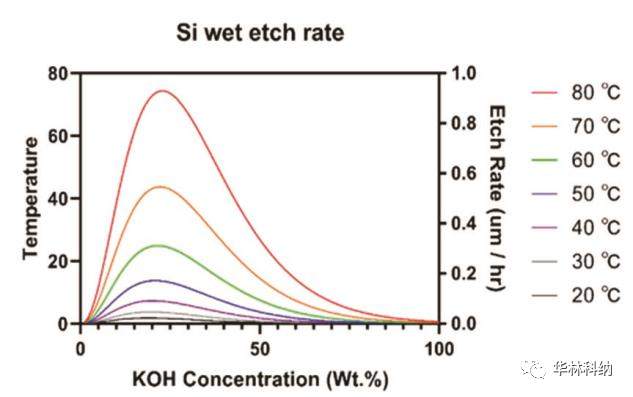

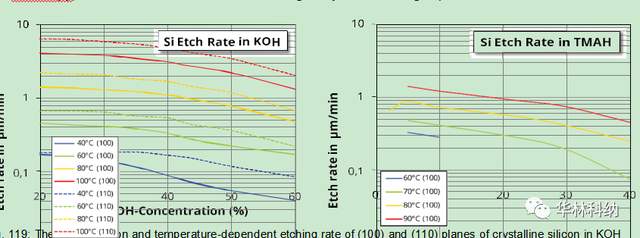

他方向上的蚀刻速度快,而各向同性蚀刻(如HF)会向所有方向侵蚀。使用KOH工艺是因为其在制造中的可重复性和均匀性,同时保持了较低的生产成本。异丙醇(IPA)经常添加到溶液中,以改变从{110}壁到{100}壁的选择性,并提高表面光滑度。 氧化物和氮化物

2022-07-14 16:06:06 2774

2774

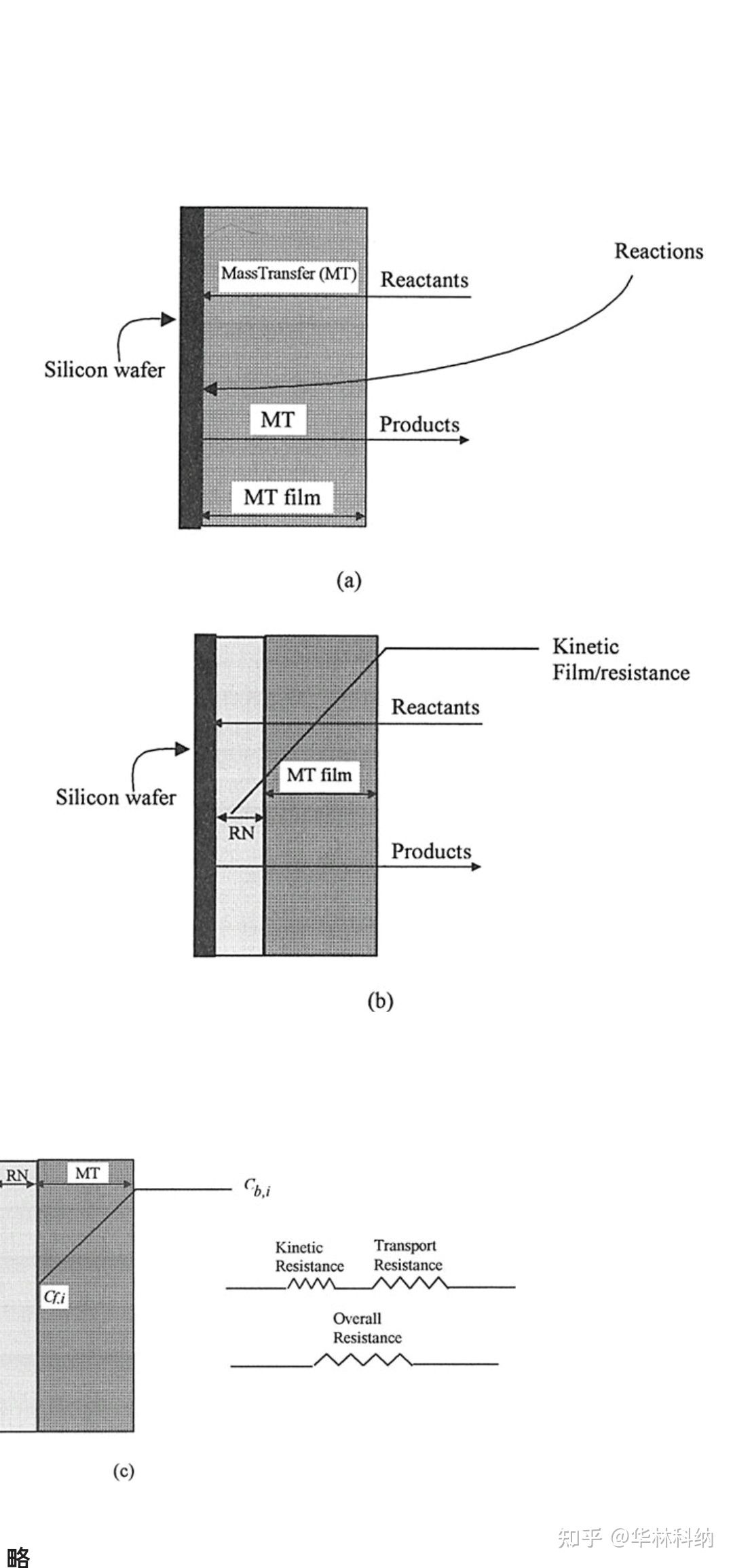

湿法蚀刻工艺的原理是利用化学溶液将固体材料转化为liquid化合物。由于采用了高选择性化学物质可以非常精确地适用于每一部电影。对于大多数解决方案选择性大于100:1。

2022-07-27 15:50:25 2109

2109

传统的光刻工艺是相对目前已经或尚未应用于集成电路产业的先进光刻工艺而言的,普遍认为 193nm 波长的 ArF 深紫外光刻工艺是分水岭(见下表)。这是因为 193nm 的光刻依靠浸没式和多重曝光技术的支撑,可以满足从 0.13um至7nm 共9个技术节点的光刻需要。

2022-10-18 11:20:29 13992

13992 反应离子蚀刻 (RIE)是一种干法蚀刻工艺,与半导体工业中使用的互补金属氧化物半导体(CMOS)方法兼容。

2023-04-14 14:26:16 1253

1253

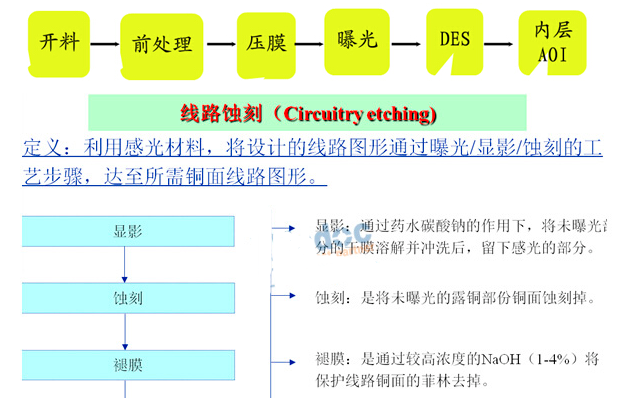

一、PCB工艺设计要考虑的基本问题

PCB的工艺设计非常重要,它关系到所设计的PCB能否高效率、低成本地制造出来。新一代的SMT装联工艺,由于其复杂性,要求设计者从一开始就必须考虑制造

2023-04-25 16:52:12

`请问PCB蚀刻工艺质量要求有哪些?`

2020-03-03 15:31:05

PCB制作工艺中的碱性氯化铜蚀刻液1.特性1)适用于图形电镀金属抗蚀层,如镀覆金、镍、锡铅合金,锡镍合金及锡的印制板的蚀刻。 2)蚀刻速率快,侧蚀小,溶铜能力高,蚀刻速率容易控制。 3)蚀刻液可以

2018-02-09 09:26:59

PCB制程中的COB工艺是什么呢?

2023-04-23 10:46:59

,通过光化学法,网印图形转移或电镀图形抗蚀层,然后蚀刻掉非图形部分的铜箔或采用机械方式去除不需要部分而制成印制电路板PCB。而减成法中主要有雕刻法和蚀刻法两种。雕刻法是用机械加工方法除去不需要的铜箔,在单

2018-09-21 16:45:08

所需的铜迹线。PCB蚀刻工艺使用高度侵蚀性的基于氨的溶液-氯化铁或盐酸来完成。两种化学品都被认为是经济和丰富的。要蚀刻您的PCB,您需要按照以下步骤进行操作:1.使用您选择的任何PCB设计软件,电路板

2020-11-03 18:45:50

,间隔宽的导线分布的部位,蚀刻就会过度。所以,这就要求设计者在电路设计时,就应首先了解工艺上的可行性,尽量做到整个板面电路图形均匀分布,导线的粗细程度应尽量相一致。特别是在制作多层印制电路板时,大面积

2018-09-11 15:19:38

,间隔宽的导线分布的部位,蚀刻就会过度。所以,这就要求设计者在电路设计时,就应首先了解工艺上的可行性,尽量做到整个板面电路图形均匀分布,导线的粗细程度应尽量相一致。特别是在制作多层印制电路板时,大面积铜箔

2013-10-31 10:52:34

导线线宽十分精细时将会产生一系列的问题。同时,侧腐蚀(见图4)会严重影响线条的均匀性。 在印制板外层电路的加工工艺中,还有另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺

2018-11-26 16:58:50

工序(底片由于划伤或者垃圾造成的问题,包括曝光机问题,曝光局部不足等),显影工序(显影不清),蚀刻工序(喷嘴压力过大,蚀刻时间过长),电镀问题(电镀不均匀,或者表面有吸附),操作不当(基本是划伤造成的)。 关键看PCB断线的形式,所以工艺工程师经验技术很重要。

2013-02-19 17:30:52

范围。 预热工艺 在选择性焊接工艺中的预热主要目的不是减少热应力,而是为了去除溶剂预干燥助焊剂,在进入焊锡波前,使得焊剂有正确的黏度。在焊接时,预热所带的热量对焊接质量的影响不是关键因素,PCB材料

2018-09-10 16:50:02

作用的添加剂的一些氨基磺酸镍镀液来镀制。我们常说的PCB镀镍有光镍和哑镍(也称低应力镍或半光亮镍),通常要求镀层均匀细致,孔隙率低,应力低,延展性好的特点。

2011-12-22 08:43:52

PCB碱性蚀刻常见问题原因及解决方法

2012-08-03 10:14:05

上 解决方法: (1)基板表面退膜不够完全,有残膜存在。 (2)全板镀铜时致使板面镀铜层厚度不均匀。 (3)板面用油墨修正或修补时沾到蚀刻机的传动的滚轮上。 (4)检查退膜工艺条件,加以调整及改进

2018-09-19 16:00:15

还提出了另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺,可以参阅内层制作工艺中的蚀刻。 目前,锡或铅锡是最常用的抗蚀层,用在氨性蚀刻剂的蚀刻工艺中。氨性蚀刻剂是普遍

2018-09-13 15:46:18

PCB选择性焊接工艺难点解析在PCB电子工业焊接工艺中,有越来越多的厂家开始把目光投向选择焊接,选择焊接可以在同一时间内完成所有的焊点,使生产成本降到最低,同时又克服了回流焊对温度敏感元件造成

2013-09-13 10:25:12

在PCB电子工业焊接工艺中,有越来越多的厂家开始把目光投向选择焊接,选择焊接可以在同一时间内完成所有的焊点,使生产成本降到最低,同时又克服了回流焊对温度敏感元件造成影响的问题,选择焊接还能够与将来

2017-10-31 13:40:44

时,预热所带的热量对焊接质量的影响不是关键因素,PCB材料厚度、器件封装规格及助焊剂类型决定预热温度的设置。在选择性焊接中,对预热有不同的理论解 释:有些工艺工程师认为PCB应在助焊剂喷涂前,进行预热

2018-09-14 11:28:22

呢?正负片工艺之间究竟有什么区别呢?诸位看官听小编慢慢道来。一、正片和负片的区别:正片:沉铜—整板电镀(加厚8到10um)—贴干膜—图镀(在加厚到成品35um)—镀铅锡—蚀刻(镀铅锡的地方是要保留

2017-08-09 18:43:52

PCB,电路板,基板上面如何出现电路呢?这就要蚀刻来实现。所谓蚀刻,先在板子外层需保留的铜箔部分,也就是电路的图形部分,在上面预镀一层铅锡抗蚀层,然后用化学方式将其余的铜箔腐蚀掉。铜有两层,一层

2017-02-21 17:44:26

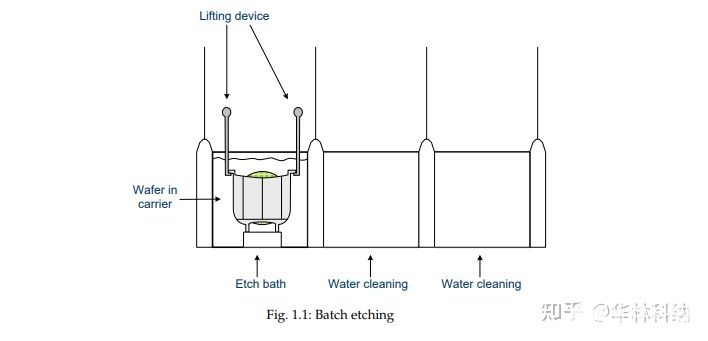

的(即,所有方向的蚀刻速率都相同)或各向异性的(即,不同方向的蚀刻速率不同),尽管在 CMOS 制造中使用的大多数湿蚀刻剂是各向同性的。通常,与干蚀刻工艺相比,湿蚀刻剂往往具有高度选择性。湿蚀刻槽

2021-07-06 09:32:40

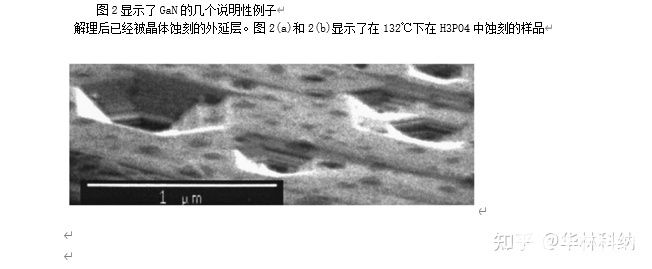

`书籍:《炬丰科技-半导体工艺》文章:GaN 纳米线制造和单光子发射器器件应用的蚀刻工艺编号:JFSJ-21-045作者:炬丰科技网址:http://www.wetsemi.com

2021-07-08 13:11:24

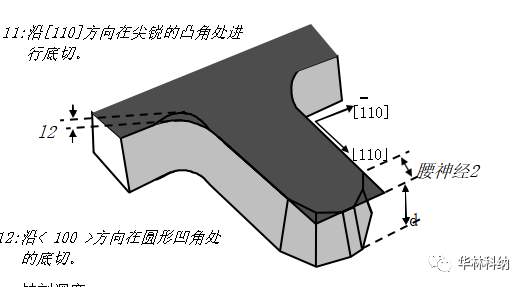

使用 Wulff-Jaccodine方法预测这些结构的凸凹形状。• 使用湿化学蚀刻方法了解和预测 GaN 结构的3D几何形状可以实现将结构(例如纳米线、MEMS)和功能(光电子学)相结合的新应用。如有侵权,请联系作者删除

2021-07-08 13:09:52

、135°C 以上溶于乙二醇的 KOH、180°C 溶于乙二醇的 NaOH。文章全部详情,请加V获取:hlknch / xzl1019^晶体蚀刻工艺中两个蚀刻步骤中的第一个用于确定蚀刻深度,它可以通过几种

2021-07-07 10:24:07

,可用作常用 KKI 蚀刻剂的替代品。通过改变溶液中 HCl 的含量,可以实现对 MESA 形成有用的非选择性蚀刻和 InGaP 对 GaAs 的强选择性蚀刻。这种解决方案的一个重要优点是它不会攻击

2021-07-09 10:23:37

的历史蚀刻工艺进行了两个主要的工艺更改,这使得这项工作成为必要。首先,我们从 Clariant AZ4330 光刻胶切换到 Shipley SPR220-3。我们发现后者的光刻胶具有更好的自旋均匀性

2021-07-06 09:39:22

书籍:《炬丰科技-半导体工艺》文章:微镜角度依赖性与蚀刻剂选择编号:JFKJ-21-047作者:炬丰科技网址:http://www.wetsemi.com/index.html抽象的:在为微光学创建

2021-07-19 11:03:23

:MacEtch 是一种湿法蚀刻工艺,可提供对取向、长度、形态等结构参数的可控性,此外,它是一种制造极高纵横比半导体纳米结构的简单且低成本的方法。 3 该工艺利用了在氧化剂(例如过氧化氢 (H2O2))和酸(例如

2021-07-06 09:33:58

十分精细时将会产生一系列的问题。同时,侧腐蚀会严重影响线条的均匀性。在印制板外层电路的加工工艺中,还有另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺,可以参阅内层制作工艺

2018-04-05 19:27:39

各位大佬:想咨询国内是否有如下这样的工艺:多层PCB/FPC,top层的走线铜,不同的回路,铜厚不一样。我的理解在理论上是可行的,先使用全板铜蚀刻后得到不同的回路,然后对特定的回路进行电镀工艺,增加特定回路的铜厚,各位大佬如果有供应商资源可以和我一起探讨一下,联系方式:***

2022-11-22 14:45:08

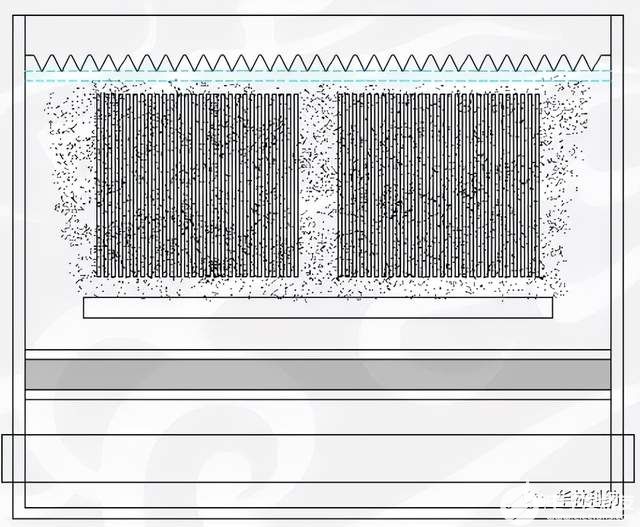

蚀刻 浸入蚀刻是一种半桨技术,它只需一个装满蚀刻洛液的槽,把板子整个浸入到溶液中,如图1所示。板子需要保持浸入直至蚀刻完成,这就需要很长的蚀刻时间,且蚀刻速度非常缓慢。可以通过加热蚀刻溶液的方法

2018-09-11 15:27:47

在印制电路加工中﹐氨性蚀刻是一个较为精细和覆杂的化学反应过程,却又是一项易于进行的工作。只要工艺上达至调通﹐就可以进行连续性的生产, 但关键是开机以后就必需保持连续的工作状态﹐不适宜断断续续地生产

2017-06-23 16:01:38

多层PCB加工过程中必不可少的就是使用到压合机,而压合机压力的均匀性和温度的均匀性对压合的品质影响相当之大,而如何通过试验的方式进行定期的检测其稳定性,从而保证产品的压合品质呢。论坛里有就这个

2018-08-30 10:49:21

多层PCB加工过程中必不可少的就是使用到压合机,而压合机压力的均匀性和温度的均匀性对压合的品质影响相当之大,而如何通过试验的方式进行定期的检测其稳定性,从而保证产品的压合品质呢。论坛里有就这个

2018-11-22 15:41:50

。所有的导电层通过介质利用多层层压工艺粘合在一起。 核材料就是工厂中的双面敷箔板。因为每个核有两个面,全面利用时,PCB的导电层数为偶数。为什么不在一边用敷箔而其余用核结构呢?其主要原因是:PCB

2013-03-13 11:32:34

介质板。所有的导电层通过介质利用多层层压工艺粘合在一起。 核材料就是工厂中的双面敷箔板。因为每个核有两个面,全面利用时,PCB的导电层数为偶数。为什么不在一边用敷箔而其余用核结构呢?其主要

2012-08-09 21:10:38

晶片全面曝光的方法,使单一晶片上可以获得更多的芯片(chip)。如此一来,虽然产率得以提高,但同时也制造一些工艺处理问题。特别在对硅晶片蚀刻深凹槽(deeptrench)工艺方面。 由于采用全面曝光

2018-03-16 11:53:10

的问题,大多数电路板都是使用蚀刻工艺进行生产的,工艺流程中就会出现因为锐角区域较为狭窄而导致有腐蚀性化学物质残留,最后导致Acid Traps现象。那么锐角不可以,直角是否可以呢,这个问题有很多大佬们在各大论坛讨论。个人认为如果没有特殊要求,走线时用钝角既美观有安全,除非部分要求,最好不要使用直角。

2020-07-17 08:30:00

深度解析PCB选择性焊接工艺难点在PCB电子工业焊接工艺中,有越来越多的厂家开始把目光投向选择焊接,选择焊接可以在同一时间内完成所有的焊点,使生产成本降到最低,同时又克服了回流焊对温度敏感元件造成

2013-09-23 14:32:50

湿法蚀刻工艺的原理是使用化学溶液将固体材料转化为液体化合物。选择性非常高,因为所用化学药品可以非常精确地适应各个薄膜。对于大多数解决方案,选择性大于100:1。

2021-01-08 10:12:57

。 在印制板外层电路的加工工艺中,还有另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺,可以参阅内层制作工艺中的蚀刻。 目前,锡或铅锡是最常用的抗蚀层,用在氨性蚀刻剂的蚀刻工艺

2018-09-19 15:39:21

一.概述 目前,印刷电路板(PCB)加工的典型工艺采用"图

2006-04-16 21:23:42 903

903 多层PCB压机温度和压力均匀性测试方法

多层PCB加工过程中必不可少的就是使用到压合机,而压合机压力的均匀性和温度的均匀性

2009-11-19 08:44:06 997

997 超细线蚀刻工艺技术介绍

目前,集成度呈越来越高的趋势,许多公司纷纷开始SOC技术,但SOC并不能解决所有系统集成的问题,因

2010-03-30 16:43:08 1181

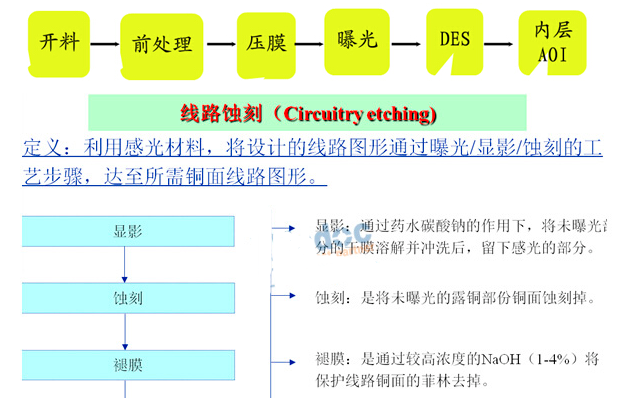

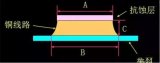

1181 印刷线路板从光板到显出线路图形的过程是一个比较复杂的物理和化学反应的过程,本文就对其最后的一步--蚀刻进行解析。目前,印刷电路板(PCB)加工的典型工艺采用"图形电镀法"。即先在板子外层需保留的铜箔部分上,也就是电路的图形部分上预镀一层铅锡抗蚀层,然后用化学方式将其余的铜箔腐蚀掉,称为蚀刻。

2017-12-26 08:57:16 28232

28232 本文首先介绍了PCB蚀刻工艺原理和蚀刻工艺品质要求及控制要点,其次介绍了PCB蚀刻工艺制程管控参数及蚀刻工艺品质确认,最后阐述了PCB蚀刻工艺流程详解,具体的跟随小编一起来了解一下吧。

2018-05-07 09:09:09 40469

40469 印刷线路板从光板到显出线路图形的过程是一个比较复杂的物理和化学反应的过程,本文就对其最后的一步--蚀刻进行解析。目前,印刷电路板(PCB)加工的典型工艺采用“图形电镀法”。即先在板子外层需保留的铜箔部分上,也就是电路的图形部分上预镀一层铅锡抗蚀层,然后用化学方式将其余的铜箔腐蚀掉,称为蚀刻。

2019-08-16 11:31:00 4646

4646 蚀刻过程是PCB生产过程中基本步骤之一,简单的讲就是基底铜被抗蚀层覆盖,没有被抗蚀层保护的铜与蚀刻剂发生反应,从而被咬蚀掉,最终形成设计线路图形和焊盘的过程。当然,蚀刻原理用几句话就可以轻而易举

2019-07-23 14:30:31 3894

3894

在印制板外层电路的加工工艺中,还有另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺,可以参阅内层制作工艺中的蚀刻。目前,锡或铅锡是最常用的抗蚀层,用在氨性蚀刻剂的蚀刻工艺

2019-07-10 15:11:35 2708

2708

要注意的是,这时的板子上面有两层铜。在外层蚀刻工艺中仅仅有一层铜是必须被全部蚀刻掉的,其余的将形成最终所需要的电路。这种类型的图形电镀,其特点是镀铜层仅存在于铅锡抗蚀层的下面。另外一种工艺方法是整个

2019-07-08 14:51:34 2430

2430

目前,印刷电路板(PCB)加工的典型工艺采用"图形电镀法"。即先在板子外层需保留的铜箔部分上,也就是电路的图形部分上预镀一层铅锡抗蚀层,然后用化学方式将其余的铜箔腐蚀掉,称为蚀刻。

2019-07-01 16:33:53 2423

2423

印刷线路板从光板到显出线路图形的过程是一个比较复杂的物理和化学反应的过程,本文就对其最后的一步——蚀刻进行解析。

2019-05-31 16:14:09 3307

3307 目前,印刷电路板(PCB)加工的典型工艺采用"图形电镀法"。即先在板子外层需保留的铜箔部分上,也就是电路的图形部分上预镀一层铅锡抗蚀层,然后用化学方式将其余的铜箔腐蚀掉,称为蚀刻。

2019-07-06 10:13:21 8077

8077 目前,印刷电路板(PCB)加工的典型工艺采用”图形电镀法”。即先在板子外层需保留的铜箔部分上,也就是电路的图形部分上预镀一层铅锡抗蚀层,然后用化 学方式将其余的铜箔腐蚀掉,称为蚀刻。

2019-07-09 10:09:34 3924

3924 PCB板蚀刻工艺用传统的化学蚀刻过程腐蚀未被保护的区域。有点像是挖沟,是一种可行但低效的方法。在蚀刻过程中也分正片工艺和负片工艺之分,正片工艺使用固定的锡保护线路,负片工艺则是使用干膜或者湿膜来保护线路。用传统的蚀刻方法到线或焊盘的边缘是畸形的。

2020-07-12 10:26:56 3060

3060 大型PCB制造商使用电镀和蚀刻工艺在板上生产走线。对于电镀,生产过程始于覆盖外层板基板的电镀铜。 光刻胶蚀刻也用作生产印刷电路板的另一个关键步骤。在蚀刻过程中保护所需的铜需要在去除不希望有的铜和在

2020-12-31 11:38:58 3561

3561 1、 PCB蚀刻介绍 蚀刻是使用化学反应而移除多余材料的技术。PCB线路板生产加工对蚀刻质量的基本要求就是能够将除抗蚀层下面以外的所有铜层完全去除干净,仅此而已。在PCB制造过程中,如果要精确地

2021-04-12 13:48:00 31008

31008

多层PCB内层的光刻工艺包括几个阶段,接下来详细为大家介绍多层PCB内层的光刻工艺每个阶段都需要做什么。 PART.1 在第一阶段,内层穿过化学制剂生产线。铜表面会出现粗糙度,这对于光致抗蚀剂的最佳

2021-09-05 10:00:16 2160

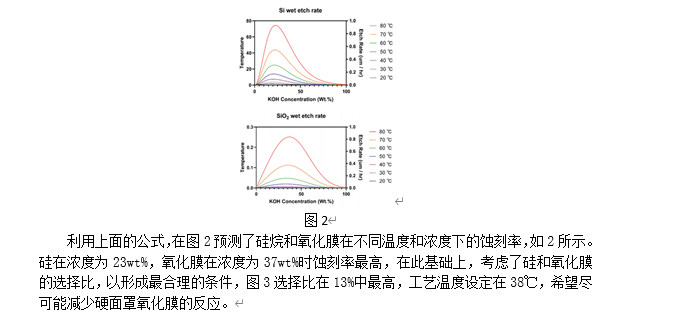

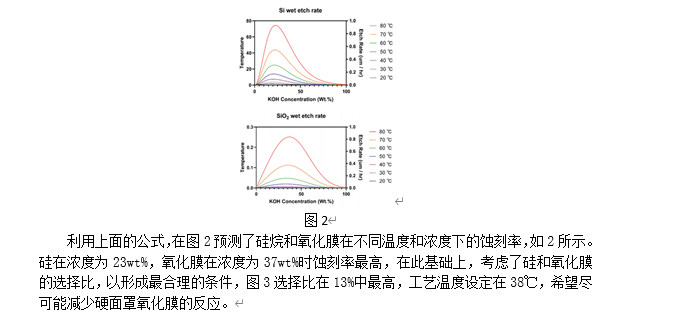

2160 引言 了解形成MEMS制造所需的三维结构,需要SILICON的各向异性蚀刻,此时使用的湿式蚀刻工艺考虑的事项包括蚀刻率、长宽比、成本、环境污染等[1]。用于硅各向异性湿式蚀刻 溶液有KOH

2021-12-23 09:55:35 484

484

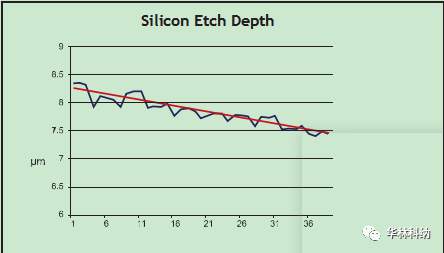

本研究透过数值解析,将实验上寻找硅晶片最佳流动的方法,了解目前蚀刻阶段流动的形式,并寻求最佳晶片蚀刻条件,蚀刻工艺效率低利用气泡提高湿法蚀刻工艺效果,用实验的方法寻找最佳流动,通过数值分析模拟了利用

2022-01-19 17:11:32 340

340

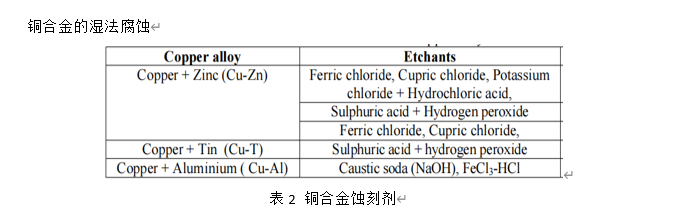

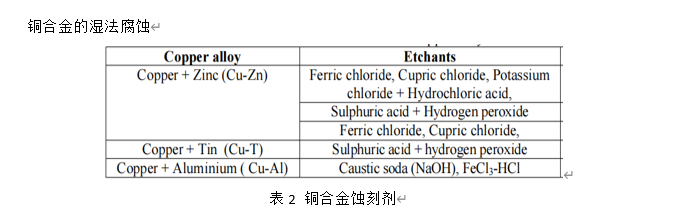

湿法蚀刻工艺已经广泛用于生产各种应用的微元件。这些过程简单易操作。选择合适的化学溶液(即蚀刻剂)是湿法蚀刻工艺中最重要的因素。它影响蚀刻速率和表面光洁度。铜及其合金是各种工业,特别是电子工业的重要

2022-01-20 16:02:24 1860

1860

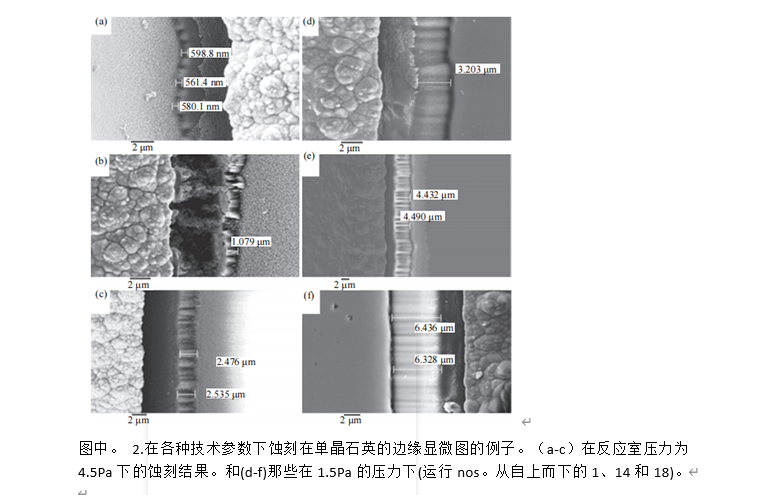

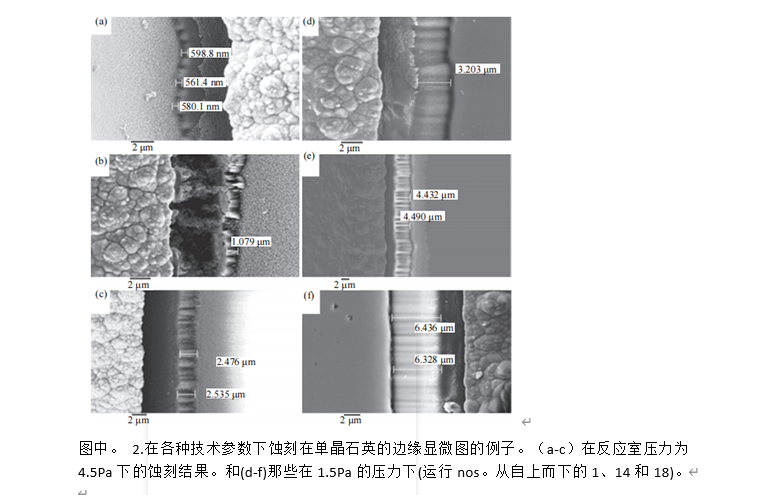

本文对单晶石英局部等离子体化学刻蚀工艺的主要工艺参数进行了优化。在射频(射频,13.56兆赫)放电激励下,在CF4和H2的气体混合物中进行蚀刻。采用田口矩阵法的科学实验设计来检验腔室压力、射频发生器

2022-02-17 15:25:42 1804

1804

的氧化镍未完全去除造成的。这项研究对这些多余金属缺陷的成分进行了分类和确定,评估了推荐的去除氧化镍的湿蚀刻方法,最后提出了一种湿蚀刻工艺,该工艺将快速去除缺陷,同时继续保持所需的半各向异性蚀刻轮廓,这是大多数金属

2022-02-28 14:59:35 1780

1780

了解形成MEMS制造所需的三维结构,需要SILICON的各向异性蚀刻,此时使用的湿式蚀刻工艺考虑的事项包括蚀刻率、长宽比、成本、环境污染等[1]。用于硅各向异性湿式蚀刻。

2022-03-11 13:57:43 336

336

半导体生产过程中,蚀刻工艺是非常重要的工艺。蚀刻工艺中使用的方法通常有batch式和枯叶式两种。Batch式是用传统的方法,在药液bath中一次性加入数十张晶片进行处理的方法。但是随着半导体技术

2022-03-14 10:50:47 475

475

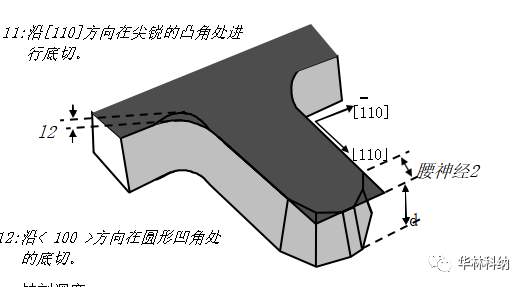

我们开发了一种改进的各向异性湿法蚀刻工艺,通过在晶片上使用单个蚀刻掩模来制造各种硅微结构,这些微结构具有圆形凹角和尖锐凸角、用于芯片隔离的凹槽、蜿蜒的微流体通道、具有弯曲V形凹槽的台面结构以及具有

2022-03-14 10:51:42 581

581

硅是微电子学和微细力学中最常用的衬底材料。它不仅可用作无源衬底,也可用作电子或机械元件的有源材料。如本章所述,所需的图案也可以通过湿化学蚀刻方法来实现。

2022-03-23 14:17:16 1811

1811

的各向同性湿法蚀刻条件相比,由于非常高的各向异性,反应离子蚀刻工艺能够实现更好的蚀刻尺寸控制。尽管如此,当使用敏感材料(即栅极氧化物[1])或当尺寸放宽时,使用光敏抗蚀剂的湿法图案化仍然是参考工艺。本文研究了整个湿法腐蚀过程中抗蚀剂保护的完整性。给出了确保这种保护的一些提示,以及评估这种保护的相关新方法。

2022-04-06 13:29:19 666

666

薄晶片已成为各种新型微电子产品的基本需求。 需要更薄的模具来适应更薄的包装。 使用最后的湿蚀刻工艺在背面变薄的晶圆与标准的机械背面磨削相比,应力更小。 硅的各向同性湿蚀刻通常是用硝酸和氢氟酸的混合物

2022-04-07 14:46:33 751

751

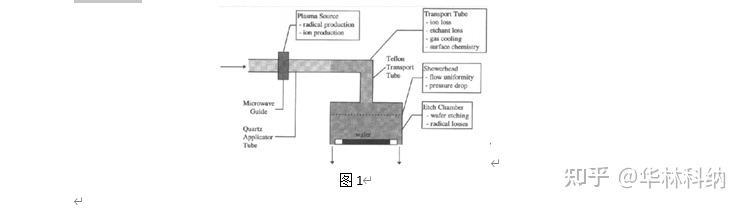

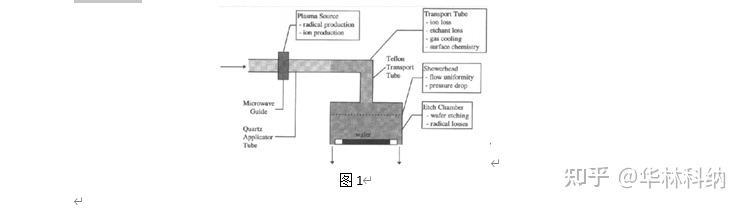

本研究的目的是开发和应用一个数值模型来帮助设计和操作CDE工具,为此,我们编制了第一个已知的NF3/02气体的等离子体动力学模型,通过与实验蚀刻速率数据的比较,实现了模型验证。此外,该模型通过改变

2022-04-08 16:44:54 893

893

抛光的硅片是通过各种机械和化学工艺制备的。首先,通过切片将单晶硅锭切成圆盘(晶片),然后进行称为研磨的平整过程,该过程包括使用研磨浆擦洗晶片。 在先前的成形过程中引起的机械损伤通过蚀刻是本文的重点。在准备用于器件制造之前,蚀刻之后是各种单元操作,例如抛光和清洁。

2022-04-28 16:32:37 668

668

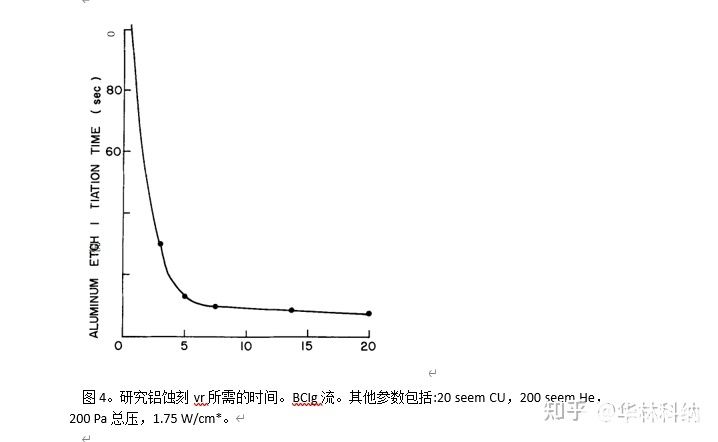

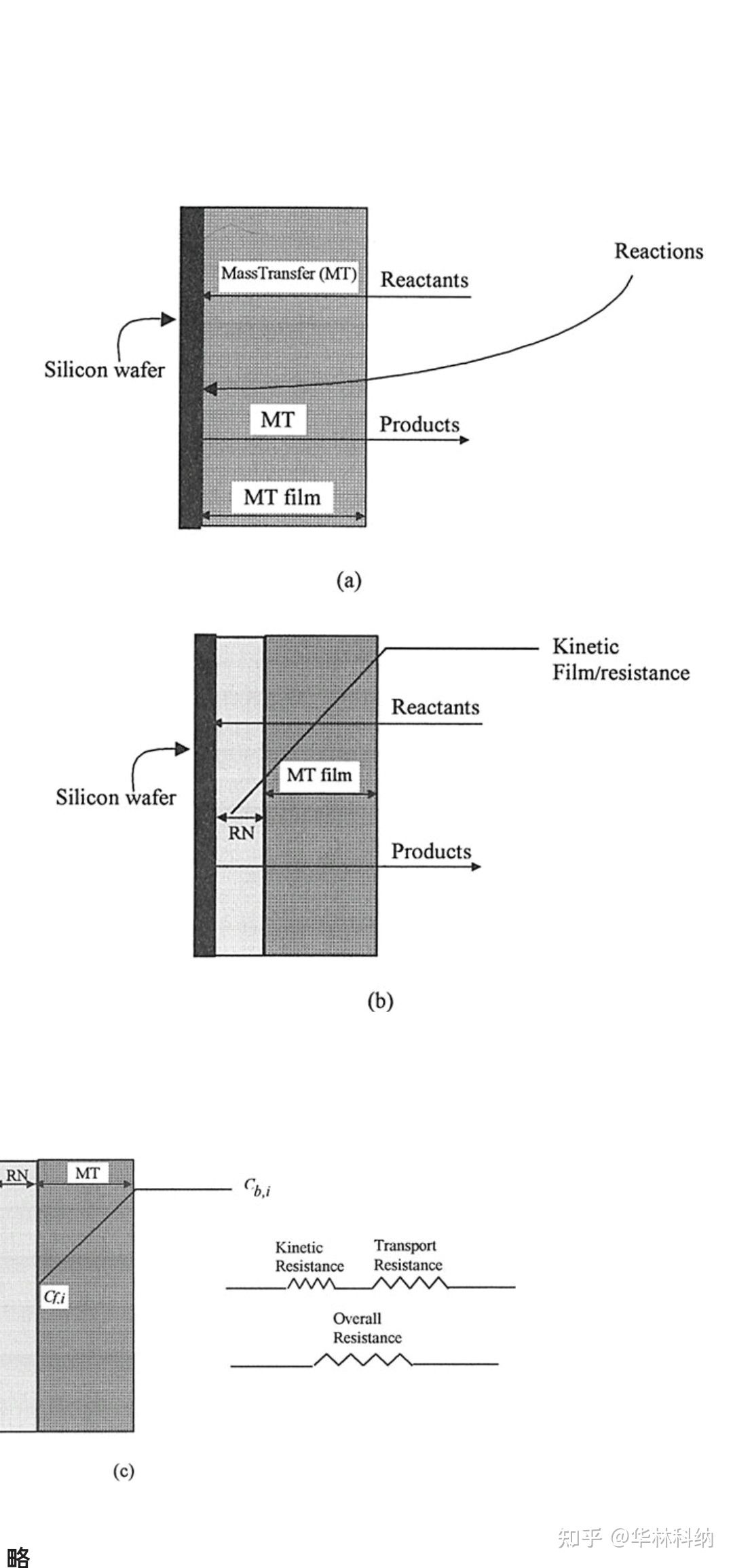

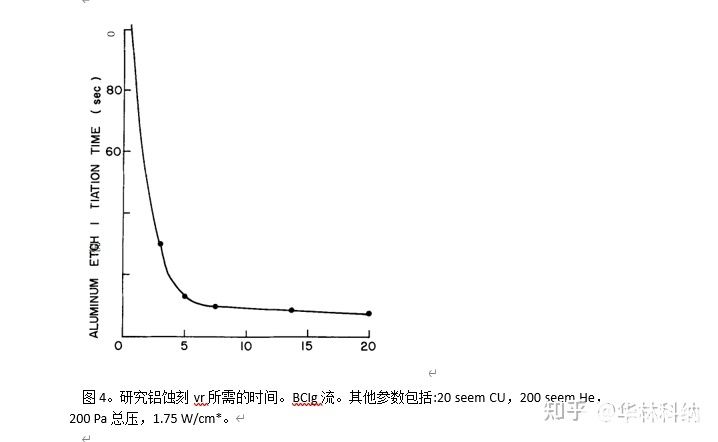

引言 我们华林科纳讨论了一种高速率各向异性蚀刻工艺,适用于等离子体一次蚀刻一个晶片。结果表明,蚀刻速率主要取决于Cl浓度,而与用于驱动放电的rf功率无关。几种添加剂用于控制蚀刻过程。加入BCl以开始

2022-06-13 14:33:14 904

904

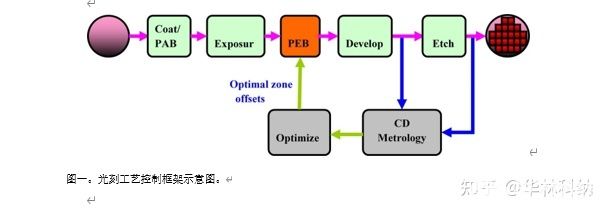

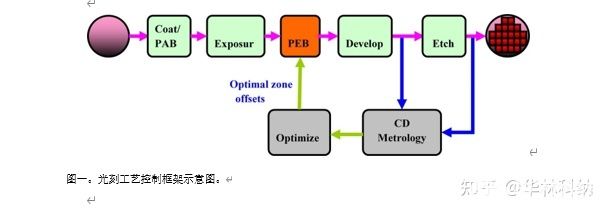

新的方法,通过光刻和刻蚀工艺顺序来提高跨晶片栅极CD的均匀性。我们华林科纳所提出的方法是通过优化整个晶片曝光后烘烤(PEB)温度曲线来补偿光刻工艺顺序中的上游和下游系统CD变化成分。更准确地说,我们首先构建了一个温度-偏移模型,该模型将

2022-06-22 14:58:34 1301

1301

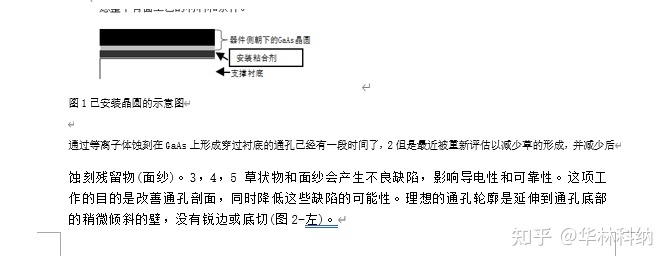

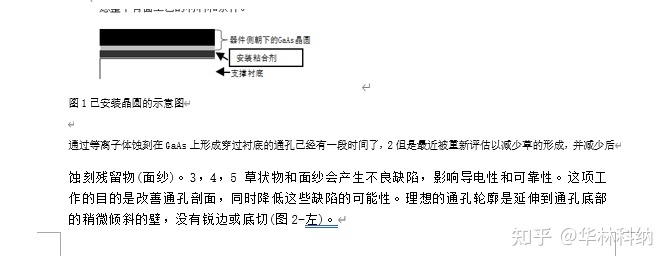

通过使用多级等离子体蚀刻实验设计、用于蚀刻后光致抗蚀剂去除的替代方法,以及开发自动蚀刻后遮盖物去除顺序;一种可再现的基板通孔处理方法被集成到大批量GaAs制造中。对于等离子体蚀刻部分,使用光学显微镜

2022-06-23 14:26:57 516

516

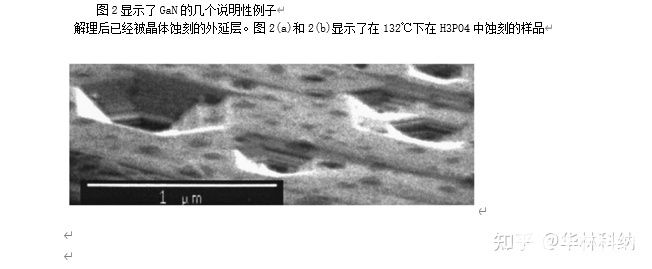

目前,大多数III族氮化物的加工都是通过干法等离子体蚀刻完成的。1,2干法蚀刻有几个缺点,包括产生离子诱导损伤3和难以获得激光器所需的光滑蚀刻侧壁。干法蚀刻产生的侧壁的典型均方根(rms)粗糙度约为

2022-07-12 17:19:24 3454

3454

蚀刻工艺 蚀刻过程分类

2022-08-08 16:35:34 736

736

薄晶片已成为各种新型微电子产品的基本需求。更薄的模具需要装进更薄的包装中。与标准的机械背磨相比,在背面使用最终的湿法蚀刻工艺而变薄的晶片的应力更小。

2022-08-26 09:21:36 2363

2363

金属蚀刻是一种通过化学反应或物理冲击去除金属材料的技术。金属蚀刻技术可分为湿蚀刻和干蚀刻。金属蚀刻由一系列化学过程组成。不同的蚀刻剂对不同的金属材料具有不同的腐蚀特性和强度。

2023-03-20 12:23:43 3172

3172 印刷线路板从光板到显出线路图形的过程是一个比较复杂的物理和化学反应的过程,本文就对其最后的一步--蚀刻进行解析。目前,印刷电路板(PCB)加工的典型工艺采用"图形电镀法"。即先在

2023-03-29 10:04:07 886

886 其实不同颜色的PCB,它们的制造的材料、制造工序都是一样的,包括敷铜层的位置也是一样的,经过蚀刻工艺后就在PCB上留下了最终的布线,例如下图这块刚经过蚀刻工艺的PCB,敷铜走线就是原本的铜色,而PCB基板略显微黄色。

2023-05-09 10:02:43 1699

1699

蚀刻可能是湿制程阶段最复杂的工艺,因为有很多因素会影响蚀刻速率。如果不保持这些因素的稳定,蚀刻率就会变化,因而影响产品质量。如果希望利用一种自动化方法来维护蚀刻化学,以下是你需要理解的基本概念。

2023-05-19 10:27:31 575

575

纳米片工艺流程中最关键的蚀刻步骤包括虚拟栅极蚀刻、各向异性柱蚀刻、各向同性间隔蚀刻和通道释放步骤。通过硅和 SiGe 交替层的剖面蚀刻是各向异性的,并使用氟化化学。优化内部间隔蚀刻(压痕)和通道释放步骤,以极低的硅损失去除 SiGe。

2023-05-30 15:14:11 1071

1071

关键词:氢能源技术材料,耐高温耐酸碱耐湿胶带,高分子材料,高端胶粘剂引言:蚀刻(etching)是将材料使用化学反应或物理撞击作用而移除的技术。蚀刻技术可以分为湿蚀刻(wetetching)和干蚀刻

2023-03-16 10:30:16 3504

3504

半导体制造工艺之光刻工艺详解

2023-08-24 10:38:54 1221

1221

在印制板外层电路的加工工艺中,还有另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺,可以参阅内层制作工艺中的蚀刻。

2023-09-06 09:36:57 811

811

要注意的是,蚀刻时的板子上面有两层铜。在外层蚀刻工艺中仅仅有一层铜是必须被全部蚀刻掉的,其余的将形成最终所需要的电路。这种类型的图形电镀,其特点是镀铜层仅存在于铅锡抗蚀层的下面。

2023-09-07 14:41:12 474

474

一站式PCBA智造厂家今天为大家讲讲pcb打样蚀刻工艺注意事项有哪些?PCB打样蚀刻工艺注意事项。PCB打样中,在铜箔部分预镀一层铅锡防腐层,保留在板外层,即电路的图形部分,然后是其余的铜箔被化学方法腐蚀,称为蚀刻。

2023-09-18 11:06:30 670

670 另外一种工艺方法是整个板子上都镀铜,感光膜以外的部分仅仅是锡或铅锡抗蚀层。这种工艺称为“全板镀铜工艺“。与图形电镀相比,全板镀铜的缺点是板面各处都要镀两次铜而且蚀刻时还必须都把它们腐蚀掉。

2023-12-06 15:03:45 263

263

电子发烧友App

电子发烧友App

评论