天线最终的目的是要将射频信号辐射到自由空间,这时天线的设计就显得非常重要,但是天线设计很大程度上依赖于所安装平台的特性,另外天线对周围环境很敏感,这些原因导致很多情况下,天线对每个平台都是独一无二的设计。

2016-10-24 11:33:12 81945

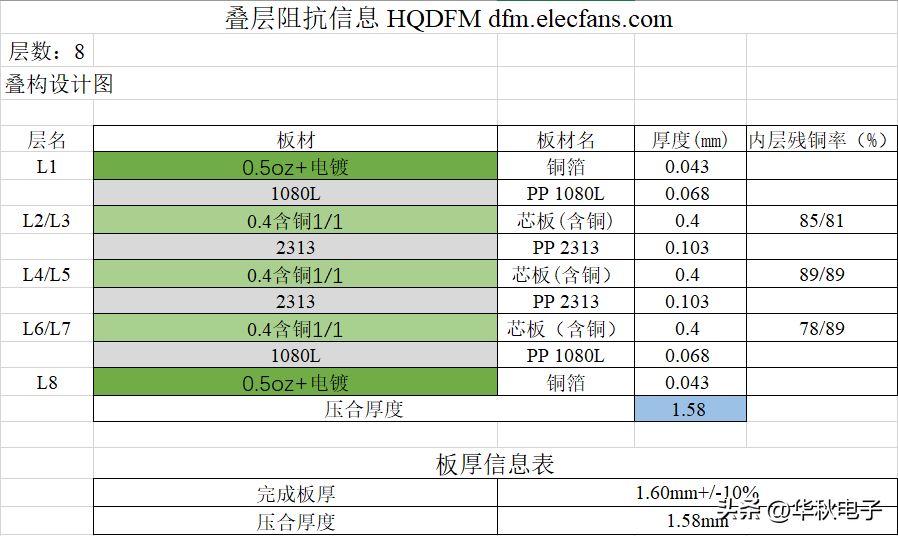

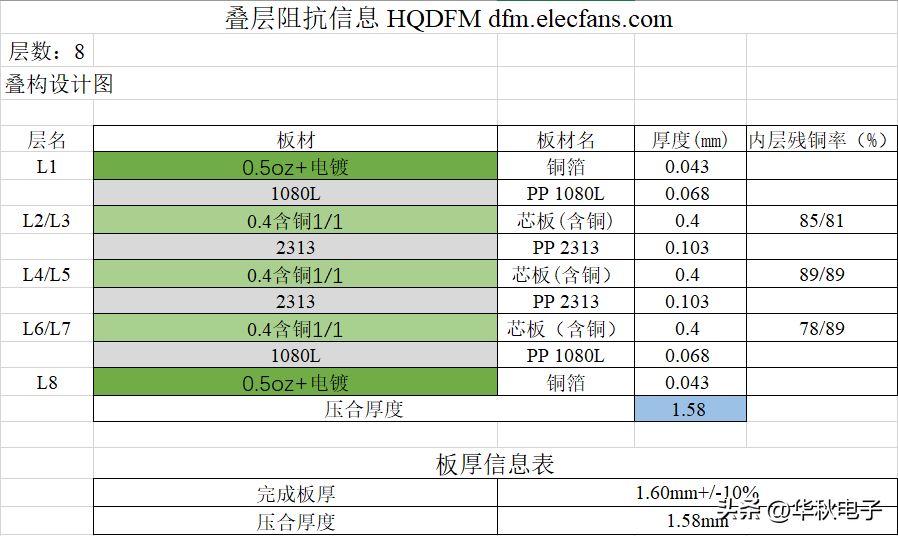

81945 由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。

2023-07-18 09:22:31 875

875

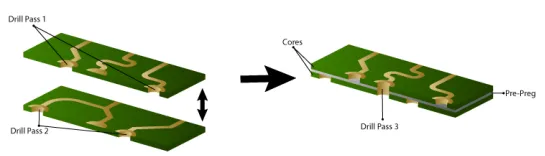

作者:蒋修国 过孔的应用场景非常多,过孔的结构也是相当复杂,在写《ADS信号完整性仿真与实战》一书时,用了一整章介绍了过孔。如下是过孔的一张简化结构图: 其中就包括了过孔的残桩Stub。 通常

2021-03-12 11:17:20 2715

2715 决于选择的PCB叠层结构。由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分

2023-07-31 10:18:02 684

684

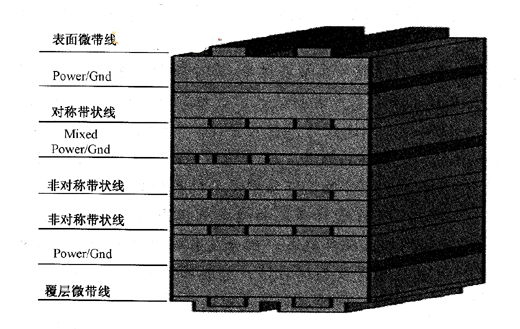

层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本文介绍多层PCB板层叠结构的相关内容。对于电源、地的层数以及信号层数确定后,它们之间的相对排布位置是每一个PCB工程师都不能回避的话题;

2016-08-04 11:27:07 6502

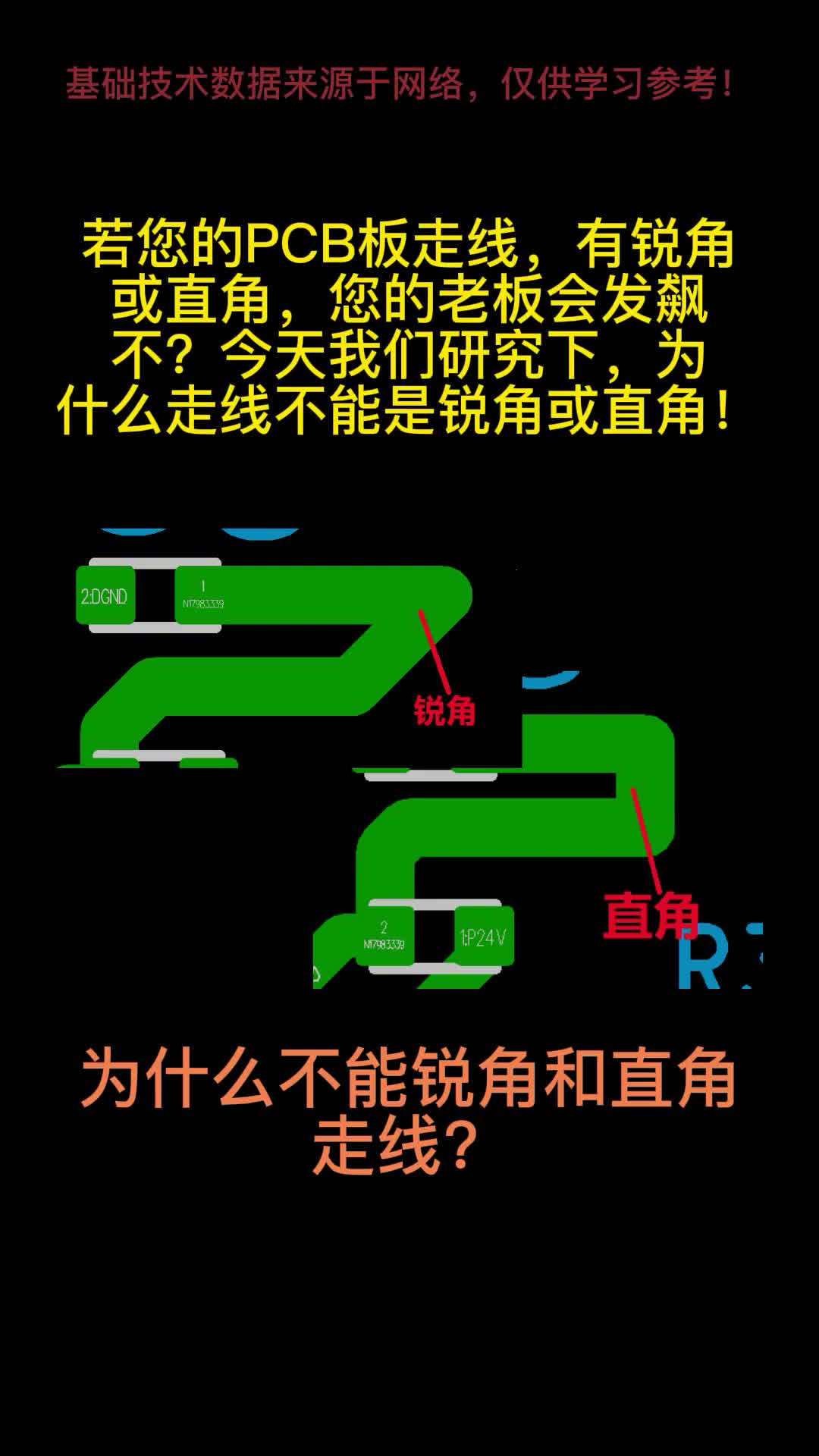

6502 下面从直角走线、差分走线、蛇形线三个方面来阐述PCB LAYOUT的走线。

2021-03-17 07:25:46

本帖最后由 maskmyself 于 2017-7-10 10:08 编辑

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速

2017-07-07 11:45:56

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2014-08-13 15:44:05

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-08-05 06:40:24

新人,求PCB布局走线资料,谢谢!

2014-08-02 19:19:40

PCB中走线有几种这几种分别有什么作用?哪种对信号的影响最好?

2012-11-13 15:49:21

pcb走线时,会影响到已经布完的线。之前正在布的线不会对已经布完的线产生影响,现在不知道怎么恢复。

2019-09-25 03:58:46

好的图像质量的保证。 PCB走线如果可能的话,信号走线使用6mil, 走线间距使用6mil. 放置0.1uF的退耦电容在对应的DSP电源脚上,并尽可能的靠近。它的走线尽可能的粗。电源正极的走线最少要

2023-04-13 16:09:54

求高手贡献PCB设计走线经验!及相关技术

2013-01-11 20:02:07

1.PCB走线线宽的重要性 PCB载流能力的计算一直缺乏权威的技术方法、公式,经验丰富CAD工程师依靠个人经验能作出较准确的判断。但是对于CAD新手,不可谓遇上一道难题。 对于大电流电源走线

2023-04-12 16:02:23

`为什么下图中PCB走线正反面不同。孔与孔之间为直接通路。为什么背面的走线环绕迂回。小白菜提问,求高手详解。谢谢`

2018-10-29 08:46:46

`用altium 画PCB 对称电路时走线没有走对称,看起来有点别扭。像这种对称电路走线一般要怎么处理比较好呢?像我这样画对电器想能有没有什么影响?要怎么画才比较合理?希望大家指点指点`

2017-01-07 11:20:13

经常听说“PCB走线间距大于等于3倍线宽时可以抑制70%的信号间干扰”,这就是3W原则,信号线之间的干扰被称为串扰。那么,你知道串扰是怎么形成的吗?当两条走线很近时,一条信号线上的信号可能会在另一

2022-12-27 20:33:40

在pcb的设计过程中,元器件的布局和走线的调整是非常重要的一个步骤。恰当的布局可以简化布线的难度,更重要的是可以提高PCB的电气性能,减少EMC,EMI。 下面是同一个原理图对应的两种不同的布局和走

2019-10-17 04:37:54

PCB板蛇形走线有什么作用PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,麦|斯|艾|姆|P|CB样板贴片,麦1斯1艾1姆1科1技全国1首家P|CB样板打板蛇形走线的主要作用

2013-08-29 15:43:30

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是时钟

2017-11-22 20:04:14

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2018-08-30 10:14:44

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2020-07-14 18:02:17

PCB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关"信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处?;最典型的就是

2018-09-20 11:05:23

PCB电容引脚之间可以走线吗?

2023-04-13 16:25:48

1.1 PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。1.3 高速数字信号走线尽量短。1.4 敏感模拟信号走线尽量短。1.5

2019-05-30 06:58:19

PCB设计走线的宽度与最大允许电流有何关系?PCB设计走线的宽度与铜厚有何关系?

2021-10-11 09:49:14

PCB设计走线的规则是什么

2021-03-17 06:36:28

PCB能不能以锐角走线pcb layout能不能以90°走线

2021-02-26 08:14:21

1. 一般规则1.1 PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。1.3 高速数字信号走线尽量短。1.4 敏感模拟信号走线尽量

2014-03-14 17:44:44

pcb布局,走线方面,有什么建议吗,该怎么怎么走,怎么提高效率

2016-10-15 14:51:34

;=2倍的线宽。PCI板上的蛇行线就是为了适应PCI 33MHzClock的线长要求。若在一般普通PCB板中,是一个分布参数的 LC滤波器,还可作为收音机天线的电感线圈,短而窄的蛇形走线可做保险丝等等

2019-05-22 02:48:05

PCB Layout中的走线策略布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见

2009-08-20 20:58:49

,尽量不要走蛇形线,尤其不能在小范围内蜿蜒走线。5. 可以经常采用任意角度的蛇形走线,如图1-8-20中的C结构,能有效的减少相互间的耦合。6. 高速PCB 设计中,蛇形线没有所谓滤波或抗干扰的能力,只

2018-07-08 13:28:36

cadence PCB 怎么取消走线?***用过,取消很容易,cadence没发现这个功能!

2016-01-25 22:57:46

的平面是导体,这就够了。信号路径是表层走线,所以下面的平面就是参考路径。对于PCB上这一特殊结构,参考路径是以平面的形式出现的,所以也叫参考平面。从电流回路的角度来说,参考平面承载着信号的返回

2014-11-17 10:07:29

作用,这种结构在高频的(10G以上)IC封装PCB设计中经常会用采用,被称为CPW结构,可以保证严格的差分阻抗控制(2Z0),如图1-8-19。差分走线也可以走在不同的信号层中,但一般不建议这种走法

2019-03-18 21:38:12

为什么PCB走线中不能出现锐角和直角?而且走线也不能和IC的PIN脚垂直?会影响到什么?

2023-04-11 16:31:28

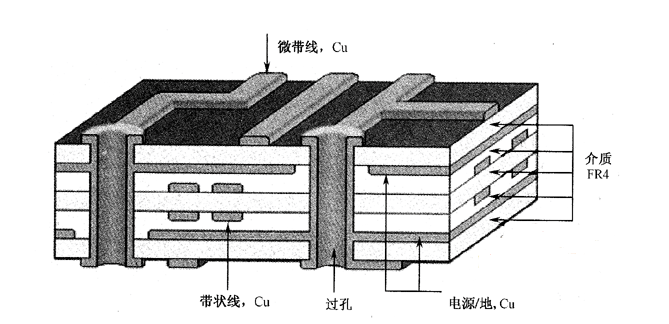

介电常数受横截面的几何结构影响比较大;而串扰,其有效介电常数受奇偶模式的影响较大;不同绕线方式有效介电常数受其绕线方式的影响。3.仿真分析过程 3.1 微带线和带状线传输时延PCB中微带线是指走线只有一

2014-10-21 09:54:56

AD里PCB多根走线时怎么改变线宽

2019-09-12 04:20:46

怎样计算PCB布线中走线允许的最大长度?走线太长了都有哪些影响呢?

2023-04-10 17:10:25

宽,距电源/地越近,或隔离层的介电常数越高,特征阻抗就越小。 11、PCB板上的走线可等效为串联和并联的电容、电阻和电感结构。串联电阻的典型值0.25-0.55 ohms/英尺。并联电阻阻值通常很高

2014-12-16 09:47:09

做一网络通信,发现网口直线有点问题,直接从网络变压器的输出端子接信号(我还用的排线)传输速度能达几MB/S,但是如果通过PCB直线,发现传输速度只有几KB/S,差别太大了,有什么挽救办法没有?由于结构原因,接口离网络变压器有7~8CM的距离走线,还经过了两个连接器!

2012-10-17 21:01:53

PCB走线线间距能不能走5mil?

2019-09-26 05:35:53

PCB长距离走线和短距离加个过孔走线哪种走线更合理?

2019-09-25 22:11:32

AD18 ,PCB,走线,任意走线,在哪里设置?

2019-03-07 01:36:59

全球领先的全套互连产品供应商Molex公司推出2.4mm精密压接安装测试连接器产品,这是业界唯一的工作于50 GHz的高速垂直PCB装接结构。与传统的末端装接连接器(end-launch connector)相比,

2012-07-10 09:30:49 971

971

2012-10-12 12:55:09 0

0 2013-12-16 14:10:04 0

0 电源平面和地平面要满足20H规则;当电源层、底层数及信号的走线层数确定后,为使PCB具有良好的EMC性能它们之间的相对排布位置基本要求...

2018-03-30 16:05:45 17029

17029

在设计多层 PCB 电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用 4 层,6 层,还是更多层数的电路板。 确定层数之后, 再确定内电层的放置位置以及如何在这些层上分布不同的信号。

2018-08-01 08:00:00 0

0 寻找PCB行业结构性成长机会。在2000年以前,全球PCB产值70%分布在欧洲、美洲、日本等三个地区。

2018-08-03 16:34:06 5018

5018 PCB产品结构复杂,产品种类根据终端需求不断演进:终端电子产品向轻薄、短小、多功能的需求变化,促使电子元器件的产品性能和集成度迅速提升。

2018-09-07 17:07:26 13570

13570 我国PCB产业结构仍有改善空间,IC载板占比低于国际水平。从PCB产业结构来看, Prismark数据显示,全球PCB市场中,IC载板占比始终高于10%,而我国PCB产业IC载板占比始终保持在较低

2019-01-18 16:51:07 7036

7036

这种精度对低频电路没有一点问题,但RF电路一般需要50Ω的走线才能正常运行。部件体积越来越小,但物理定律不会改变。因此, 今天0.062英寸厚原型板上的一根微带走线尺寸为0.11英寸宽,而30年前也是0.11英寸。但很多SMT(表面组装技术)元件都要比其前代元件小得多,因此,用于RF原型的低成本双面板似乎不适合于今天的小型SMT元件。

2019-02-26 14:36:05 3118

3118 机械层是定义整个PCB板的外观的,其实我们在说机械层的时候就是指整个PCB板的外形结构。

2020-01-16 12:11:00 3613

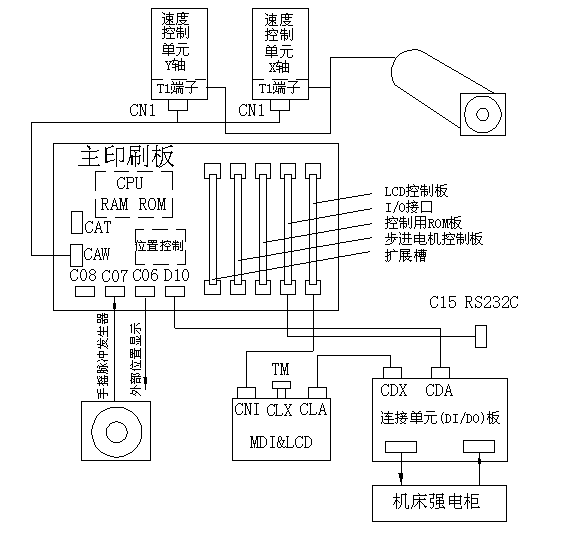

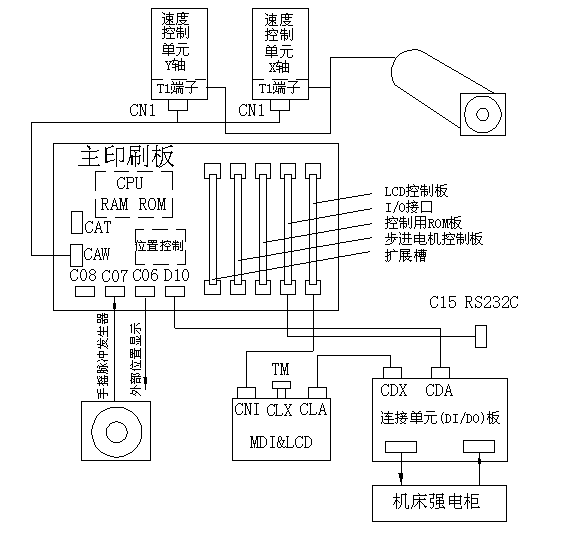

3613 数控装置是整个数控系统的核心,其硬件结构按CNC装置中各PCB电路板的插接方式可以分为大板式结构和功能模块式结构。

2019-11-12 17:36:30 1596

1596

近年我国的印制电路行业走过了艰辛的历程,外资大量涌入,内资体制调整,价格竞争激烈,成本不断上涨,兼并重组使中国的PCB产业结构发生了巨大变化。

2019-11-09 11:21:29 805

805 机械层是定义整个PCB板的外观的,其实我们在说机械层的时候就是指整个PCB板的外形结构。

2019-09-05 16:07:25 3045

3045 随着市场竞争的加剧,硬件设备正以集成化的方向发展。天线也由外置进化内置再进化到嵌入式,我们先来介绍这类应用的天线种类:

2019-09-09 10:49:00 0

0 确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于生产厂家来说,层叠结构对称与否是PCB板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到最佳的平衡。

2019-10-04 17:10:00 8395

8395

确定多层 PCB 板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于生产厂家来说,层叠结构对称与否是 PCB 板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到最佳的平衡。

2019-10-15 14:31:36 4960

4960

在PCBA业务领域,随着南通数通二期的投产,无锡深南PCB产品结构得到进一步优化,从而使无锡深南 PCB 业务的生产效率及产出得到提升,盈利能力增强;无锡深南的PCBA业务在上半年也有一定的增长。

2020-09-25 10:59:16 2338

2338 晶体尽量靠近主控放置,晶体的负载电容靠近管脚放置;晶体走线尽量短且走在表层,避免打孔换层。

2021-02-19 15:47:27 4242

4242

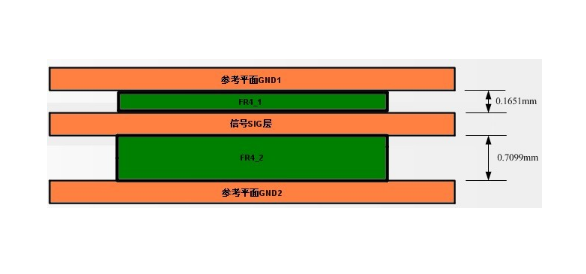

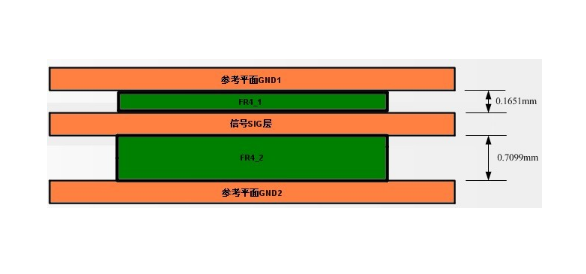

选择板层、板厚、内层铜厚、阻抗层、参考层并输入阻抗值、线距(差分阻抗)、线到铜的距离(共面阻抗),点计算,可自动计算出线宽及叠构方案。

2022-09-16 09:23:08 2206

2206 关键信号优先选TOP层,因为在TOP层下面是GND层。射频和高速信号,走线需要为50ohm,所以叠层厚度需要考虑阻抗控制。

2022-10-09 16:15:39 1849

1849 虽然PCB技术有了进步,但PCB的基本结构没有改变,例如材料特性、使用的层叠层数、几何结构和钻孔技术(允许孔只穿透堆叠的一部分)。通过PCB技术形成的结构被抽象为一组物理/电气结构:走线、平面(或电源层)、通孔和焊盘。

2022-10-20 11:15:03 540

540 在PCB设计时我们在处理DDR部分的时候都会进行一个拓扑的选择,一般DDR有T点和Fly-by两种拓扑结构,那么这两种拓扑结构的应用场景和区别有哪些呢? T点拓扑结构: CPU出来的信号线经过

2022-11-27 07:40:01 999

999 PCB板层层叠结构介绍

2023-02-18 17:47:09 2582

2582

该基站的双工器似乎是虹膜耦合腔滤波器,与一些腔间耦合。输入和输出的耦合是T,是谐振器上的一个连接部分,而不是耦合回路。频率由电容帽调节。滤波器是宽信号的带通。

2023-03-04 16:03:51 353

353 和正片设计相反,负片设计默认是有铜的,走线和铺铜的地方意味着这里的铜被清除,没有走线和铺铜的地方铜被保留。见下图。其成本相对正片来说极低,且流程短,但存在极大的“坏孔”隐患。

2023-03-19 11:36:43 948

948 精进成为一个很厉害的工程师。 同样是硬件工程师,有的三四年年收入增长了三倍,有的只涨了3000,甚至于还有降薪了,这些都是身边朋友同事的真实案例。当然不排除运气的因素,但是持续的充电学习,迅速提高自己的设计能力和专业素养,是你获得专业技能提升与涨薪的不二法门。 硬件工程师是需要“广”而“博”的设计知识的。 如果你想在此行业有更好的发展,不仅仅要懂得基本数字硬件设计知识,还需要 模拟电路的设计知识

2023-07-04 12:15:04 269

269

决于选择的PCB叠层结构。 由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。 PCB叠层设计 “ 层的定义设计原则 1、主芯片相临层

2023-07-19 07:45:02 543

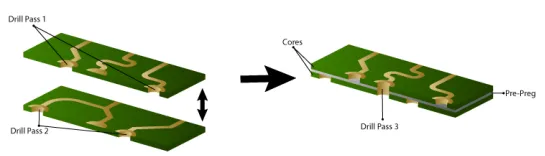

543 在设计2层PCB时,实际上不需要考虑PCB在工厂的结构问题。但是,当电路板上的层数为四层或更多时,PCB的堆叠是一个重要因素。

2023-07-19 16:19:13 2030

2030

由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。

2023-07-20 09:20:21 510

510

决于选择的PCB叠层结构。 由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。 PCB叠层设计 “ 层的定义设计原则 1、主芯片相临层

2023-07-27 18:15:06 341

341

决于选择的PCB叠层结构。 由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。 PCB叠层设计 “ 层的定义设计原则 1、主芯片相临层为地

2023-07-31 10:15:02 434

434

决于选择的PCB叠层结构。由于最小线宽和最小线距是取决于PCB类型以及成本要求,受此限制,选择的PCB叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。 一、PCB叠层设计 层的定义设计原则: 1)主芯片相临层

2023-08-01 07:45:01 1760

1760

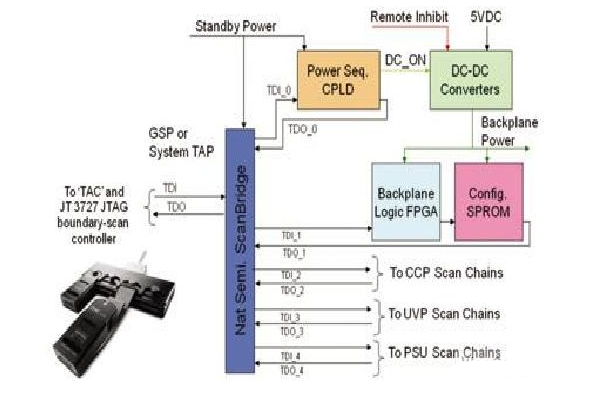

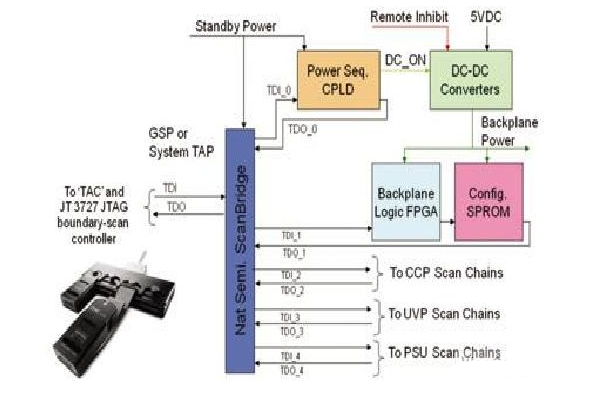

在测试系统中,NI PCI-6533用作位于每个SRI(商店可替换品)上EMId(电子模块标识)设备的接口。它们带有元件编号和序列号数据等等,还包括近故障检测日志。PCI-DIO-96 被作为一个使用CPLD、有160 个管脚的DIO,CPLD 将来自测试控制器PC 的I/O 板卡的输出和输入进行多路复用。

2023-10-17 14:53:08 192

192

该基站的双工器似乎是虹膜耦合腔滤波器,与一些腔间耦合。输入和输出的耦合是T,是谐振器上的一个连接部分,而不是耦合回路。频率由电容帽调节,滤波器是宽信号的带通,如果能看到该过滤器的响应速度,那就更好了。

2023-10-27 10:45:36 325

325

如何设计出低成本和快速PCB工艺的CPWG结构?网上可以找到很多CPWG计算器,但当地层间距小于约走线宽度的30%?50%时,这些计算器就会失效,因为电路板上铜箔走线的高度成为了一个显着因素。

2023-11-08 14:57:40 89

89 确定多层 PCB 板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线 但是制层数越多越利于布线,但是制层数越多越利于布线 板成本和难度也会随之增加。

2023-11-13 15:33:05 156

156 切片分析切片分析就是通过取样、镶嵌、切片、抛磨、腐蚀、观察等一系列手段和步骤获得 PCB 横截面结构的过程。

2023-11-16 16:31:56 156

156 确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于生产厂家来说,层叠结构对称与否是PCB板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到的平衡。

2023-11-22 15:29:56 270

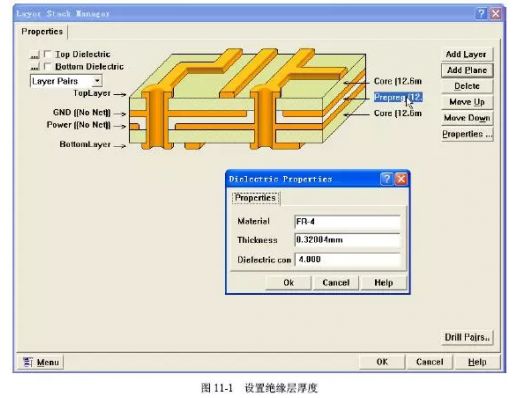

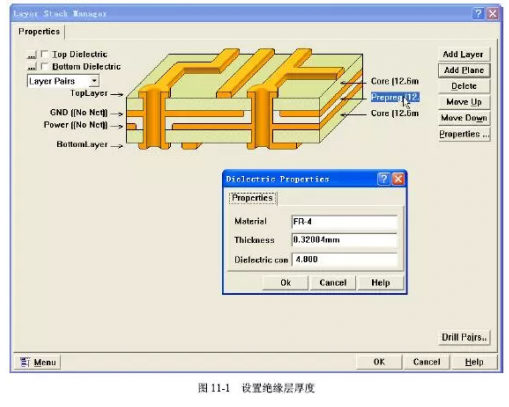

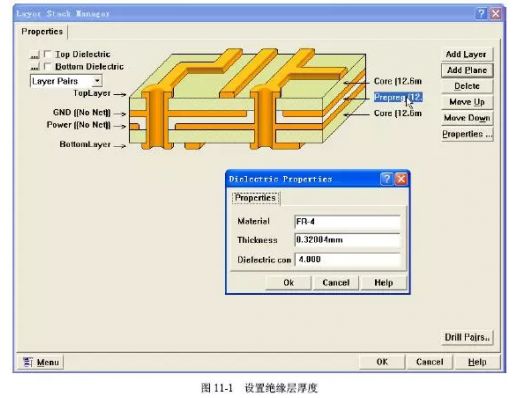

270 1.PCB叠层结构与阻抗计算1.1.Core和PPPCB由Core和Prepreg(半固化片)组成。Core是覆铜板(通常是FR4—玻璃纤维&环氧基树脂),Core的上下表面之间填充的是固态

2024-01-25 17:15:52 1177

1177

正在加载...

电子发烧友App

电子发烧友App

评论