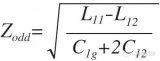

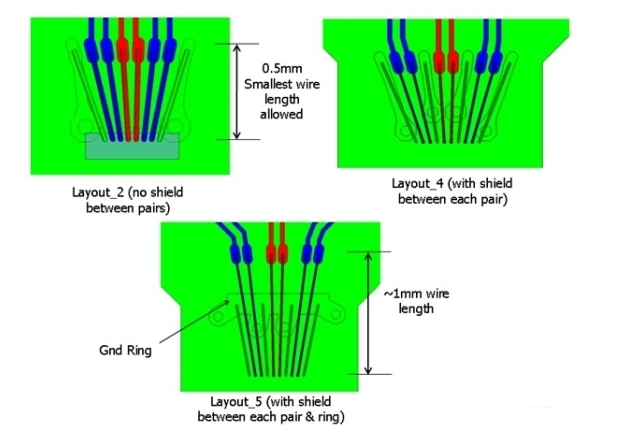

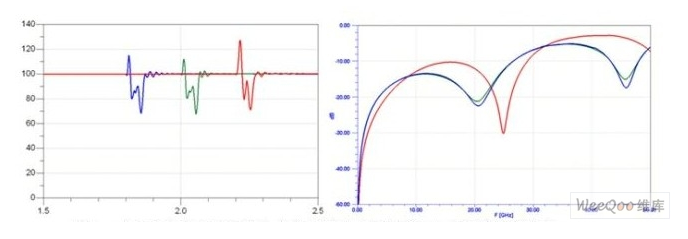

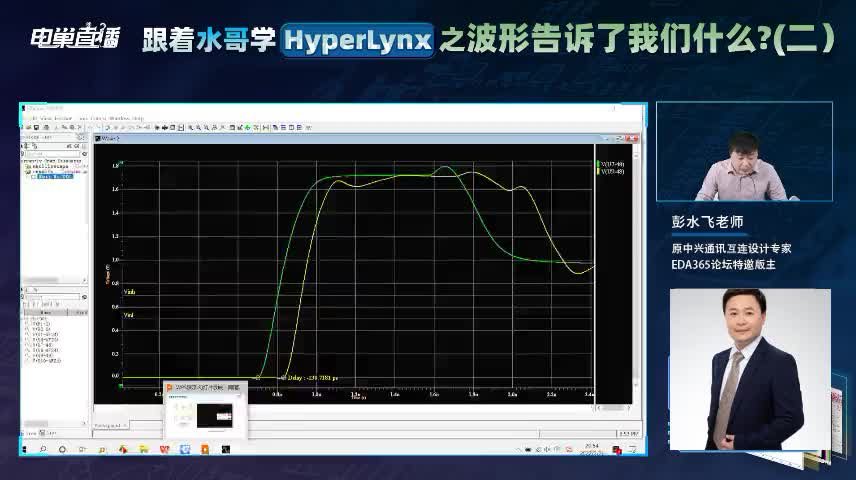

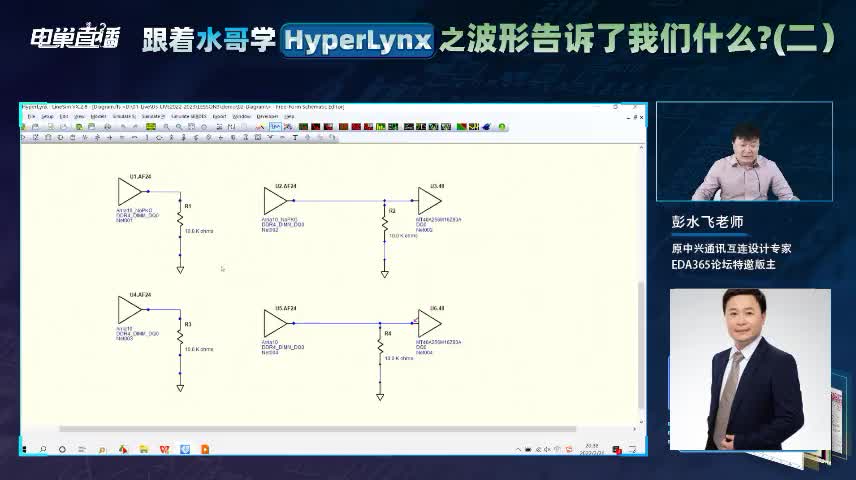

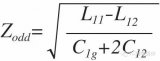

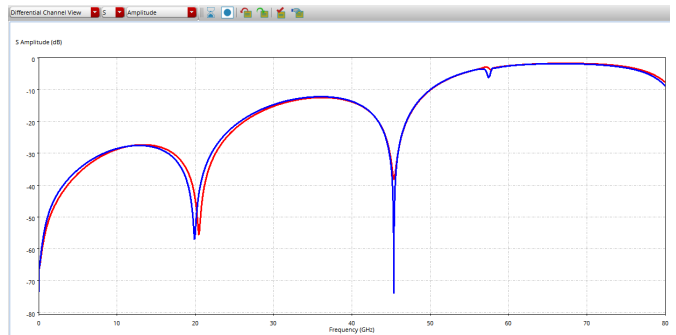

的阻抗不连续性和改善其回波损耗性能,以满足10Gbps SerDes键合线封装规范。 差分阻抗 一个典型的SerDes通道包含使用两个单独互连结构的互补信号发射器和接收器之间的信息交换。两个端点之间

2018-09-12 15:29:27

自己做封装库时,焊盘的大小有没有个设计规范??、要比实际器件管脚的大小大多少啊?、、求指教!!

2013-09-14 10:04:23

自己做封装库时,焊盘的尺寸有没有个设计规范??、要比实际器件管脚的大小大多少啊?、、求指教!!

2013-09-14 11:33:26

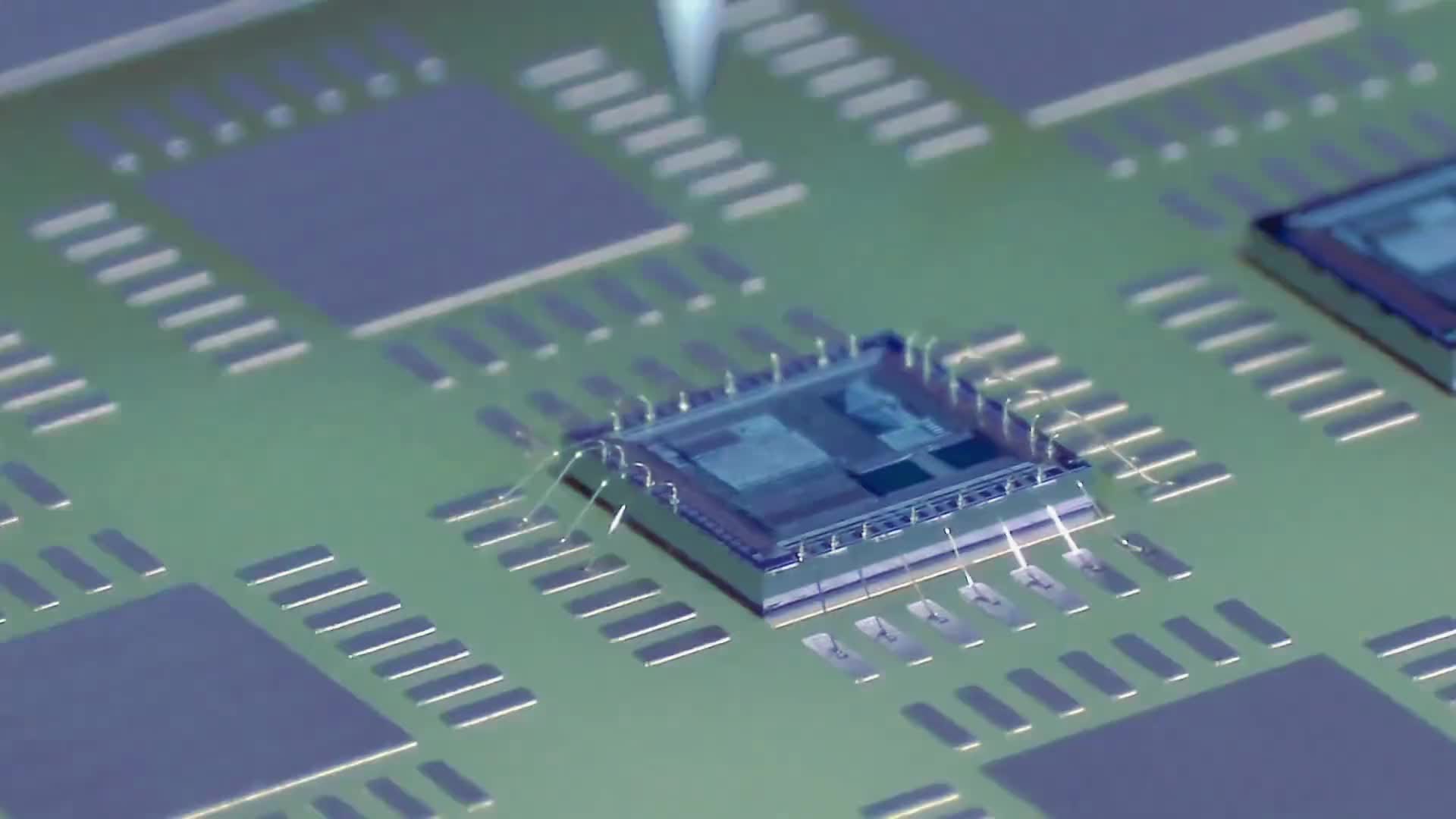

芯片进行封装时,需利用金属线材,将芯片(Chip)及导线架(Lead Frame)做连接,由于封装时,可能有强度不足与污染的风险。此实验目的,即为藉由打线拉力(Wire Bond Ppull)与推力

2018-09-27 16:22:26

(Wire Bond Shear)来验证接合能力,确保其封装可抵抗外在应力。iST宜特检测可针对铝线、金线、铜线进行试验,线径可小至0.8mil以下。参考规范MIL-STD-883 METHOD 2011.7JESD22-B116

2018-11-30 16:00:20

被压缩,即使是在需要许多种供电电压和实际输出功率不断增加的情况。先进的封装形式,例如DaulCool NexFET功率MOSFET就有助于工程师在标准封装中满足这些需求。采用了NexFET技术的功率

2012-12-06 14:32:55

BGA封装如何布线走线

2009-04-11 13:43:43

和基板介质间还要具有较高的粘附性能。 BGA封装技术通常采用引线键合、等离子清洗、模塑封装、装配焊料球、回流焊等工艺流程。引线键合PBGA的封装工艺流程包括PBGA基板的制备和封装

2023-04-11 15:52:37

加速了对新型微电子封装技术的研究与开发,诸如球形触点阵列封装(Ball grid array,简称BGA ) 技术,芯片尺寸封装(Chipscalepackage,简称CSP) 技术,直接芯片键合

2015-10-21 17:40:21

纯净的金属表面紧密接触达到原子间的结合,从而形成焊接。主要焊接材料为铝线焊头,一般为楔形。 (3)金丝焊 球焊在引线键合中是最具代表性的焊接技术,因为现在的半导体封装二、三极管封装都采用AU线球焊

2018-09-11 15:27:57

90’s to 45’s ,把其他的勾都去掉,这样进行优化时就不会将设计者故意弯曲的走线拉直或变形。二、Cadence 做封装库要注意些什么?做封装既可以在Allegro中File-》New-

2019-05-21 10:11:28

文章目录1、GPIO构件封装方法与规范2、利用构件方法控制小灯闪烁3、工程文件组织框架与第一个C语言工程分析1、GPIO构件封装方法与规范构件封装建议、必要性与优点建议按底层硬件操作功能封装构件

2021-11-08 06:58:21

MCM-L是采用片状多层基板的MCM。MCM-L技术本来是高端有高密度封装要求的PCB技术,适用于采用键合和FC工艺的MCM。MCM-L不适用有长期可靠性要求和使用环境温差大的场合。

2020-03-19 09:00:46

MOSFET封装伸援助之手 满足芯片组移动新功能

2021-05-10 06:54:58

PADS如何画蛇形走线元件封装:比如用PADS画一个引脚的蓝牙天线或者2个引脚的天线,天线铜箔是蛇形走线的。

2020-07-30 10:06:57

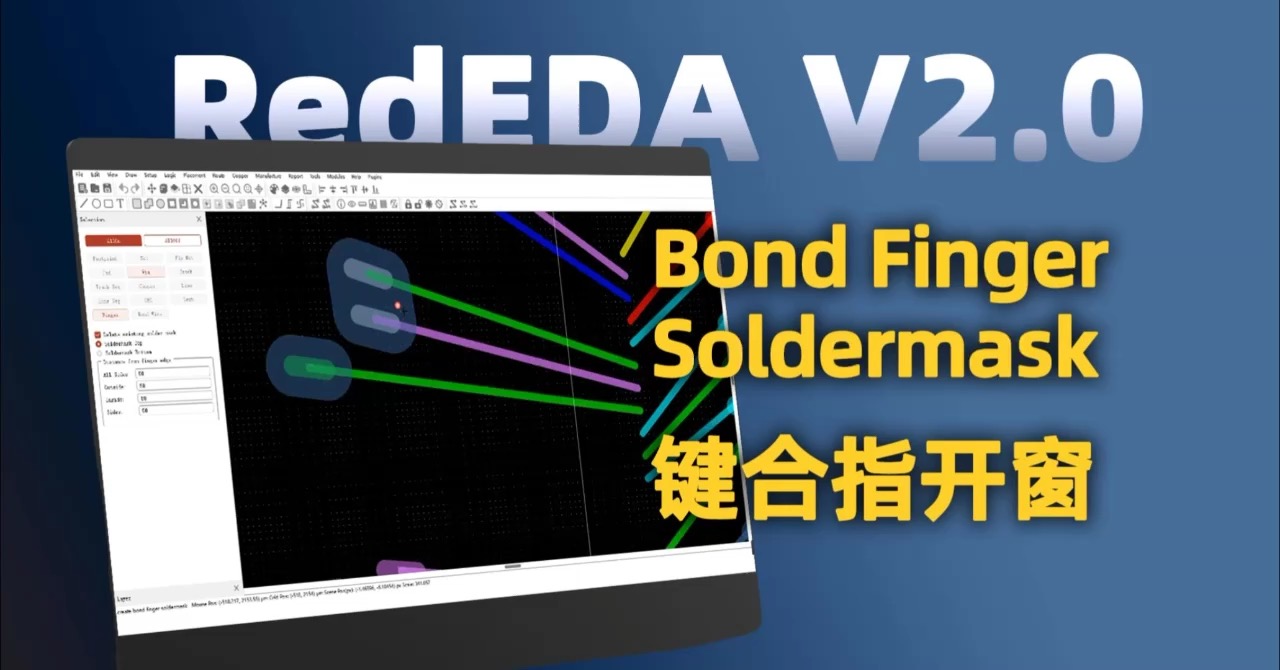

PADS异形封装,我想画个封装,想在封装上用个2D线画个小区域,让这个小区域可以盖绿油,我用阻焊层的2D线画了还是不显示阻焊层怎么办?

2014-11-19 17:52:08

。人们希望防焊膜材料(液态或干膜)将其下面的电路元器件完全封装,以保护其免受操作环境中各种侵蚀的影响。使用干膜防焊膜时为了达到这一目的,所选用的覆膜在压合过程中必须能够布满电路上的所有焊垫和印制线,一

2013-02-25 11:37:02

树脂),其组件符合工业规范要求。图2 采用键合线的PQFN封装图3 采用铜片的PQFN封装 例如,PQFN 5×6铜片封装可在与现有SO-8相当的工业标准尺寸中,实现优于0.5mΩ的电阻,从裸片到

2018-09-12 15:14:20

线放入DBC衬底上的连接装置中,从而形成完整的封装。 除了Sn96.5-Ag3.5焊料外,还对SiN衬底上用于瞬态液相(TLP)键合工艺的另外两种无铅芯片粘接系统进行了研究。在键合过程中,通过互扩散

2018-09-11 16:12:04

存储器控制器用户指南列出了数据,地址,控制和时钟信号的长度匹配要求。给出的数字是否必须补偿FPGA和DDR2封装内的键合线长度?如果是这样,我在哪里可以找到这些长度?谢谢,TL以上来自于谷歌翻译以下

2019-03-15 10:06:16

本帖最后由 eehome 于 2013-1-5 10:11 编辑

connex金线键合机编程

2012-05-19 09:03:56

印刷电路板上的半导体封装。在大多数 BGA 中,半导体芯片和封装基板是通过金线键合连接的。这些封装基板和主板通过焊球连接。为了满足这些连接所需的可靠性,封装基板两侧的端子均镀金。化学镀金在更高

2021-07-09 10:29:30

的尺寸稳定性和低的吸潮性,具有较好的电气性能和高可靠性。金属薄膜、绝缘层和基板介质间还要具有较高的粘附性能。三大BGA封装工艺及流程一、引线键合PBGA的封装工艺流程1、PBGA基板的制备在BT树脂

2018-09-18 13:23:59

芯片键合表面按栅阵形状布置好焊料凸点后,芯片以倒扣方式安装在封装基板上,通过凸点与基板上的焊盘实现电气连接,取代了WB和TAB 在周边布置端子的连接方式。倒装键合完毕后,在芯片与基板间用环氧树脂进行

2017-09-18 11:34:51

无锡一家股份制企业,可以代工COB,陶瓷管壳、金属封管壳和金属陶瓷管壳等产品的封装,具有贴片共晶焊/导电胶工艺、金丝/铝丝键合、气密非气密封盖、激光打标等能力,价格优惠,封装评估的从下单到加工完成

2014-05-29 13:40:03

目前在做砷化镓和磷化铟,在研究bongder和debonder工艺, 主要是超薄片很难处理,so暂定临时键合解键合和薄片清洗流程,因为正面有保护可以做背面工艺,这里有前辈做过这个吗?

2018-12-17 13:55:06

在刚刚使用软件时经常要在封装库里面找需要的封装找好久,今天给大家分享一个规范的 protel封装命名参考,便于大家以后可以更加规范而且也更方便寻找所需的封装。

2020-07-24 09:09:10

请教:最近在书上讲解电感时提到一个名词——键合线,望大家能给出通俗详细解释

2014-06-22 13:21:45

WLP的命名上还存在分歧。CSP晶片级技术非常独特,封装内部并没有采用键合方式。封装芯片的命名也存在分歧。常用名称有:倒装芯片(STMicroelectronics和Dalias

2018-08-27 15:45:31

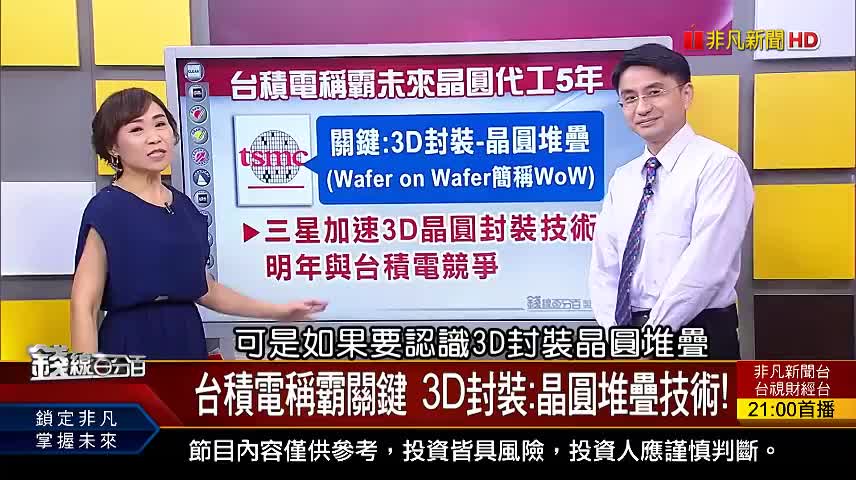

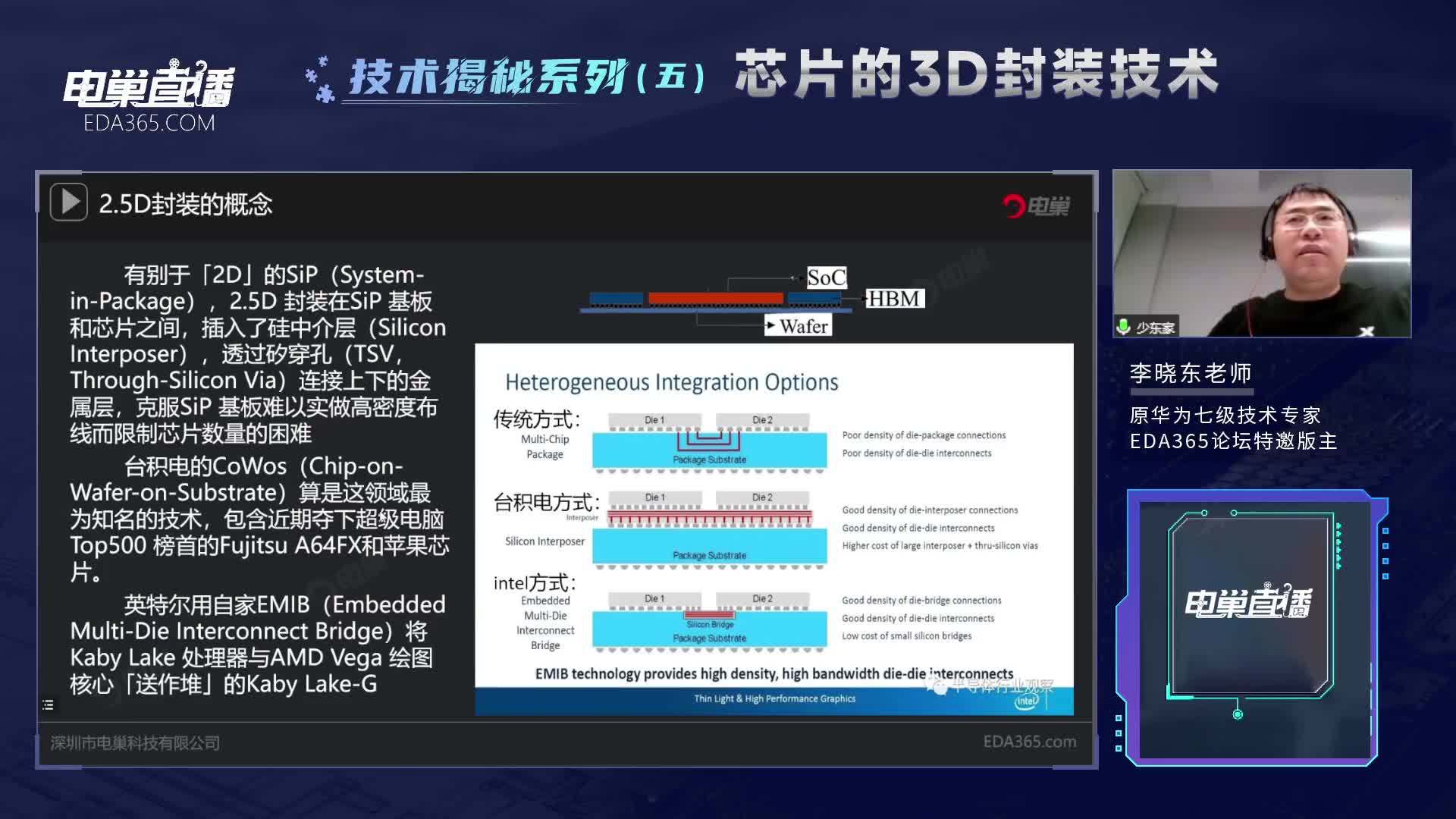

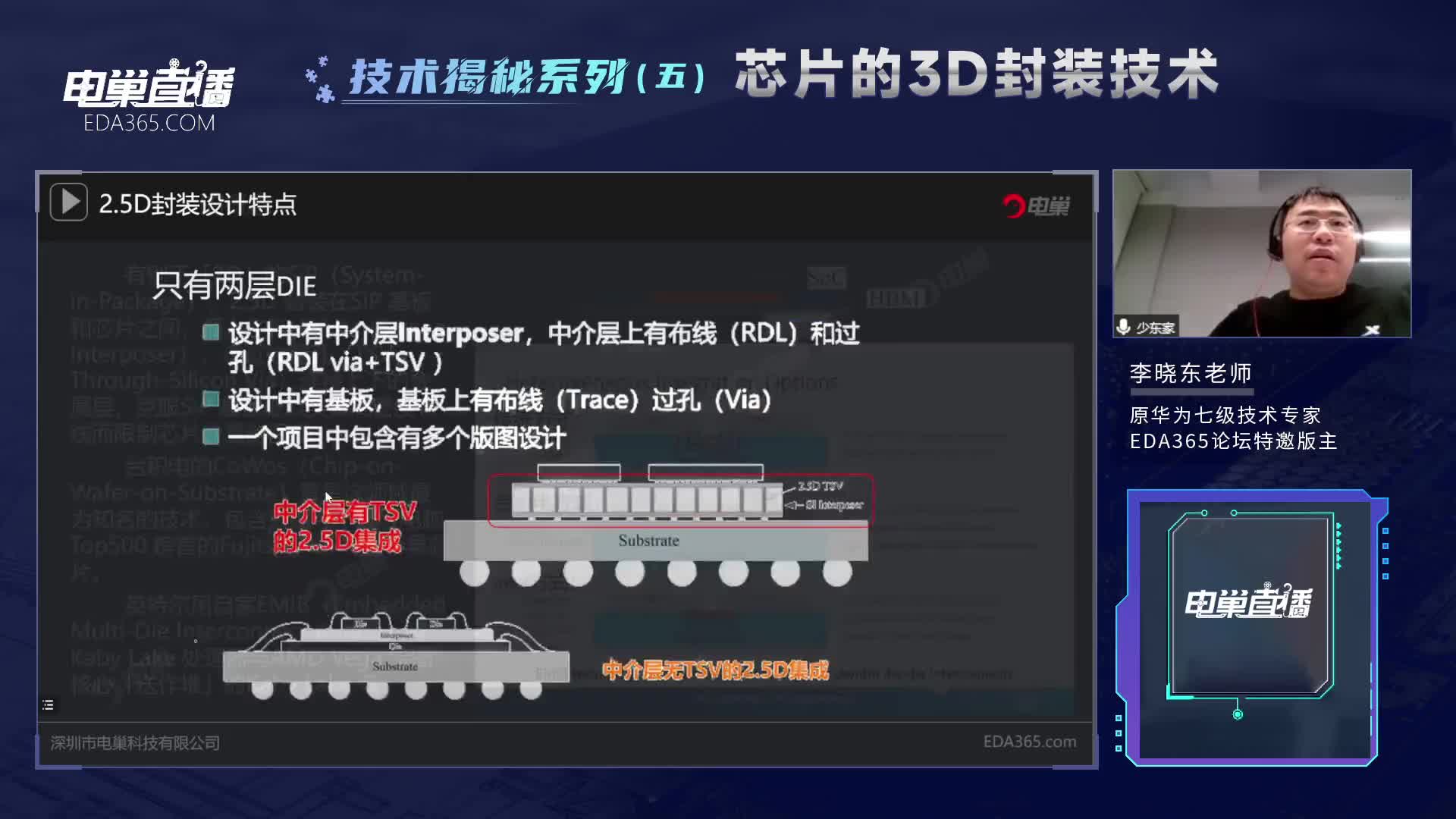

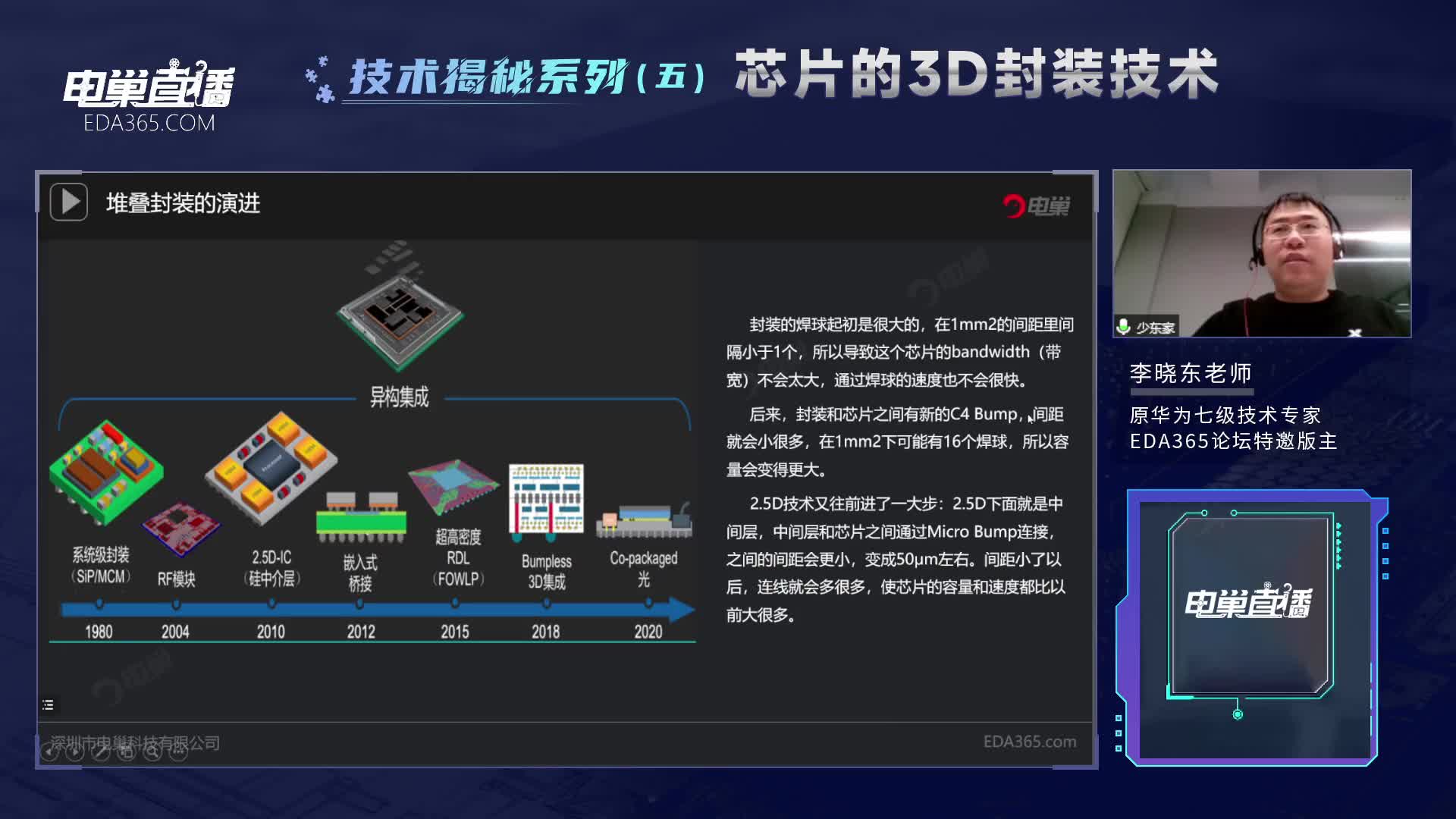

中芯片问的连接距离,持续缩小的封装尺寸促使芯片三维重叠结构的运用,生产效率的提高需要把单个芯片的连接上艺扩展到整个硅片卜进行。硅片键合工艺把多层圆片上下相连同时形成电气和机械连接以满足这些要求。硅片

2018-11-23 17:03:35

而在键合引线和芯片底座上施加的载荷。进行塑封器件组装时出现的爆米花现象就是一个典型的例子。综合载荷应力条件在制造、组装或者操作的过程中,诸如温度和湿气等失效加速因子常常是同时存在的。综合载荷和应力条件常常会进一步加速失效。这一特点常被应用于以缺陷部件筛选和易失效封装器件鉴别为目的的加速试验设计。

2021-11-19 06:30:00

此文档介绍了PCB的一些常用封装的设计规范,共享

2018-06-08 11:16:52

分享一款不错的优化远程及遥测应用的视频SERDES电路

2021-06-03 06:31:04

本帖最后由 知秋一叶03 于 2021-2-5 09:31 编辑

了解管脚焊盘,器件封装的命名规范

2021-02-05 09:29:14

史上最全的PCB封装命名规范

2017-11-27 17:23:32

史上最全的PCB封装命名规范

2015-06-12 15:58:56

找了一圈,发现做线键合机的比较多,想知道做晶圆键合wafer bonding的中国厂家。

2021-04-28 14:34:57

在线监测导通电压Von,以观察引线键合点失效的后果并验证检测方法的可行性。图12给出了在每个引线键合点被剥离后的半个调制周期内集电极电流Ion与Von的函数关系。这显示了在不同电流值下,不同引线键合点

2019-03-20 05:21:33

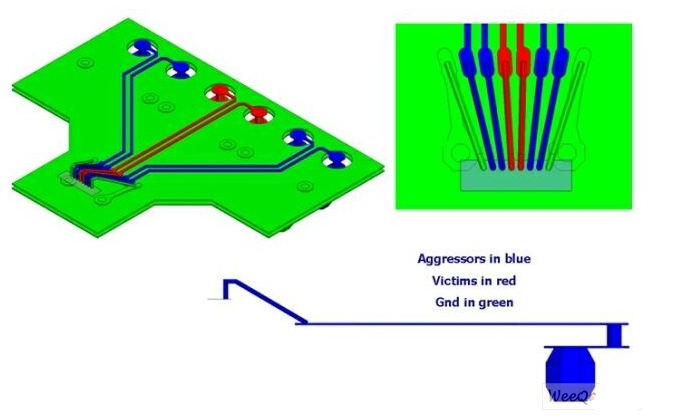

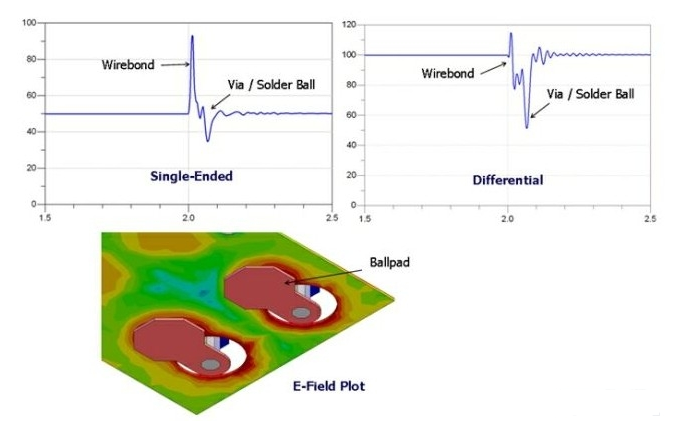

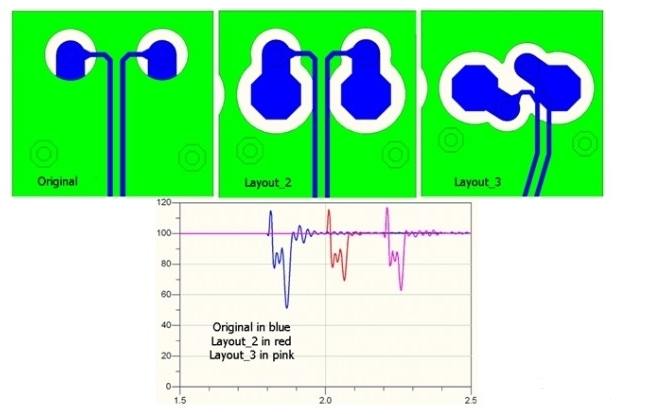

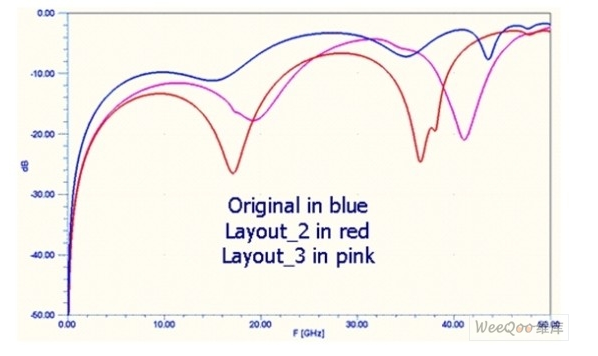

本文将讨论通过优化封装内的阻抗不连续性和改善其回波损耗性能,以满足10Gbps SerDes键合线封装规范。

2021-04-25 07:42:13

如何实现一体化芯片-封装协同设计系统的设计?如何优化封装和芯片接口设计?

2021-04-21 07:01:10

的距离之后,差分线的阻抗也随之发生变化,需要调整差分走线满足目标阻抗的要求。芯片的SMT焊盘距离参考平面距离变小之后阻抗也会变低,需要在SMT焊盘的参考平面上进行挖空处理来优化SMT焊盘的阻抗。具体挖空

2018-09-11 11:50:13

(参考APEC⒛00)。嵌入功率器件的平面金属化封装技术是其中较好的一种。 图1 不用引线键合的集成功率模块 图2给出了一个集成模块的剖面图,应用了嵌入功率器件的多层集成封装技术。包括:散热板、基板、绝缘

2018-11-23 16:56:26

首先通过焊锡将芯片背部焊接在基板上,再通过金属键合线引出正面电极,最后进行塑封或者灌胶。传统封装技术成熟,成本低,而且可兼容和替代原有 Si 基器件。 但是,传统封装结构导致其杂散电感参数较大,在

2023-02-22 16:06:08

论述了微电子封装技术的发展历程 发展现状及发展趋势 主要介绍了微电子封装技术中的芯片级互联技术与微电子装联技术 芯片级互联技术包括引线键合技术 载带自动焊技术 倒装芯片技术 倒装芯片技术是目前

2013-12-24 16:55:06

微电子封装,首先我们要叙述一下三级封装的概念。一般说来,微电子封装分为三级。所谓一级封装就是在半导体圆片裂片以后,将一个或多个集成电路芯片用适宜的封装形式封装起来,并使芯片的焊区与封装的外引脚用引线键合

2018-09-12 15:15:28

有人又将其称为圆片级-芯片尺寸封装(WLP-CSP),以晶圆圆片为加工对象,在晶圆上封装芯片。晶圆封装中最关键的工艺为晶圆键合,即是通过化学或物理的方法将两片晶圆结合在一起,以达到密封效果。如下

2021-02-23 16:35:18

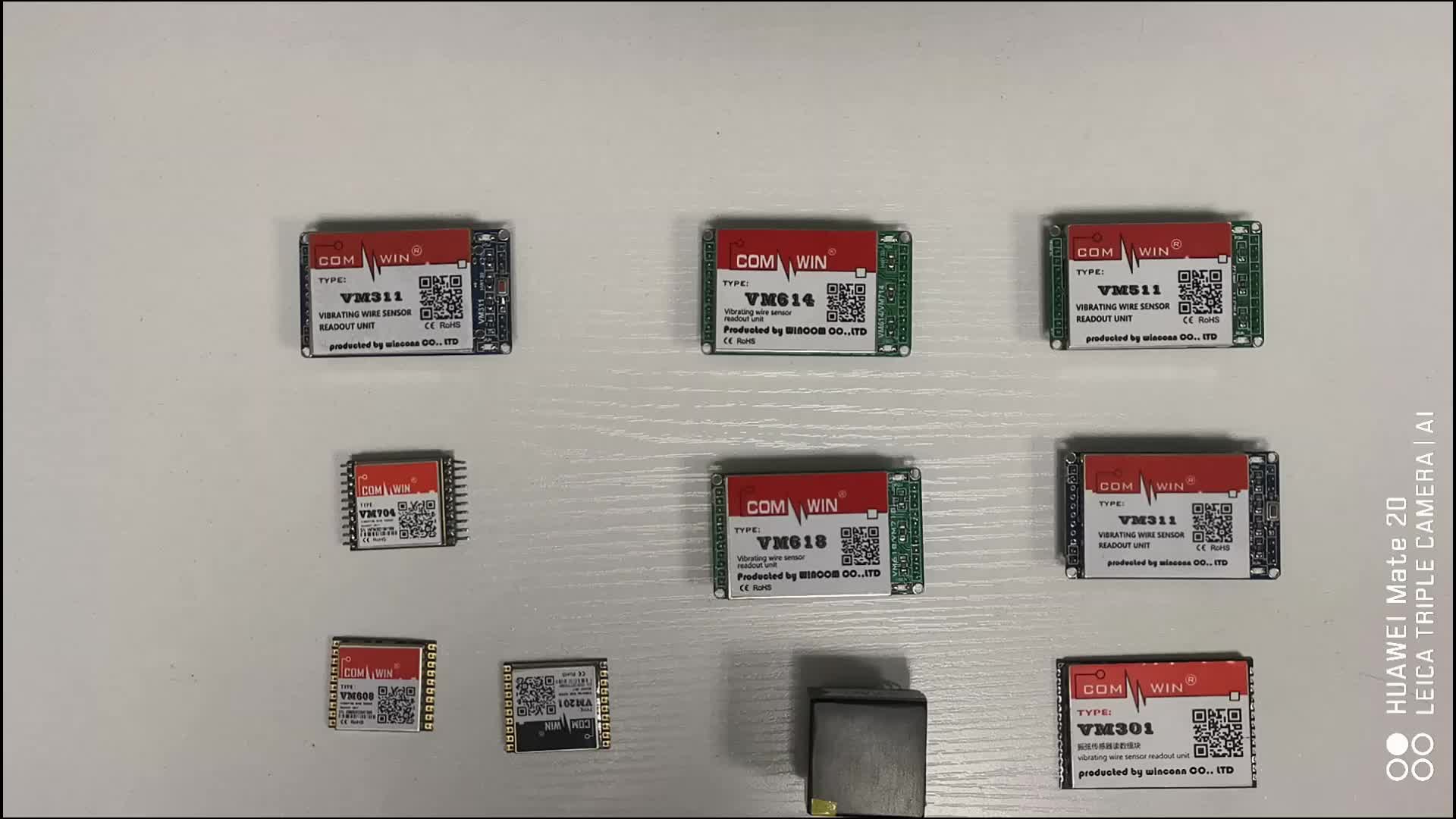

满足加速度大于30000g应用场景。

完成大尺寸QFN封装金线键合工艺开发。

其它信息请加qq了解。(qq:972186757)

2024-03-10 14:14:51

。金丝焊也叫热(压)(超)声焊主要键合材料为金(AU)线焊头为球形故为球焊。 COB封装流程 第一步:扩晶。采用扩张机将厂商提供的整张LED晶片薄膜均匀扩张,使附着在薄膜表面紧密排列的LED晶粒拉开

2018-09-17 17:12:09

贴膜(W-M)→晶圆表面去膜(WDP)→晶圆烘烤(WBK)→晶圆切割(SAW)→切割后清洗(DWC)→晶圆切割后检查(PSI)→紫外线照射(U-V)→晶片粘结(DB)→银胶固化(CRG)→引线键合(WB

2013-12-09 21:48:32

PCB的封装是器件物料在PCB中的映射,封装是否处理规范牵涉到器件的贴片装配,我们需要正确的处理封装数据,满足实际生产的需求,有的工程师做的封装无法满足手工贴片,有的无法满足机器贴片,也有的封装

2023-04-17 16:53:30

;工艺设备复杂,成本,高,壳内零件较多易引起芯片沾污。引线键合技术本身存在诸多技术缺陷表现在:多根引线并联会产生邻近效应,导致同一硅片的键合线之间或同一模块内的不同硅片的键合线之间电流分布不均;由于高频

2018-08-28 11:58:28

硅-硅直接键合技术主要应用于SOI、MEMS和大功率器件,按照结构又可以分为两大类:一类是键合衬底材料,包括用于高频、抗辐射和VSIL的SOI衬底和用于大功率高压器件的类外延的疏水键合N+-N-或

2018-11-23 11:05:56

硅衬底和砷化镓衬底金金键合后,晶圆粉碎是什么原因,偶发性异常,找不出规律,有大佬清楚吗,求助!

2023-03-01 14:54:11

微电子封装,首先我们要叙述一下三级封装的概念。一般说来,微电子封装分为三级。所谓一级封装就是在半导体圆片裂片以后,将一个或多个集成电路芯片用适宜的封装形式封装起来,并使芯片的焊区与封装的外引脚用引线键合

2023-12-11 01:02:56

现在有哪些芯片是将IC与外围电路做在一起的(封装成一个IC)?同事说到后面会把晶振等较大的器件也会封装进去,那这种IC在后面是不是一种大趋势?如果是这样,怎样能保证匹配和性能,因为封装到里,可能无法靠调整外围电路优化,个人还不是太懂,请各位发表下自己的观点帮忙了解些~~

2015-07-20 11:49:43

芯片封装键合技术各种微互连方式简介微互连技术简介定义:将芯片凸点电极与载带的引线连接,经过切断、冲压等工艺封装而成。载带:即带状载体,是指带状绝缘薄膜上载有由覆 铜箔经蚀刻而形成的引线框架,而且芯片

2012-01-13 14:58:34

芯片(Die)必须与构装基板完成电路连接才能发挥既有的功能,焊线作业就是将芯片(Die)上的信号以金属线链接到基板。iST宜特针对客户在芯片打线封装(Bonding, COB, Quick

2018-08-29 15:35:01

芯片封装设计中的wire_bonding知识介绍Wire Bond/金线键合: 指在对芯片和基板间的胶粘剂处理以使其有更好的粘结性能后,用高纯金线把芯片的接口和基板的接口键合 成分为金(纯度为

2012-01-13 15:13:50

1、TAB技术中使用()线而不使用线,从而改善器件的热耗散性能。A、铝B、铜C、金D、银2、陶瓷封装基板的主要成分有()A、金属B、陶瓷 C、玻璃D、高分子塑料3、“塑料封装与陶瓷封装技术均可以制成

2013-01-07 19:19:49

7系列系列中的SERDES是否有最小延迟规范?我想了解如果SERDES直接(最短路径)连接到另一个SERDES以实现GTH收发器之间的最小延迟串行到串行连接,那将是什么样的。

2020-07-22 13:45:34

是要实现电器和热连接。我们应用IGBT过程中,导热性是决定IGBT模块最关键的因素。第二是键合,主要是通过键合线实现芯片与键合线之间的连接。第三是外壳安装。第四是罐封,进行材料填充,事先与外界隔离

2012-09-17 19:22:20

介绍PCB封装的命名规范,让封装库有规律,易查询。

2015-10-29 14:07:56 0

0 制作Altium Designer的封装规范,包括原理图和PCB图的各种参数和必需尺寸等等。

2016-08-03 17:55:44 0

0 本文详细介绍了元器件封装的命名规则,对于规范封装具有相当好的意义

2016-08-18 17:26:55 0

0 详细介绍了各类元器件封装设计规范要求,全面。

2016-08-29 16:05:01 0

0 PCB元件封装设计规范,做封装时有用

2016-12-16 21:20:06 0

0 基于_群封装_技术的RADIUS认证优化_高宝

2017-03-19 11:31:31 0

0 对于10Gbps及以上数据速率的SerDes,每个数据位的单位间隔是随着近 20~30ps的信号上升/下降时间而缩短的。

2018-07-18 17:18:48 7390

7390

几乎每天都有小伙伴在后台留言说想要 PCB 封装设计的规范文档,小编为了满足大家,今天就给大家上菜了,希望大家喜欢,记得帮忙转发,点赞哦,谢谢您。 器件封装设计原则: 1、公司封装库中没有的器件

2022-12-09 10:59:45 505

505 如果设计不合适,一个通道中的这些多重转换将会影响信号完整性性能。在10Gbps及以上,通过最大限度地减少阻抗不连续性,得到适合的互连设计已成为提高系统性能的一个重要的考虑因素。由于封装内有许多不连续区,该收发器封装在提高回波损耗性能方面存在一个重要瓶颈。

2020-11-12 15:31:05 2606

2606

PCB的封装是器件物料在PCB中的映射,封装是否处理规范牵涉到器件的贴片装配,我们需要正确的处理封装数据,满足实际生产的需求,有的工程师做的封装无法满足手工贴片,有的无法满足机器贴片,也有的封装

2021-01-21 11:27:06 8765

8765

适用于主流EDA工具的封装命名规范,规范的命名可以提高审核效率,较少工程师犯错。

2022-10-21 16:06:45 0

0 PCB 封装命名规范注解 1. 命名中所涉及到的任何数据均由相应计算公式或规格书获得 2. PCB 库命名只涉及二维尺寸,封装的高度 H 不做标注 3. 命名格式中字母含义解释 [PKT

2022-12-09 10:40:09 0

0 自动化建模和优化112G封装过孔 ——封装Core层过孔和BGA焊盘区域的阻抗优化

2023-11-29 15:19:51 179

179

电子发烧友App

电子发烧友App

评论