规则一:高速信号走线屏蔽规则在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。图1 高速

2018-11-28 11:14:18

高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。7. 有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2017-07-07 11:45:56

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-05-23 08:52:37

效的减少相互间的耦合。6. 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。7. 有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2014-08-13 15:44:05

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高速PCB设计中

2019-08-05 06:40:24

控制标准是100Ω;误差不能大于±10%; 走线避免直角,以免产生反射,影响高速传输性能; 参考层:MIPI信号线下方一定要有参考层(推荐用地层),且一定要保证参考层的连续性(即在MIPI信号

2023-04-12 15:08:27

的间距最好是0.5mm以上。这样有助于避免交互干扰。另一种选择达到90 ohm的差分阻抗的方法。可以在USB的差分信号线对加上6pF到地。因为有些设计需要这些,但是当有些PCB设计达不到90 ohm

2023-04-13 16:09:54

夹杂在差分信号之间的非查份(单独一条)走线方式有什么要求吗?这就是要画的连接线PCB高速差分信号线四层怎么弄,还要求阻抗,就是一个连接线

2023-04-07 17:46:45

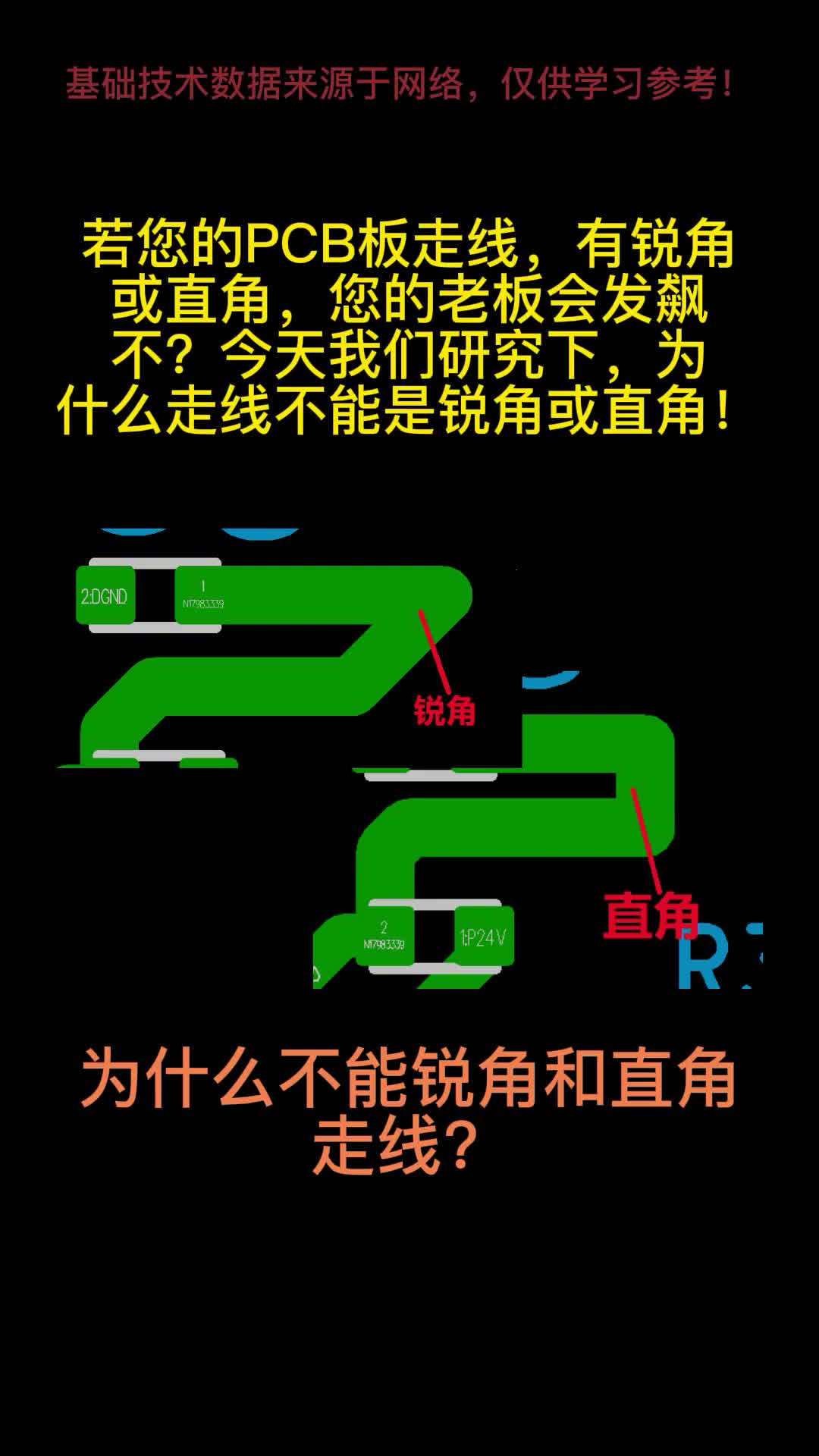

不出来,高速PCB设计工程师的重点还是应该放在布局,电源/地设计,走线设计,过孔等其他方面。当然,尽管直角走线带来的影响不是很严重,但并不是说我们以后都可以走直角线,注意细节是每个优秀工程师必备的基本素质

2014-11-18 17:29:31

PCB四层板中我将中间两层设置成了信号层,能否给点实用的布线的经验???当布完线后该怎么进行敷铜呢?需要在哪层进行敷铜,最好是能说说为啥。如果将中间层设置成电源层和地层,那中间层还能走信号线吗???需要注意些什么???在此谢过。。。。

2023-04-11 17:33:46

,同时走线过细也使阻抗无法降低,那么在高速(>100MHz)高密度PCB设计中有哪些技巧? 在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意

2012-03-03 12:39:55

1.1 PCB板上预划分数字、模拟、DAA信号布线区域。1.2 数字、模拟元器件及相应走线尽量分开并放置於各自的布线区域内。1.3 高速数字信号走线尽量短。1.4 敏感模拟信号走线尽量短。1.5

2019-05-30 06:58:19

。 5、可以经常采用任意角度的蛇形走线,能有效的减少相互间的耦合。 6、高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以只作时序匹配之用而无其它目的。 7、有时可以考虑螺旋走线的方式进行绕线,仿真表明,其效果要优于正常的蛇形走线。

2018-12-05 09:36:02

PCB设计走线的宽度与最大允许电流有何关系?PCB设计走线的宽度与铜厚有何关系?

2021-10-11 09:49:14

PCB设计走线的规则是什么

2021-03-17 06:36:28

减少布线层,降低PCB成本。 当然,这样做的代价是冒一些技术风险,甚至牺牲一半成功率。 对于背板的层叠设计,鉴于常见背板很难做到相邻走线互相垂直,不可避免地出现平面长距离布线。 对于高速背板

2023-04-12 15:12:13

硬件工程师做久了自然有自己处理电路板的一套方法,也许不是最好的办法,自己却能理解其中的意义。但是工作中还是要按照最完美的办法进行操作,本期我们就来了解一下关于高速信号走线准则到底有哪几条是你不清楚的?

2020-10-30 08:33:48

:—-Top—-GND—-Power—-Sig1—-GND—-Bottom注: 原则上3层信号层,3层电源层,其中GND为2、5两层,3、4中间层为Power和中间信号层。若中间信号层走线较少,可适当在中间信号层对Power进行敷铜

2019-05-21 09:16:36

请问大伙PCB设计中,常见的串口通讯线(TX、RX)是否属于高速信号线?然后高速信号的标准到底是什么?在网上浏览了一些相关知识,感觉始终不太理解。

2023-01-26 20:39:13

高速信号在走线的时候出现直角有什么影响?A、B、AB、D类功放分别是什么意思?PCB设计为什么要大面积敷t铜?

2021-10-18 06:13:38

电容,反射,EMI等效应在TDR测试中几乎体现不出来,高速PCB设计工程师的重点还是应该放在布局,电源/地设计,走线设计,过孔等其他方面。当然,尽管直角走线带来的影响不是很严重,但并不是说我们以后都可以

2018-09-17 17:31:52

EMI所加的电阻电容或ferrite bead, 不能造成信号的一些电气特性不符合规范。 所以, 最好先用安排走线和PCB叠层的技巧来解决或减少EMI的问题, 如高速信号走内层。 最后才用电阻电容

2012-08-05 19:33:41

走线的相互干扰增强,同时走线过细也使阻抗无法降低,请专家介绍在高速(>100MHz)高密度PCB设计中的技巧? 在设计高速高密度PCB时,串扰(crosstalk interference

2017-01-03 15:10:49

的要求有很多冲突。但基本原则是因 EMI 所加的电阻电容或 ferrite bead, 不能造成信号的一些电气特性不符合规范。 所以, 最好先用安排走线和 PCB 迭层的技巧来解决或减少 EMI

2021-09-19 14:47:06

高速布线与 EMI 的要求有很多冲突。但基本原则是因 EMI 所加的电阻电容或 ferrite bead, 不能造成信号的一些电气特性不符合规范。 所以, 最好先用安排走线和 PCB 迭层的技巧来

2016-09-12 14:53:53

和过孔传输时延在PCB设计时候,经常会遇到走线换层,走线换层必须借助于过孔。但长度相等的过孔和走线之间的时延并不相等。过孔的时延可以用式3.3表示TD_via=√LC 3.3 其中TD_via表示信号经过

2014-10-21 09:54:56

,减小绕线间平行走线长度。 4.小结 在PCB设计时候要将等长的设计观念逐步向等时设计转变,在对时序或者等长要求高的设计尤其需要注意串扰,绕线方式,不同层走线,过孔时延等方面对时序的影响。丰富的SI(信号完整性)知识和正确的仿真方法可以帮助设计去评估PCB板上的传输时延,从而提高设计的质量。

2014-10-21 09:51:22

高速PCB信号走线的九条规则.pdf(220.78 KB)

2019-09-16 07:26:43

误区一:认为差分信号不需要地平面作为回流路径,或者认为差分走线彼此为对方提供回流途径。造成这种误区的原因是被表面现象迷惑,或者对高速信号传输的机理认识还不够深入。从图1-8-15的接收端的结构可以

2012-12-18 12:03:00

误区一:认为差分信号不需要地平面作为回流路径,或者认为差分走线彼此为对方提供回流途径。造成这种误区的原因是被表面现象迷惑,或者对高速信号传输的机理认识还不够深入。从图1-8-15的接收端的结构可以

2012-12-19 16:52:38

为了避免不理想返回路径的影响,可以采用差分对走线。为了获得较好的信号完整性,可以选用差分对来对高速信号进行走线,如图1所示,LVDS电平的传输就采用差分传输线的方式。 图1 差分对走线实例

2018-11-27 10:56:15

信号的特性阻抗连续规则高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射。也就是说,同层的布线的宽度必须连续,不同层的走线阻抗必须连续。规则五、高速PCB设计的布线方向规则

2021-03-31 06:00:00

通过高速PCB来控制解决。做了4年的EMI设计,一些心得和大家交流、交流。规则一、高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只

2022-04-18 15:22:08

区域。如果Tr≤2Tpd,信号落在问题区域。对于落在不确定区域及问题区域的信号,应该使用高速布线方法。(四)、什么是传输线 PCB板上的走线可等效为下图所示的串联和并联的电容、电阻和电感结构。串联

2015-05-05 09:30:27

高速信号区域相应的电源平面或地平面尽可能保持完整(11)建议布线分布均匀,大面积无布线的区域需要辅铜,但要求不影响阻抗控制(12)建议所有布线需倒角,倒角角度推荐45度(13)建议防止信号线在相邻层

2017-02-16 15:06:01

。(8)建议布线到板边的距离大于2MM(9)建议信号线优先选择内层布线(10)建议高速信号区域相应的电源平面或地平面尽可能保持完整(11)建议布线分布均匀,大面积无布线的区域需要辅铜,但要求不影响阻抗

2017-02-10 10:42:11

/0.86mm 的过孔,也可以尝试非穿导孔;对于电源或地线的过孔则可以考虑使用较大尺寸,以减小阻抗;2.PCB 上的信号走线尽量不换层,也就是说尽量减少过孔;3.电源和地的管脚要就近做过孔,过孔和管脚之间

2016-12-20 15:51:03

高速PCB设计之一 何为高速PCB设计电子产品的高速化、高密化,给PCB设计工程师带来新的挑战。PCB设计不再是产品硬件开发的附属,而成为产品硬件开发中“前端IC,后端PCB,SE集成”3个环节中

2014-10-21 09:41:25

。 问:在高速PCB设计中,串扰与信号线的速率、走线的方向等有什么关系?需要注意哪些设计指标来避免出现串扰等问题? 答:串扰会影响边沿速率,一般来说,一组总线传输方向相同时,串扰因素会使边沿速率变慢

2019-01-11 10:55:05

高速PCB设计的信号完整性问题 随着器件工作频率越来越高,高速PCB设计所面临的信号完整性等问题成爲传统设计的一个瓶颈,工程师在设计出完整的解决方案上面临越来越大的挑战。尽管有关的高速仿真工具

2012-10-17 15:59:48

高速PCB设计的叠层问题

2009-05-16 20:51:30

本期讲解PCB设计中高速信号关键信号的布线要求。一、时钟信号布线要求在数字电路设计中,时钟信号是一种在高态与低态之间振荡的信号,决定着电路的性能。时钟电路在数字电路中点有重要地位,同时又是产生

2017-10-19 14:25:36

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地

2016-01-19 22:50:31

。 而绝对的要求是控制两个器件之间的走线延迟为某一个值,比如器件A、B之间的延迟为Ins,而这样的要求往往由高速电路设计者提出,而由PCB工程师去实现。要满足这个要求,就必须知道信号的传播速度c但需要

2018-11-27 15:22:54

以PCB设计软件allegro进行操作,以四层板的设置为例进行正片层的光绘设置。打开allegro操作界面、在ALLGRO的操作命令:具体的生成步骤:(正片层的光绘设置、以生成TOP层为例)首先把ALLEGRO

2017-01-20 10:22:15

、PCB的可靠性设计4、电磁兼容性和PCB设计约束三、1、改进电路设计规程提高可测性2、混合信号PCB的分区设计3、蛇形走线的作用4、确保信号完整性的电路板设计准则四、1、印制电路板的可靠性设计五、1

2012-07-13 16:18:40

比如射频走线或者一些高速信号线,必须走多层板外层还是内层也可以走线

2023-10-07 08:22:18

高速电路信号完整性分析与设计—PCB设计多层印制板分层及堆叠中应遵徇的基本原则;电源平面应尽量靠近接地平面。布线层应安排与映象平面层相邻。重要信号线应紧临地层。[hide] [/hide][此贴子已经被作者于2009-9-12 10:38:14编辑过]

2009-09-12 10:37:02

PCB设计时,有时候需要在不增加PCB走线宽度的情况下提高该走线通过大电流的能力(载流能力),通常的方法是给该导线镀锡(或者上锡);下面以在PCB顶层走线镀锡为例,使用AD09软件,简单介绍如何走线上锡处理:1、 选择TopLayer层,确定需要走线的地方,画一条导线;(图文详解见附件)

2019-09-06 15:57:30

PCB Layout中的走线策略布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见

2009-08-20 20:58:49

的层又分为电源层、底线层和信号层,而层的选择中,层的相对位置、地平面/电源的分割、PCB的布线、接口电路的处理又有这非常大影响。 层的选择第一步是层数,层数的选择不宜太多也不宜太少,太多则信号线过于密集

2015-01-08 15:26:03

一线工程师整理的PCB设计技巧,包含高速,混合信号和低电平应用,例举众多实例说明。工程师们绝对福利~PCB设计是一门艺术,好的PCB设计需要花费数十年的时间才能不断磨砺而成。设计一个可靠的高速,混合

2017-07-26 17:37:44

作用,这种结构在高频的(10G以上)IC封装PCB设计中经常会用采用,被称为CPW结构,可以保证严格的差分阻抗控制(2Z0),如图1-8-19。差分走线也可以走在不同的信号层中,但一般不建议这种走法

2019-03-18 21:38:12

一博科技自媒体高速先生原创文 | 黄刚 古语有云:窈窕淑女,君子好逑,如果要各位PCB行业的高富帅从高高瘦瘦和矮胖矮胖这两种身材的美女中去选择的话,相信大多数人都会选择前者吧。那么如果传输线也有

2020-03-19 11:16:47

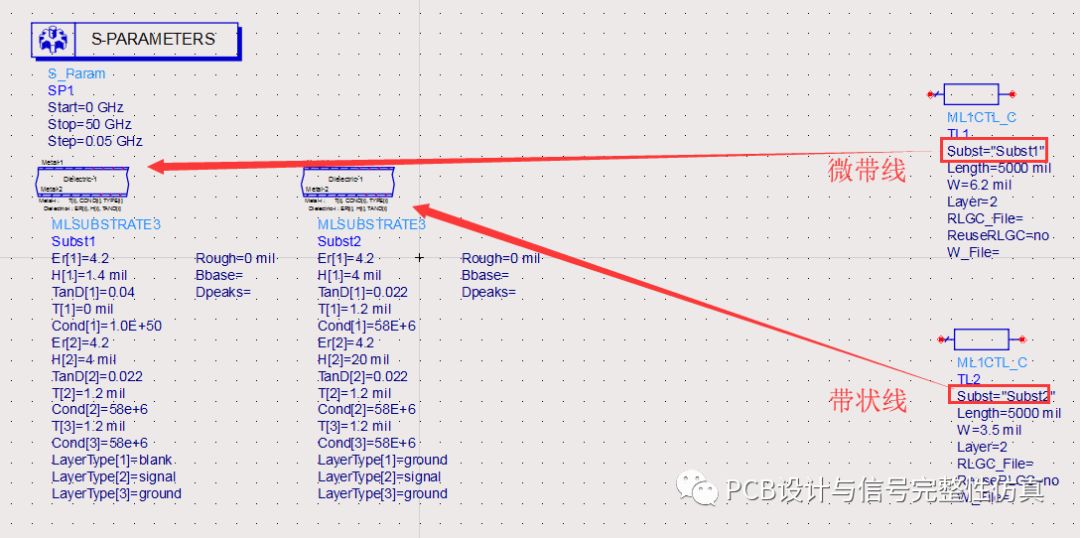

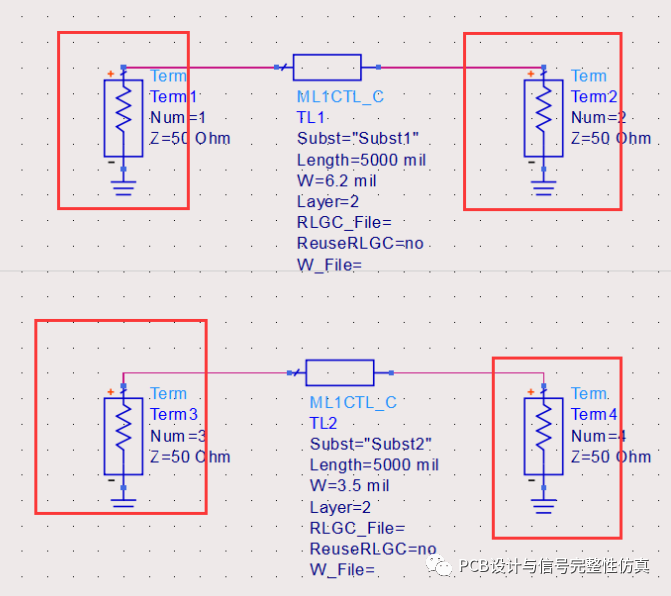

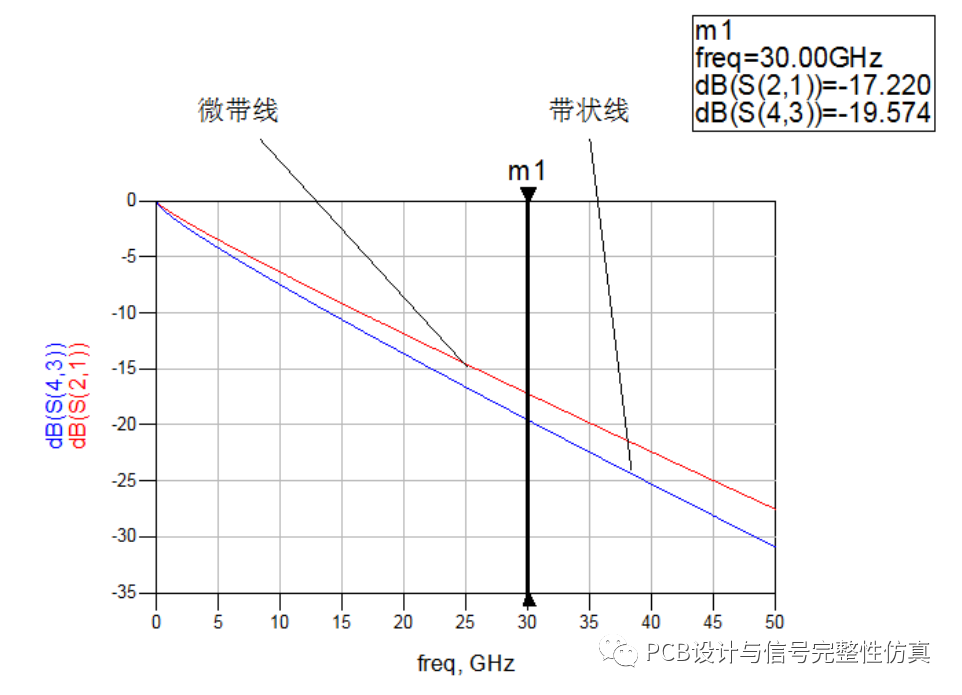

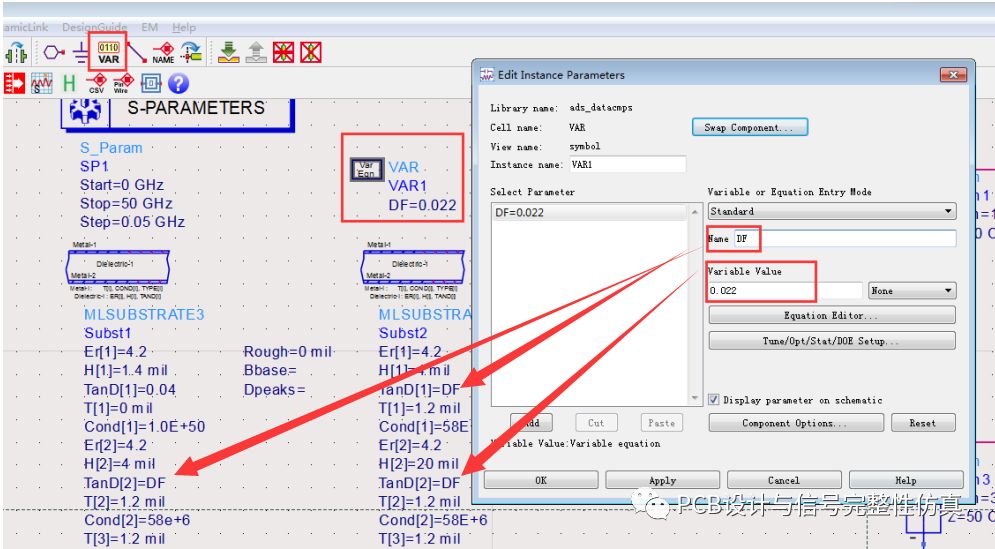

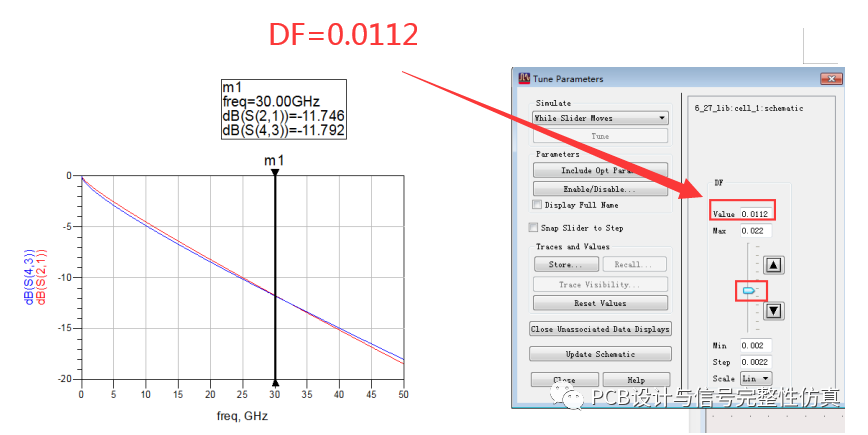

过多损失掉,因此在布线前期就需要规划选择一个合适的走线层。这里我们通过仿真软件来对比表层走线与内层走线,谁更适合用于高速信号的传输。首先搭建叠层模板,分别是表层走线模板和内层走线的层叠模板:为了更接近

2020-03-09 10:57:00

这里说的注意事项是针对于6层pcb设计中,假八层的pcb设计工艺而言。6层pcb的一种层叠结构参考图1,三四层为内层走线,如果要控制内层的阻抗,那么中间的pp层就要做的很厚,但是pp层很厚的话工艺

2019-06-03 08:03:57

高速PCB设计是一个相对复杂的过程,由于高速PCB设计中需要充分考虑信号、阻抗、传输线等众多技术要素,常常成为PCB设计初学者的一大难点,本文提供的几个关于高速PCB设计的基本概念及技术要点

2023-04-19 16:05:28

`内层的地层与电源层可以走线吗理论上地层与电源层相邻的面积越完整越近高频的阻抗越 低,实务上当外层(top and bottom side)的高速走线电磁幅 射太强的时候,为了降低表层幅射强度,在

2014-02-19 18:23:03

大小和走线粗细决定铜箔厚度,如电源板一般使用2-3OZ铜箔,普通信号板一般选择1OZ的铜箔,走线较细的情况还可能会使用1/3QZ铜箔以提高良品率;同时避免在内层使用两面铜箔厚度不一致的芯板。5、PCB板

2017-01-16 11:40:35

高速信号区域相应的电源平面或地平面尽可能保持完整(11)建议布线分布均匀,大面积无布线的区域需要辅铜,但要求不影响阻抗控制(12)建议所有布线需倒角,倒角角度推荐45度(13)建议防止信号线在相邻层

2017-01-23 16:04:35

。(3)遵守紧耦合的原则,当两条差分信号线距离很近时,电流传输方向相反,其磁场相互抵消,电场相互耦合,电磁辐射也要小得多。为减少损耗,高速差分线换层时可以在换层孔的附近添加地过孔。(4)走线尽可能地短而

2017-07-18 10:57:28

板的布线层层数;(3)信号质量控制:对于高速信号比较集中的PCB设计,如果重点关注信号质量,那么就要求减少相邻层布线以降低信号间串扰,这时布线层层数与参考层层数(Ground层或Power层)的比例

2017-03-01 15:29:58

形成边长超过200MIL的自环(14)建议相邻层的布线方向成正交结构说明:相邻层的布线避免走成同一方向,以减少层间串扰,如果不可避免,特别是信号速率较高时,应考虑用地平面隔离各布线层,用地信号隔离各信号线。更多技术干货可关注【快点PCB学院】公众号

2017-01-23 09:36:13

通用的高速信号PCB设计处理原则有:(1)层面的选择:处理高速信号优先选择两边是GND的层面处理(2)处理时要优先考虑高速信号的总长(3)高速信号Via数量的限制:高速信号允许换一次层,换层时加

2017-02-07 09:40:04

问一个比较弱智的问题,如果我使用的是四层板,中间两层分别为地和电源层,并且想要在电源层走线,我在添加层的时候,是不是只能选择add layer而不是add plane?我现在是add plane,怎么能够实现在电源层走线?

2019-07-04 04:36:10

图解在高速的PCB设计中的走线规则

2021-03-17 07:53:30

是FR4层压板,而导体则是信号走线。FR4的平均介电常数在4.2到4.5之间。由于不知道制造误差,有可能导致对铜线的过度蚀刻,最终造成阻抗误差。计算PCB走线阻抗的最精确方法是利用场解析程序(通常是

2018-11-27 10:07:39

在高速PCB设计过程中,由于存在传输线效应,会导致一些一些信号完整性的问题,如何应对呢?

2021-03-02 06:08:38

来源:互联网在高速PCB设计中,差分信号的应用越来越广泛,这主要原因是和普通的单端信号走线相比,差分信号具有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。作为一名(准)PCB设计工程师,我们必须搞定差分信号,接下来我们了解下相关内容吧!

2020-10-23 08:36:50

解决高速PCB设计信号问题的全新方法

2021-04-25 07:56:35

高速数字PCB设计信号完整性解决方法

2021-03-29 08:12:25

作为一名合格的、优秀的PCB设计工程师,我们不仅要掌握高速PCB设计技能,还需要对其他相关知识有所了解,比如高速PCB材料的选择。这是因为,PCB材料的选择错误也会对高速数字电路的信号传输性能造成不良影响。

2021-03-09 06:14:27

。 6. 高速PCB设计中,蛇形线没有所谓滤波或抗干扰的能力,只可能降低信号质量,所以 只作时序匹配之用而无其它目的。 7. 有时可以考虑螺旋走线的方式进行绕线。

2014-12-16 09:47:09

重点分析一下电容和接地过孔在保证信号低阻抗回路中所起的作用,这也是多层PCB板设计中有效抑制EMI的重要方面之一。多层PCB设计中,由于布线密度,拓补结构的要求,信号走线经常需要在层间切换,如果它所

2019-05-20 08:30:00

电源布局、网口电路、音频走线的PCB设计

2021-03-04 06:10:24

网络,在多层的PCB走线的时候一旦产生了开环的结果,将产生线形天线,增加EMI的辐射强度。 图3 开环规则 规则四:高速信号的特性阻抗连续规则 高速信号,在层与层之间切换的时候必须保证特性阻抗

2018-09-20 10:38:01

。规则四:高速信号的特性阻抗连续规则高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射。也就是说,同层的布线的宽度必须连续,不同层的走线阻抗必须连续。规则五:高速PCB设计

2017-11-02 12:11:12

什么是高速pcb设计高速线总体规则是什么?

2019-06-13 02:32:06

和方式要符合所用的探棒。11、在高速 PCB 设计中,信号层的空白区域可以敷铜,而多个信号层的敷铜在接地和接电源上应如何分配?一般在空白区域的敷铜绝大部分情况是接地。 只是在高速信号线旁敷铜时要注意敷

2017-01-20 10:29:29

本文主要分析一下在高速PCB设计中,高速信号与高速PCB设计存在一些理解误区。 误区一:GHz速率以上的信号才算高速信号? 提到高速信号,就需要先明确什么是高速,MHz速率级别的信号算高速、还是

2019-11-05 11:27:17 10310

10310

电子发烧友App

电子发烧友App

评论