前段时间有一个网友向我提出了这样一个疑问:他问我在有些开关电源电路中,为什么会在场效应管的栅极和驱动它的芯片之间加一个二极管。其实这是一个加速放电的二极管,用来为场效应管提供一个快速放电的回路。有些

2023-02-27 10:03:29 612

612

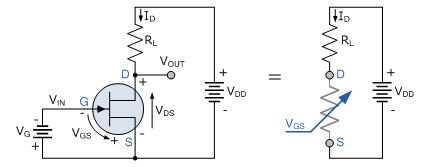

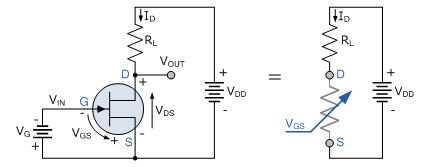

FET电流源是一种有源电路,它使用场效应晶体管为电路提供恒定量的电流。但是,为什么还要恒定电流呢?恒流源和吸电流(吸电流与电流源相反)是一种非常简单的方法,只需使用单个FET和电阻即可形成具有恒定电流值的偏置电路或基准电压源,例如100uA、1mA或20mA。

2023-07-17 15:52:50 2162

2162

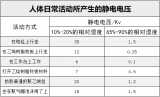

是如何产生的

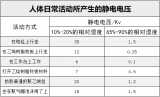

静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时,产生的一种现象,如摩擦起电就是一种静电放电现象。

静电的问题一直困扰着许多电子产品,其放电电流产生的电磁场,通过电容耦合、电感

2023-05-12 12:02:17

本章及随后几章将讨论静电放电引起的系统问题的硬件解决措施。为了便于对系统硬件解决进行讨论,将系统上的静电放电效应划分成以下三个部分:1. 静电放电之前静电场的效应2. 放电产生的电荷注入效应3. 静电放电电流产生的场效应

2019-07-29 07:55:17

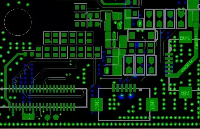

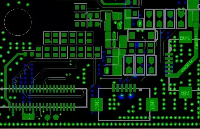

排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100。对于顶层和底层表面都有元器件、具有很短连接线。来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会

2019-05-22 09:49:34

。 在做ESD放电测试时通常采用两种方法:接触放电和空气放电。接触放电就是直接对待测设备进行放电;空气放电也称为间接放电,是强磁场对邻近电流环路耦合产生。这两种测试的测试电压一般为2KV-8KV

2018-09-17 17:43:16

1.静电放电之前静电场的效应 2.放电产生的电荷注入效应 3.静电放电电流产生的场效应 尽管印刷线路板(PWB,通常也称之为PCB)的设计会对上述三种效应都产生影响,但是主要是对第三种效应

2018-09-21 11:52:02

生产程序。 总之,静电无处不在。做好静电防护措施,对于电子产品生产来说,等同于消除一大安全隐患。 那么,PCB设计如何应对静电放电电流产生的场效应?PCB设计技术会对下面三种效应都产生影响: 1.静电

2017-10-25 11:33:31

是如何产生的

静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时,产生的一种现象,如摩擦起电就是一种静电放电现象。

静电的问题一直困扰着许多电子产品,其放电电流产生的电磁场,通过电容耦合、电感

2023-05-12 11:52:56

:

一、静电是如何产生的

静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时,产生的一种现象,如摩擦起电就是一种静电放电现象。

静电的问题一直困扰着许多电子产品,其放电电流产生的电磁场,通过

2023-05-08 18:28:47

PCB电流与线宽有何关系?PCB设计铜铂厚度、线宽和电流有何关系?PCB设计时铜箔厚度,走线宽度和电流有何关系?

2021-09-30 08:28:23

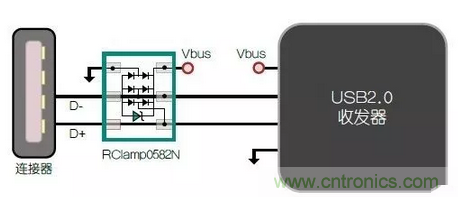

PCB 设计可以减少故障检查及返工所带来的不必要成本。在PCB 设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD 放电产生的直接电荷注入,因此PCB 设计中更重要的是克服放电电流产生

2012-02-03 14:09:10

PCB设计中如何防止静电放电我们的手都曾有过静电放电(ESD)的体验,即使只是从地毯上走过然后触摸某些金属部件也会在瞬间释放积累起来的静电。我们许多人都曾抱怨在实验室中使用导电毯、ESD静电腕带

2013-01-29 10:38:41

紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100.对于顶层和底层表面都有元器件、具有很短连接线。来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成

2016-07-21 11:00:16

超出毫米波技术范围(30GHz),但的确也涉及RF和低端微波技术。 RF工程设计方法必须能够处理在较高频段处通常会产生的较强电磁场效应。这些

2009-03-25 11:49:47

越大,所需要的电荷就越多(即储能越多),充电时间也就越长。当PCB设计之电容充满电后,VC等于E。此时开关K与2端接通,则PCB设计之电容器通过R放电,放电电流为,VC逐渐降低。在接通2端的瞬间,放电

2019-08-13 10:49:30

PCB设计技术会对下面三种效应都产生影响: 1. 静电放电之前静电场的效应 2. 放电产生的电荷注入效应 3. 静电放电电流产生的场效应 但是,主要是对第三种效应产生影响。下面的讨论

2018-08-29 10:28:15

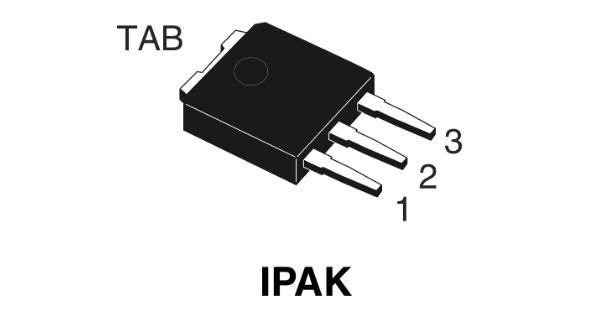

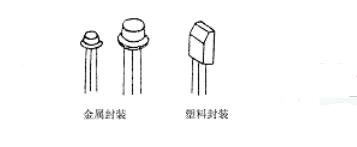

`场效应三极管的型号命名方法<br/> 现行有两种命名方法。第一种命名方法与双极型三极管相同,第三位字母J代表结型场效应管,O代表绝缘栅场效应管。第二位字母代表 材料

2009-04-25 15:42:55

现行有两种命名方法。第一种命名方法与双极型三极管相同,第三位字母J代表结型场效应管,O代表绝缘栅场效应管。第二位字母代表 材料,D是P型硅,反型层是N沟道;C是N型硅P沟道。例如,3DJ6D是结型

2021-05-13 06:13:46

的型号命名方法 现行有两种命名方法。第一种命名方法与双极型三极管相同,第三位字母J代表结型场效应管,O代表绝缘栅场效应管。第二位字母代表 材料,D是P型硅,反型层是N沟道;C是N型硅P沟道。例如

2013-03-27 16:19:17

好东西呀:场效应管检测方法与经验一、用指针式万用表对场效应管进行判别(1)用测电阻法判别结型场效应管的电极根据场效应管的PN结正、反向电阻值不一样的现象,可以判别出结型场效应管的三个电极。具体方法

2012-07-28 14:13:50

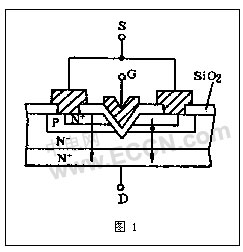

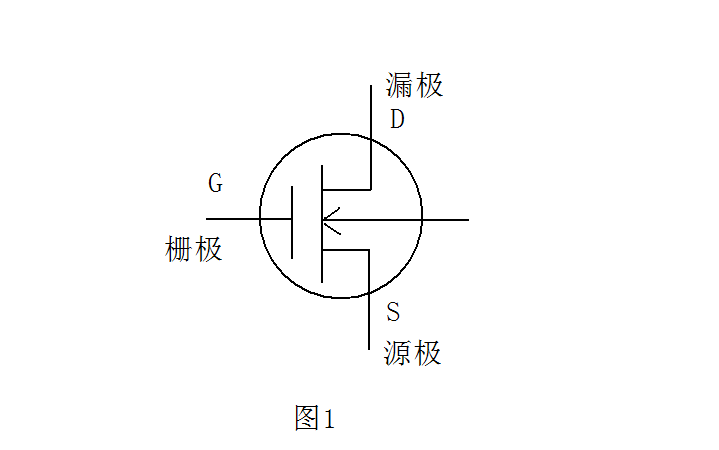

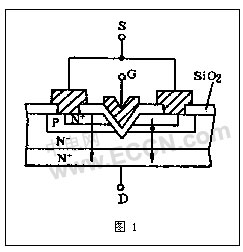

场效应管(FET)是一种具有pn结的正向受控作用的有源器件,它是利用电场效应来控制输出电流的大小,其输入端pn一般工作于反偏状态或绝缘状态,输入电阻很高,栅极处于绝缘状态的场效应管,输入阻抗很大

2019-07-29 06:01:16

场效应管的参数场效应管的参数很多,包括直流参数、交流参数和极限参数,但一般使用时关注以下主要参数:1、I DSS — 饱和漏源电流。是指结型或耗尽型绝缘栅场效应管中,栅极电压U GS=0时的漏源电流

2009-04-25 15:43:12

RDS减小,使表针向右摆动,多数管子的RDS增大,表针向左摆动。无论表针的摆动方向如何,只要能有明显地摆动,就说明管子具有放大能力。本方法也适用于测MOS管。为了保护MOS场效应管,必须用手握住螺钉旋

2009-04-25 15:43:42

电流与PCB设计的线宽有何关系?电流与PCB设计的铜铂厚度有何关系?

2021-10-09 08:16:59

解释一下第二个作用的原理:保护栅极G~源极S:场效应管的G-S极间的电阻值是很大的,这样只要有少量的静电就能使它的G-S极间的等效电容两端产生很高的电压。 如果不及时把这些少量的静电泻放掉,两端的高压

2022-05-14 10:22:39

本帖最后由 eehome 于 2013-1-5 10:00 编辑

静电会对绝缘栅型场效应管(MOS管)造成不良影响,如果栅极悬空会被击穿。因为静电电压很高,一般是几百伏或者几千伏,而管子栅极

2012-07-11 11:38:36

也许是指导PCB布局、系统布局以及接地的最合适人选。深思熟虑的规划以及实施能帮助实现好的结果。考虑在静电放电过程中电流的流向,考虑电流的两个极性来确保安全的电流路径。最好能把放电路径限制到接入点附近

2018-09-21 09:54:40

。 ESD静电放电的危害 ESD损坏IC是由于产生的高压和高峰值电流造成的。精密模拟电路往往具有极低的偏置电流,比普通数字电路更容易遭到损坏,因为用于ESD保护的传统输入保护结构会增加输入泄漏,因此

2021-01-06 17:26:05

它物体接触时,依据电荷中和的机理存在着电荷流动,传送足够的电量以抵消电压。在高速电量的传送过程中,将产生潜在的破坏电压、电流以及电磁场,严重时将其中物体击毁,这就是静电放电。国家标准中定义:静电放电

2011-12-07 16:14:20

寿命。2、静电放电或电流产生的热,使元器件受到潜在损伤。3、静电放电产生的电磁场幅度很大且频谱极宽,对电子器件造成干扰甚至损坏。4、静电放电破坏,使元器件受损坏不能工作。由此可见,ESD静电危害无法估量

2013-12-25 09:38:12

MOS管都能够把它击穿。另外,就算是产生ESD,也不一定会把管子击穿。静电的基本物理特征为:(1)有吸引或排斥的力量;(2)有电场存在,与大地有电位差;(3)会产生放电电流。这三种情形即ESD一般会对

2017-06-01 15:59:30

PCB 设计可以减少故障检查及返工所带来的不必要成本。在PCB 设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD 放电产生的直接电荷注入,因此PCB 设计中更重要的是克服放电电流产生

2015-02-03 14:27:03

MOSFET显示出令人反感的短通道效应。 将栅极长度(Lg)缩小到90 nm以下会产生明显的漏电流,而在28 nm以下,漏电流过大,使晶体管失效。因此,随着栅极长度的缩小,抑制关断状态泄漏至关重要。 提高

2023-02-24 15:25:29

)二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。本文将提供可以优化ESD防护的PCB设计准则。 电路环路 电流

2009-12-02 09:11:51

请问各位大神,在静电放电抗扰度试验中,静电放电发生器的直流高压电源、充电电阻、放电电阻、储能电容器、放电开关、等等的各项具体要求是什么?比如功率,电流,耐压值什么的。希望大家可以帮助我这个小菜鸟,我是刚刚开始学习EMC。谢谢!!!

2013-12-22 15:47:30

1000UF电容充电,并很快充满,栅极获得控制电压,场效应管导通,灯泡点亮,此时如果松手,轻触开关断开,电容里的电流通过500K电阻对地缓慢的放电,由于场效应管输入阻抗相当高,因此基本不会影响电容

2021-05-25 07:10:31

PCB板中静电放电的设计与解决方法

2021-03-18 06:34:49

在高速PCB设计过程中,由于存在传输线效应,会导致一些一些信号完整性的问题,如何应对呢?

2021-03-02 06:08:38

高速数字PCB设计信号完整性解决方法

2021-03-29 08:12:25

它物体接触时,依据电荷中和的机理存在着电荷流动,传送足够的电量以抵消电压。在高速电量的传送过程中,将产生潜在的破坏电压、电流以及电磁场,严重时将其中物体击毁,这就是静电放电。国家标准中定义:静电放电是具有

2018-03-01 12:00:14

。本文介绍了手机静电放电测试的要求和方法,总结分析了手机静电放电抗扰度试验的主要失效现象和模式, 可供手机静电放电抗扰度试验及提高手机抗静电能力设计时参考。

2019-07-25 06:51:33

浪涌电压/电流产生的原因主要由电压突变引起的,浪涌电流是指电网中出现的短时间象“浪”一样的高电压引起的大电流。当某些大容量的电气设备接通或断开时间,由于电网中存在电感,将在电网产生“浪涌电压”,从而引发浪涌电流。 简单形容就像“毛刺”拿示波器看也像“毛刺

2010-05-14 17:12:42

随着半导体制程技术的不断演进,以及集成电路大量的运用在电子产品中,静电放电已经成为影响电子产品良率的主要因素。美国最近公布因为静电放电而造成的国家损失,一年就高达两百多亿美金,而光是电子产品部份

2019-07-25 06:45:53

纯直流场效应管功放电路原理图

2019-11-01 09:10:41

1、结型场效应管分为N沟道和P沟道两种类型。

为使N沟道场效应管能够正常工作,应在其栅源之间加负向电压,以保证耗尽层承受反向电压;在漏源之间加正向电压,以形成漏极电流。N沟道场效应管在不加控制电压

2024-01-30 11:38:27

过电流产生的原因是什么?如何在电流情况下采取措施保护GTO?使其免遭损坏。GTO的过电流特性有哪些?逆变器的过电流保护方法有哪几种?

2021-04-12 07:06:03

运放电路PCB设计技巧

2020-12-29 07:50:05

今天在书上看到一个运放误差的计算方法,有一项是由于失调电流产生误差电压,这个搞不懂怎么来,大神们帮帮忙。解答一下。例题如图1

2013-08-19 16:48:42

。这种高频信号技术虽然远远超出毫米波技术范围(30GHz),但的确也涉及RF和低端微波技术。 RF工程设计方法必须能够处理在较高频段处通常会产生的较强电磁场效应。这些电磁场能在相邻信号线或PCB线上感生

2018-09-13 15:53:21

利用负载电流产生微波的新型MIL为了进一步提高MILO 产生微波的功率和效率,提出了其负载电流能量全部利用来产生微波的新思想。设计并运用二维全电磁PIC 方法模拟了

2009-10-26 21:37:40 18

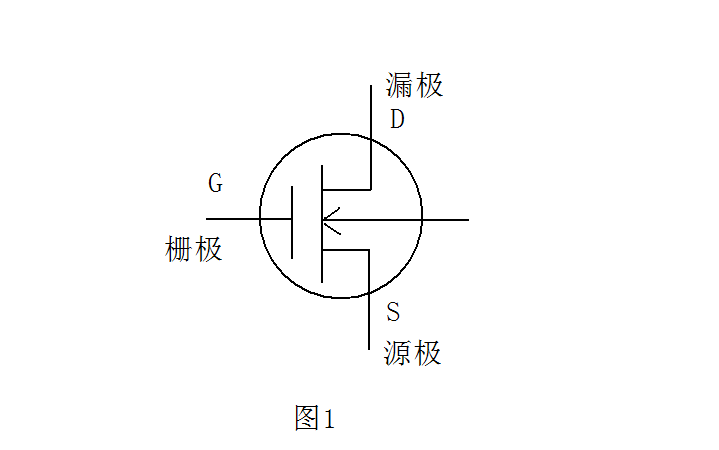

18 场效应管(简称FET)是利用输入电压产生的电场效应来控制输出电流的,所以又称之为电压控制型器件。它工作时只有一种载流子(多数载流子)参与导电,故也叫单极型半导

2009-12-10 15:32:40 87

87 尽管印刷线路板(PWB,通常也称之为PCB)的设计会对下述三种效应都产生影响,但是主要是对第三种效应产生影响。

1. 静电放电之前静电场的效应2. 放电产生的电荷注入

2010-06-12 15:43:49 58

58 场效应管的检测方法

一、用指针式万用表对场效应管进行判别(1)用测电阻法判别结型场效应管的电极根据场效应管的PN结正、反向电阻值不一样

2007-12-22 11:34:38 1094

1094

场效应管检测方法与经验

一、用指针式万用表对场效应管进行判

2009-07-02 18:28:30 427

427

场效应三极管的型号

场效应三极管的型号, 现行有两种命名方法。其一是与双极型三极管相同,第三位字母J代表结型场效应管,O代表绝缘栅场效

2009-11-09 15:57:08 4591

4591 场效应管特性及单端甲类功放电路原理 单端甲类场效应管功放电路五花八门,

2009-11-10 08:59:17 10503

10503 如何避免高速PCB设计中传输线效应

1、抑止电磁干扰的方法

很好地解决信号完整性问题将改善PCB板的电磁兼容性(EMC)。其中非常重要的是保证PCB板有很好的接

2009-11-20 11:17:00 799

799 场效应管的型号命名方法

现行场效应管有两种命名方法。第一种命名方法与双极型三极管相同,第三位字母J代表结型场效应

2009-11-26 08:40:22 7746

7746 场效应管和CMOS集成电路的焊接方法

焊接绝缘栅(或双栅)场效应管以及CMOS集成块时,因其输入阻抗很高、极间电容小,少量的静电荷即会感应静电

2010-01-16 10:37:45 919

919 PCB设计时怎样抗静电放电

静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极

2010-03-13 14:55:50 1661

1661 内容提要 一、何谓ESD 二、静电的产生机理 三、静电的危害 四、静电放电模型 五、电子工作区的静电防护 六、静电消除方法 七、静电接地的目的 八、静电防护设备要求 九、人员训练

2011-03-23 13:39:52 1412

1412 ESD 是代表英文ElectroStatic Discharge 即静电放电的意思。ESD 是本世纪中期以来形成的以研究静电的产生与衰减、静电放电模型、静电放电效应如电流热(火花)效应(如静电引起的着火与

2011-11-25 14:05:43 125

125 在EMI中和传导相关的共模及差模电流产生的原理,静点动点的概念,并详细的说明了在变压器的结构中使用补偿设计的方法

2017-10-30 17:22:34 18

18 PCB设计技术会对下面三种效应都产生影响: 1.静电放电之前静电场的效应 2.放电产生的电荷注入效应 3.静电放电电流产生的场效应 但是,主要是对第三种效应产生影响。下面的讨论将针对第三条所述

2017-12-01 10:37:20 0

0 PCB 设计可以减少故障检查及返工所带来的不必要成本。在PCB 设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD 放电产生的直接电荷注入,因此PCB 设计中更重要的是克服放电电流产生

2017-12-05 13:40:30 0

0 本文开始介绍了场效应管的概念和场效应管特点,其次介绍了场效应管的参数与场效应管的作用,最后分析了场效应管在电路中如何控制电流大小以及介绍了场效应管测量方法图解。

2018-04-03 11:37:59 43955

43955

本文档的主要内容详细介绍的是静电放电ESD的介绍和原理及解决方法概述主要内容包括了:一、何谓ESD 二、静电的产生机理 三、静电的危害 四、静电放电模型 五、电子工作区的静电防护 六、静电消除方法 七、静电接地的目的 八、静电防护设备要求 九、人员训练

2019-01-07 08:00:00 76

76 PCB设计技术会对下面三种效应都产生影响:

1. 静电放电之前静电场的效应。

2. 放电产生的电荷注入效应。

3. 静电放电电流产生的场效应。

2019-08-01 15:36:51 1007

1007

PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查及返工所带来的不必要成本。在PCB设计中,由于采用了瞬态电压抑止器(TVS)二极管来抑止因ESD放电产生的直接电荷注入,因此PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。

2019-04-16 15:32:04 1249

1249 本文介绍了场效应管的测试方法和产品特性。

2019-08-14 15:08:07 7989

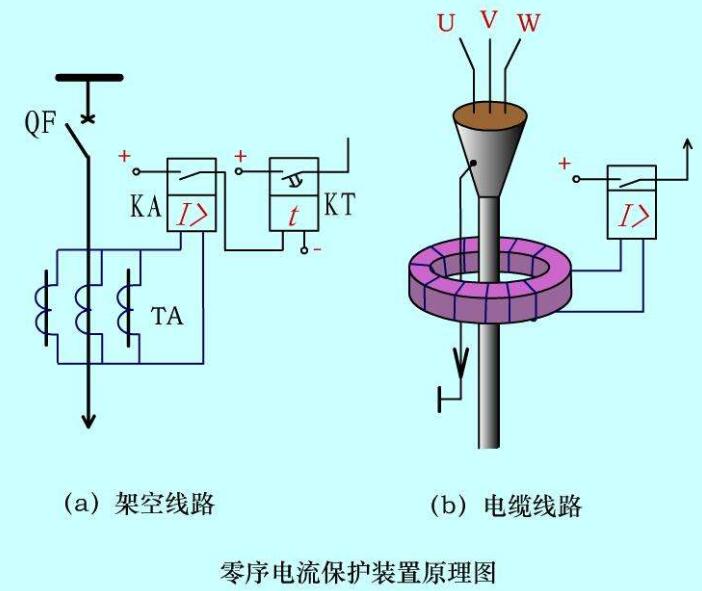

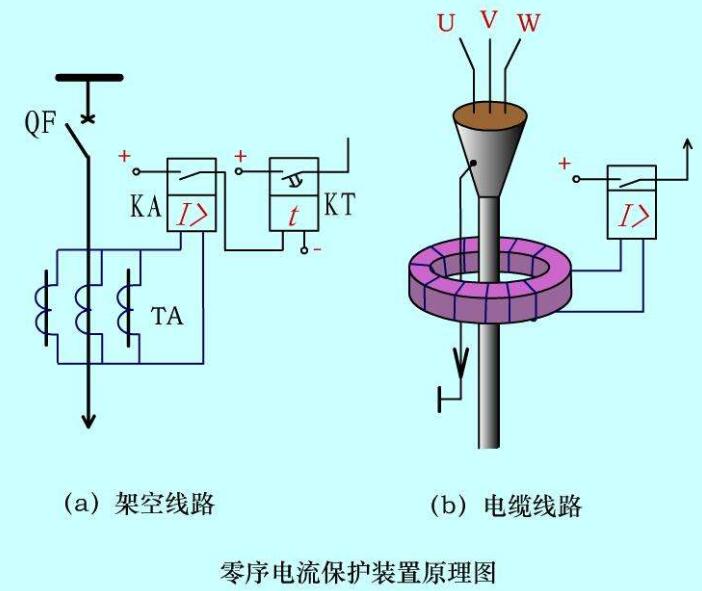

7989 本文主要介绍了零序电流产生的原因及零序电流的危害。

2019-10-21 10:19:14 53887

53887

微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的IC。单次静电放电事件就可以将PCB摧毁。

2019-12-13 16:36:32 4102

4102

PCB设计技术会对下面三种效应都产生影响:

1.静电放电之前静电场的效应

2.放电产生的电荷注入效应

3.静电放电电流产生的场效应

2019-12-31 15:48:50 951

951 1.静电放电之前静电场的效应 2.放电产生的电荷注入效应 3.静电放电电流产生的场效应 尽管印刷线路板(PWB,通常也称之为PCB)的设计会对上述三种效应都产生影响,但是主要是对第三种效应产生

2020-02-24 11:33:39 1946

1946 3. 静电放电电流产生的场效应尽管印刷线路板(PWB,通常也称之为PCB)的设计会对上述三种效应都产生影响,但是主要是对第三种效应产生影响。下面的讨论将针对第三条所述的问题给出设计指南。通常,源与接收电路之间的场耦合可以通过下列方

2020-10-14 10:43:00 2

2 控制基极电流来控制集电极电流的一种电流控制型器件,输入阻抗较低。而场效应管是利用输入电压产生的电场效应来控制输出电流的一种电压控制型器件,图几种场效应,它具有输入阻抗高、热稳定性好、便于集成化等优点而得到广泛管的外形应用。

2020-08-25 17:25:47 4714

4714

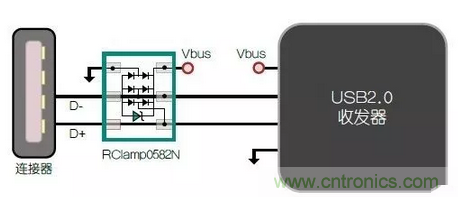

来源:罗姆半导体社区 微电子电路面临的风险比以往任何时候都大,罪魁祸首是静电放电(ESD)。静电放电是隐秘的杀手,特别容易攻击敏感的 IC。单次静电放电事件就可以将 PCB 摧毁。抗静电放电

2022-11-15 16:23:37 964

964 PCB设计中更重要的是克服放电电流产生的电磁干扰(EMI)电磁场效应。本文将提供可以优化ESD防护的PCB设计准则。

2020-12-07 10:17:40 2155

2155 电子发烧友网为你提供PCB板中静电放电的设计与解决方法资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-04 08:52:11 36

36 场效应管的简单测试方法汇总

2021-10-25 09:53:02 6

6 场效应管工作原理及场效应三极管的型号命名方法

2022-01-19 10:04:32 14

14 场效应管是一种电子元件,它可以控制电流或电压,通过改变极化层的电场来控制电流或电压。根据其结构特点分为MOSFET(金属氧化物半导体场效应管)、JFET(金属硅场效应管)、IGBT(晶体管场效应管)等。

2023-02-17 15:44:05 3572

3572 在干燥的环境下,人体静电(ESD)的电压很容易超过6~35Kv,当用手触摸电子设备、PCB或PCB上的元器件时,会因为瞬间的静电放电,而使元器件或设备受到干扰,甚至损坏设备或PCB上的元器件。

2023-07-04 09:07:44 1003

1003

静电放电的产生有两个基本条件,一. 是电荷的积累,电荷的积累是前提,然后是“跨接”,电荷的剧烈流动就是放电。所以从这两个方面就行控制就能有效地防护静电放电的产生。

2023-09-05 11:08:19 479

479

一站式PCBA智造厂家今天为大家讲讲PCB设计阻抗不连续怎么办?PCB设计阻抗不连续问题的解决方法。大家都知道PCB设计阻抗要连续。但是PCB设计也总有阻抗不能连续的时候。怎么办?下面深圳PCBA

2023-09-22 09:32:05 634

634

PCB布线是ESD防护的一个关键要素,合理的PCB设计可以减少故障检查和返工所带来不必要的成本。在PCB设计中,不但需要在静电薄弱电路增加静电抑制器件,还要克服放电电流产生的电磁干扰(EMI)电磁场效应。

2023-09-26 10:57:16 650

650

对于PCB设计过程中基板可能产生的问题,深圳捷多邦科技有限公司王总认为,主要存在的问题有,各种锡焊问题现象征兆,比如:冷焊点或锡焊点有爆破孔。

2023-11-15 15:25:11 147

147 静电放电对电路的影响主要是通过电压、电流和能量传递的方式产生的。静电放电是由于电荷积累在物体表面,当电荷之间或物体与接地之间存在电势差时,会发生电荷的突然释放,形成放电现象。

2023-11-21 16:28:41 612

612 之一,它对FET的工作状态和性能有着直接影响。本文将详细介绍场效应晶体管栅极电流的概念、计算方法以及其在不同工作状况下的特点和影响。 一、场效应晶体管栅极电流的概念 场效应晶体管的结构由源极、漏极和栅极组成。当FET处于工作状态时,栅极电流即为通过栅极电极

2023-12-08 10:27:08 655

655 解决方法。 首先,我们来看看励磁涌流产生的原因。励磁涌流的主要原因有以下几点: 变压器的饱和特性:变压器的铁芯具有饱和特性,当磁通密度超过一定值时,铁芯的磁导率会降低。在励磁电流从零开始上升时,磁通密度逐渐增加,

2023-12-19 10:40:09 1090

1090 电机轴电流产生的原因及对策 电机是现代工业和生活中的重要设备之一,广泛应用于机械传动系统中。在电机运行过程中,会产生一定的轴电流。轴电流是指由于电机中的磁场不均匀引起的磁动势差,导致电机的内外

2023-12-25 11:47:11 770

770 如何控制元器件静电放电损伤的产生 静电放电是电荷在两个物体之间突然跳跃的过程,其释放的能量可以损伤元器件。为了控制元器件静电放电损伤的产生,我们可以采取以下几种措施: 1. 选择防静电材料:静电放电

2024-01-03 11:43:27 226

226 PCB压合问题解决方法

2024-01-05 10:32:26 246

246 能会对电路性能产生负面影响。本文将详细介绍 PCB 产生串扰的原因,并提供一些解决方法。 一、串扰的原因 1. 电磁干扰(EMI) 电子设备在工作过程中会产生电磁辐射,信号线上的电流和电压变化会产生磁场,导致附近线路上的电荷和电流发生变化,从而产生

2024-01-18 11:21:55 434

434 一站式PCBA智造厂家今天为大家讲讲如何解决pcb设计阻抗不连续的问题?解决PCB设计中的阻抗不连续的方法。当涉及到PCB(Printed Circuit Board)设计时,阻抗一直是一个非常重要

2024-03-21 09:32:59 86

86

电子发烧友App

电子发烧友App

评论