如上图所示,-48V供电单板,控制风扇转动,EMI滤波电路中2个22nf共模滤波电容和100nf差摸滤波电容故障烧毁,现在基本上可以排除是器件来料和机械应力导致,看单板上面有小虫子爬过的痕迹,有没有可能是小虫子导致短路引起的,各位大神有遇到过这样的情况吗?求解答

2016-07-19 23:25:57

单板部分电路要求有上拉,但供电只有-48V电源,怎么实现?加一个3.3V电源?

2015-08-11 23:23:34

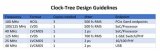

从今天开始我们分5期讲述一下电子产品系统中一个非常重要的部位 - 时钟。多数工程师意识不到它的重要性,觉得只要板子上的晶体/晶振能工作就可以了,其实不然,在今天数字逻辑、数字计算统治的世界里,几乎

2019-07-21 21:43:14

复位是什么意思?时钟可分为哪几种?时钟有什么作用?晶体振荡器有哪些功能及用途?晶体振荡器的特性是什么?

2021-07-01 07:38:04

晶体管电路设计(上),需要完整版的朋友可以下载附加保存哦~

2021-09-29 10:17:07

F28377D的外部时钟,在手册中是下面这样的controlsuite中原理图是下面这样的这图中是晶体,但好像不是手册中的电路,请问是怎么回事

2018-11-26 11:30:06

Fsys系统时钟 Fosc晶体时钟 请问Fsub是什么意思?

2015-07-22 16:48:03

焊盘属性是铺地属性是用的软件是AD09,谢谢~

2019-05-15 04:16:26

PCB中包地与铺地(铺铜)有什么区别?需要包地的地方直接用GND铺铜可以吗?

2023-04-11 17:29:22

在多层PCB设计中,在中间层有很多的地层,这样做的好处是什么?

2016-05-06 11:24:33

本帖最后由 gk320830 于 2015-3-7 13:54 编辑

PCB板上没有丝印的好处 自从开始从事电子设计以来,制作各种各样功能的PCB就一直贯穿始终。每次正面都印上了丝印,如果背面

2013-10-11 10:57:10

右下这3个选项帮解释下,我能看懂英文,但是没怎么理解,现在想铺地把之前连的地线全部融合,包含了,选哪个应该?

2019-04-22 06:36:58

我正在尝试一个PIC12F1571UP并运行一个晶体。不是一个谐振器,只是一个晶体。数据表第5.1节说“时钟源可以从外部振荡器、石英晶体谐振器、陶瓷谐振器提供……”,但是没有具体说明你可以从晶体上

2019-09-10 12:58:30

时钟,RC振荡器4.LSE是低速外部时钟,接频率为32.768kHz的石英晶体5.PLL为锁相环倍频输出,其时钟输入源可选择为HSI或者HSE在STM32上如果不使用外部晶振,OSC_IN和OSC_OUT的接法:如果使用内部RC振荡器而不使用外部晶振,请按照下面方法处理:1.100脚或1..

2022-01-26 06:39:54

我正在基于 STM32H7B3I-EVAL 评估板使用 STM32H7B3LIH6Q 设计定制板。从提供的示意图中可以看出,评估板上使用的晶体为 24 MHz。 现在,我正在构建自己的电路板并注意到

2023-02-01 08:20:55

下面是一个STM32芯片的时钟树图1、LSI是低速内部时钟,RC振荡器,频率为32kHz左右。供独立看门狗和自动唤醒单元使用。 2、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。这个

2021-08-12 07:45:54

按照说明去写的tf卡1. sudo ./mksdcard.sh2.拷贝文件3.拨码开关123 on单板上电串口一点打印也没有

2021-12-31 06:11:15

如题:pcb没有网表能铺铜铺地吗?

2011-05-02 11:15:52

多孔接地)。时钟晶体下面铺地的好处: 晶体振荡器内部的电路会产生射频电流,如果晶体是金属外壳封装的,直流电源脚是直流电压参考和晶体内部射频电流回路参考的依靠,通过地平面释放外壳被射频辐射产生的瞬态电流

2015-12-20 19:27:25

是:

【野火鲁班猫2单板电脑=物联网+综合小项目】 野火鲁班猫2单板电脑=物联网+综合小项目_哔哩哔哩_bilibili

欢迎小伙伴去站观看我的视频,多多分享,给我投票点赞。

下面是项目演示中的一些照片:

2023-05-18 20:06:03

请教给位大神,晶振下方到底是挖空好还是铺地好& p& V2 I/ Q- M# O比如说我两层板,顶层是贴片晶振,那么底层是挖空还是铺地好,网上看了两种说法都有,这让我很纠结

2018-12-26 11:55:00

突然发现外国工程师信号层(大多数顶层)好像都不铺地,底层和中间层大面积普通,这有什么原因吗?

2019-07-29 03:21:25

某工控设备开发厂商的设备中采用单片机控制电路,单片机使用外接的两脚晶体振荡器产生11.0592MHz的工作时钟。用户希望能够精确测量工作时钟的频率,但用示波器测量时一方面测不准,另一方面测量时还会出现晶体停振的情况,对于这种晶体的频率测量有没有好的办法呢?

2019-08-09 06:57:06

接地技术的引入最初是为了防止电力或电子等设备遭雷击而采取的保护性措施,但是随着电子通信和其它数字领域的发展,在接地系统中只考虑防雷和安全已远远不能满足要求了。想请教一下 为什么要将模拟地和数字地分开?单板上的信号如何接地?

2021-04-06 09:58:17

1、时钟线等长概念 在一块主板上,从北桥芯片到CPU、内存、AGP插槽的距离应该相等,主板设计的基本要求,即所谓的“时钟线等长”概念。作为CPU与内存连接桥梁的北桥芯片,在布局上是很有讲究的。例如

2018-08-30 10:14:47

什么叫PCB单板 ?是单层板的意思吗?PCB联板又是什么意思?

2023-04-23 16:15:11

使用stc89c52单板机下载程序,板子上是u***,如何查看u***是

2012-03-04 17:17:01

非常精确的时候可以省掉外部晶体和两个电容,好处是可以简化布线,节省成本并进一步降低功耗;缺点也很明显,HSI不够精准,官方给出的误差是在1%(25摄氏度)。根据手册,USB时钟不能用HSI经PLL后得...

2021-08-12 08:18:25

各位大神: 我想请教下,如果双面板布板要抗干扰好的话(比如过群脉冲),是不是应该尽量把线路都画在同一层,然后另外一层铺一整块比较完整的地,这样是不是抗干扰会大大提升呢?如果是的话,我想问铺地的那层

2019-10-24 22:38:45

描述Commodore 64 诊断加密狗(5 合 1)这个项目是一个单板解决方案,它取代了运行 Commodore 64 诊断盒 586220 所需的 5 个部件。为不同的端口安装了不同的组件。所有

2022-07-07 07:29:11

`可靠性案例分享——单板低温启动不成功问题问题描述:A单板在调试过程中发现概率性启动不成功,电流显示在0.31A左右,测试发现晶体不起振,定位为晶体不起振问题 `

2016-09-03 16:15:14

1、外部晶体/陶瓷谐振器(HSE晶体)模式 这种模式用得比较常见,HSE晶体可以为系统提供较为精确的时钟源。在时钟控制寄存器RCC_CR中的HSERDY位用来指示高速外部振荡器是否稳定。在启动时

2021-08-10 08:18:52

`32.768KHZ是一个很有意义的数字,我们每天都要用到它,它给我们带来太多的好处.只是生活中太少有人去关注了,只关注着它给我们带来的演变数字.32.768khz比较容易分频以便于产生1秒的时钟

2016-05-28 11:18:32

如何识别STM32五个时钟源及其不接外部晶体时的管脚配置?A:1.HSI是高速内部时钟,RC振荡器,频率为8MHz。2. HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为

2021-08-10 06:34:21

小弟正联系使用AD09画PCB。进入铺地阶段。开发板的铺地是怎么实现的呢?开发板的铺地和元件的管脚之间的间距很大,但是我的铺地和管脚之间的距离很小,请问,如何设置?开发板的铺地:我自己的铺地:感激不尽呀!!

2019-01-18 06:36:26

,无论纯石英晶体或13M组件电路,均需要电源正常工作输出供电,13M电路才能产生13M输出。 2、 实时时钟频率的产生 手机中的实时时钟频率基本上都是32.768KHz,是由32.768KHz晶体配合其他

2016-11-01 17:43:34

我铺地的时候它老是短路焊盘!可是人家为什么都可以不短路呢?

2016-02-12 18:16:26

LTC2949,请协助确认是否可以使用LTC29498MHz 晶体作为外部时钟输入的外部时钟吗 ? 非常感谢

2024-01-04 08:00:14

大家好,我想知道是否可以使用当前为主 MCU (STM32F334) 提供时钟的单个现有晶体振荡器为另一个 STM32 MCU (STMF031) 提供时钟。它真的可以为我节省空间、功耗、成本和电路板上的另一个时钟源。如果是,如何?

2023-01-12 07:25:54

`管脚连接了地线,copper pour铺地就无法连接了?COPPER POUR区域也定义为GND网络了。打样回来的板子也没有问题,不知道为什么点击地线网络,铺地没有链接到一起?`

2011-06-22 11:20:36

我设计的板子,继电器下面铺了地的,使用起来没什么问题。但我看别人设计的,在继电器下面是不铺地的,不知道我的设计会有什么问题

2013-12-11 15:24:32

Hi(图片请参考附件) 本人在使用HMC 6300/6301中发现6350评估板上时钟的对接和耦合方式非常奇怪,违反通识。 6350单板上通往6300/6350连接器的最后一级时钟如下图: 从

2018-07-30 10:24:27

时钟多米诺逻辑是晶体管级的结构,请问其结构如何,有何作用?如何理解比较好。

2019-07-25 05:56:04

画PCB铺地时候,什么时候铺实地什么时候网格地,有什么区别?求教!!!!!!!!!!!!

2019-02-13 06:36:32

先铺地在接地线是这样的。先接地线,再铺地,是这样的。怎么样才能让它先接地线,再铺地也与前一张一样呢?谢谢,

2019-01-30 06:36:39

外部晶体时钟或内部RC振荡器时钟在“时钟源选项”的配置位

2020-12-09 07:51:15

-- 今天无数电子线路和应用需要精确定时或时钟基准信号。晶体时钟振荡器极为适 合这方面的许多应用。时钟振荡器有多种封装,它的特点是电气性能规范多种多样。它有好几

2009-12-02 15:35:46 0

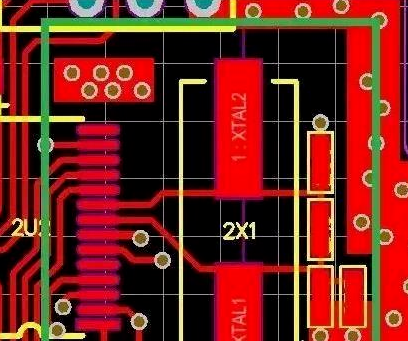

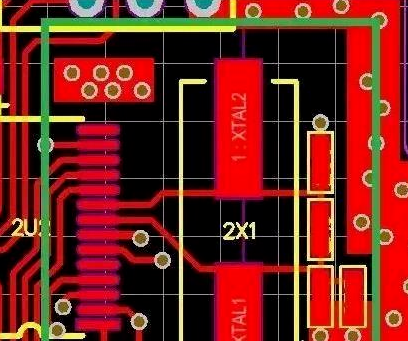

0 PCB单板及拼板设计 一.单板设计 图1 单板PCB设计 1. 适用条件: 采用手工焊接或单板尺寸较大的PCB,可采用单板方式设计; 2. 设置基准点(坐标0,0): 推荐将板边左下角设为基准点,

2012-06-28 12:54:50 0

0 2、单板高温老化0218

2017-01-08 16:28:07 0

0 除了少数罕见的特例以外,几乎所有的电子系统都至少拥有一个时钟功能,这已经不是新闻。在大多数情况下,该时钟功能是通过采用石英晶体加上相关振荡器或时钟发生器集成电路实现,这种基本的实现方式可提供一个单一

2017-10-15 10:51:47 0

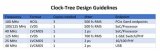

0 分下一层最好不要走线 在PCB时钟电路区域只布与时钟电路有关的器件,避免布设其他电路,晶体附近或者下面不要布其他信号线:在时钟发生电路、晶体下使用地平面,若其他信号穿过该平面,违反了映像平面功能,如果让信号穿越这个地平面的

2018-02-20 20:26:00 3462

3462

我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的PCB文件如下图1所示。

2018-04-09 15:54:00 4789

4789

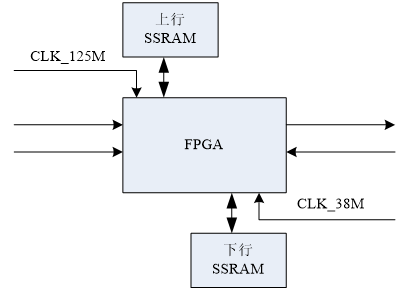

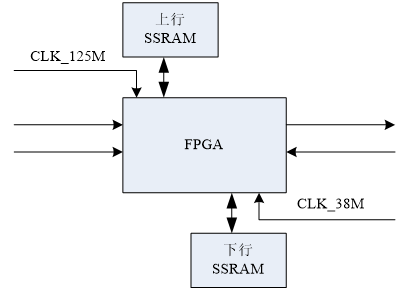

我们系统中,主板与从板之间通过交换网片的HW0、HW4互连,要使主板与从板的交换网之间能够正常交换,必须使这两个交换网片有一致的帧同步时钟及位同步时钟。在现在的单板中,从板的时钟由主板直接送出。整个系统采用的时钟源有3种方式:

2018-10-30 11:36:23 7

7 了解新的UltraScale ASIC时钟架构:如何使用它,它带来的好处以及从现有设计迁移的容易程度。

另请参阅如何使用时钟向导配置时钟网络。

2018-11-29 06:40:00 3390

3390 首先将线宽不同的两块板(表层铺地前)由ALLEGRO导入SIWAVE,在目标线上加入50Ω端口。针对不同线宽0.1016mm和0.35mm, 我们的仿真结果如图2所示,图中显示的曲线是S21,仿真频率范围为800MHz-1GHz。

2019-09-17 14:42:42 4244

4244 虽然很多人都考虑过pcba外包,却并不真正清楚pcba外包的好处。下面说一说选择pcba外包的理由和好处。

2020-07-06 09:44:51 3038

3038 举个例子来说吧。我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的PCB文件如下图1所示(两种线宽):

2020-11-03 10:40:00 5

5 Kyle Beckmeyer特别于近期撰写一篇技术文章,说明关于新型智能汽车的时钟设计关键需求与理想的时钟发生器解决方案。 您将了解到 汽车电子中所需的精密参考时钟数量正在增加系统设计的复杂性并改变最佳实践方法。 将时钟需求从石英换成硅芯片的好处

2021-05-03 18:31:00 1315

1315

华为单板热设计培训资源下载

2021-06-03 10:09:15 50

50 如何从PCB布局上来考虑EMC问题;4.如何正确使用磁珠、电容、共模电感等EMC元器件,在单板原理图阶段全面考虑电磁兼容的问题;6.如何从PCB中考虑多种地的隔离、分割.7.如何从PCB设计的过程中控制EMC问题,如时钟走线、电源走线以及接口走线控制。

2021-11-23 10:55:59 5531

5531 本文结合某单板(下文中统一称M单板)FPGA调试过程中发现地弹噪声造成某重要时钟信号劣化从而导致单板业务丢包的故障,来谈下如何最大程度地降低地弹噪声对单板信号完整性影响。

2022-07-27 09:12:17 531

531 时钟晶体电路一般有两种:无源晶体电路和有源震荡器电路。时钟晶体电路一般是辐射发射的干扰源。

2022-10-10 15:51:12 1693

1693 压接技术在连接器行业非常流行,那么什么是压接技术呢?压接技术能为连接器提供哪些好处?下面,康瑞连接器厂商将为大家分享压接技术为连接器提供的三大好处!

2022-11-18 16:52:48 1763

1763 CCE4510单板

2023-01-11 18:41:27 0

0 本应用笔记介绍了将32,768Hz晶体连接到实时时钟(RTC)的晶体选择和布局技术。它还提供有关振荡器电路设计标准、系统设计和制造问题的信息。

2023-02-07 14:40:39 302

302

时钟晶体和相关电路应布置在PCB的中央位置并且要有良好的地层,而不是靠近I/O接口处。不可将时钟产生电路做成子卡或者子板的形式,必须做在单独的时钟板上或者承载板上。

2023-02-08 09:12:00 413

413 时钟晶体和相关电路应布置在PCB的中央位置并且要有良好的地层,而不是靠近I/O接口处。

2023-02-22 09:22:50 306

306 单板上时钟的注意事项,主要有以下几个方面可以考虑。

2023-05-09 10:09:15 593

593

本文结合某单板(下文中统一称M单板)FPGA调试过程中发现地弹噪声造成某重要时钟信号劣化从而导致单板业务丢包的故障,来谈下如何最大程度地降低地弹噪声对单板信号完整性影响。

2023-06-26 10:17:37 381

381

晶体振荡器内部的电路会产生射频电流,如果晶体是金属外壳封装的,直流电源脚是直流电压参考和晶体内部射频电流回路参考的依靠,通过地平面释放外壳被射频辐射产生的瞬态电流。

2023-06-30 14:16:31 323

323

CCE4510单板

2023-06-30 20:17:51 2

2 介绍:

Pericom为选定的独立实时时钟(RTC)产品提供集成晶体封装选项。新的封装将串行接口(I²C RTC器件)与兼容的32.768 kHz石英晶体集成到单个8引脚中DFN4×4 或 16 引脚 SOIC 封装。

我们在下面列出了一些关于新的集成晶体封装选项的常见问题。

2023-07-24 16:14:45 0

0 单片机时钟电路主要由晶体振荡器和相应的外围电路组成。晶体振荡器通常使用晶体作为振荡元件,当施加合适的电压和电流时,晶体会以特定的频率振荡。晶体振荡器将晶体振荡的信号转换为一个稳定的时钟信号,供单片机系统使用。

2023-08-07 16:49:46 4120

4120 定义:指导PCBA单板工艺应变测试,以及在单板加工过程中的应变管控重点。

2023-08-10 09:44:36 1297

1297

定义:指导PCBA单板工艺应变测试,以及在单板加工过程中的应变管控重点。

2023-08-28 14:33:15 544

544

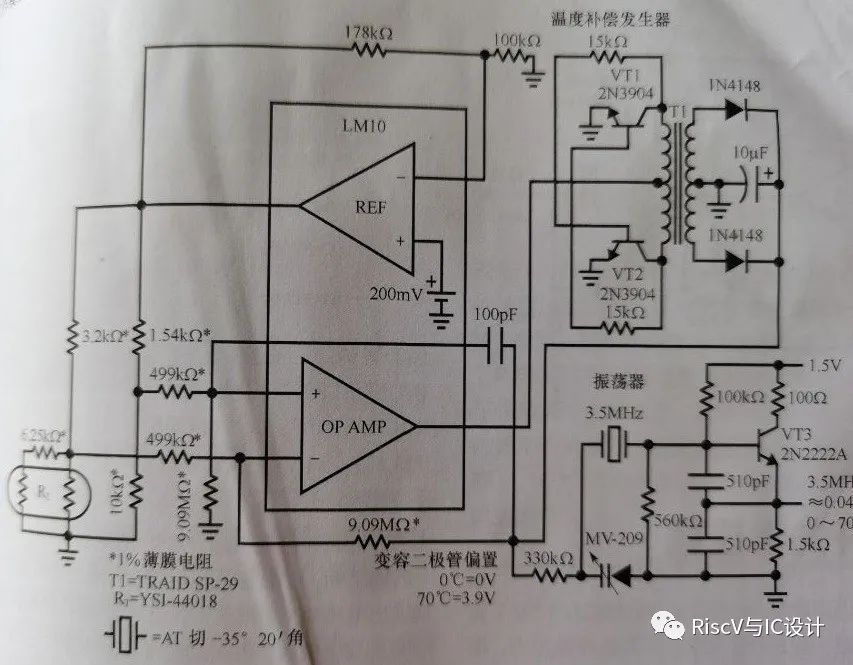

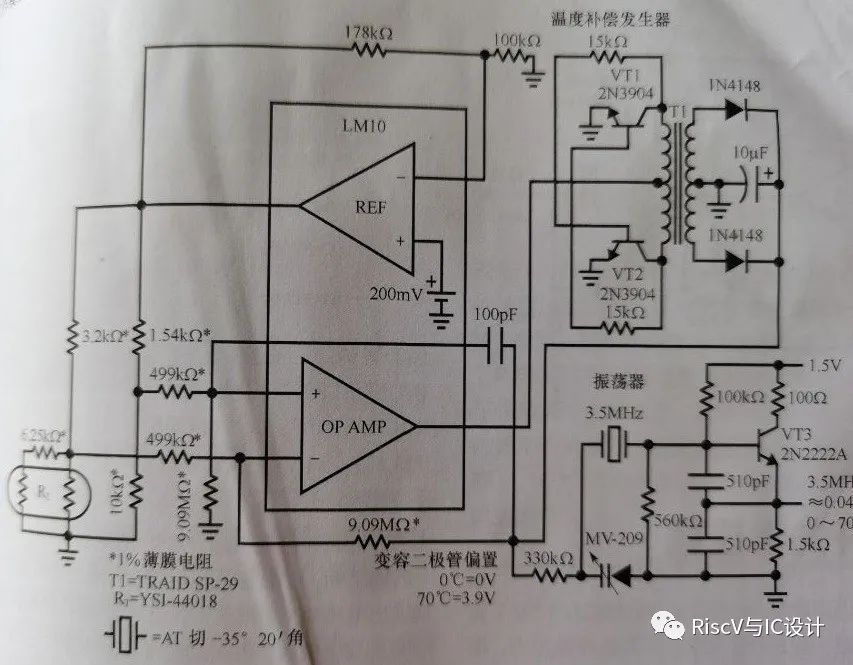

电子系统都需要一个稳定的时钟源,一般都采用晶体振荡器,设计一个低压1.5V的振荡器相对容易,如果振荡器需要良好的温度稳定性,由于晶体的温漂特性,设计就变得复杂了。

2023-10-13 14:42:02 315

315

时钟晶体下面铺地和走线

2023-11-24 15:37:09 429

429

晶振频率和时钟频率本质上有何区别呢?时钟频率有什么作用? 晶振频率和时钟频率是两个相关但又有所不同的概念。下面我们将逐一介绍这两个概念的含义、区别和作用。 首先,我们来了解晶振频率。晶振是一种

2024-01-24 16:11:35 307

307 石英晶体振荡器是如何产生时钟信号的呢? 石英晶体振荡器是一种电子振荡器,它使用石英晶体作为谐振元件来产生稳定的时钟信号。在现代电子设备中,石英晶体振荡器被广泛应用于各种计算机、通信设备、电子表

2024-01-29 13:58:19 191

191 单板上时钟的注意事项 单板上时钟晶体下面铺地的好处 单板上时钟是指将时钟晶体组件直接铺装在电路板上,这种设计方案在电子设备中广泛应用。在介绍单板上时钟的注意事项之前,让我们先了解一下为什么要在单板

2024-02-06 16:06:50 161

161

电子发烧友App

电子发烧友App

评论