日前,德州仪器(TI)宣布推出全新系列的时钟发生器,此次推出的产品可提供100飞秒(fs)的超低抖动以及灵活独特的引脚控制选项。与传统的参考时钟解决方案相比,此次推出的新型时钟发生器所具备的抖动性能可让系统设计人员优化系统定时容限和误码率(BER),以减少数据传输错误。

2015-10-12 13:54:03 1258

1258 概述:MAX3625B是MAXIM公司生产的一款提供三路输出的低抖动,高精度时钟发生器。该MAX3625B是为网络应用而优化的低抖动,高精度时钟发生器。该器件集成一个晶体振荡器和锁相环(PLL)时钟

2021-05-18 07:39:05

其它时钟分配方法,其可降低整体抖动性能。您可使用如 LMK03806 等一款器件来克服这个问题,其在同一器件中整合了所有主时钟发生器和时钟分配功能(带驱动器),如图 1 所示。该器件可在 300MHz

2018-09-13 14:18:06

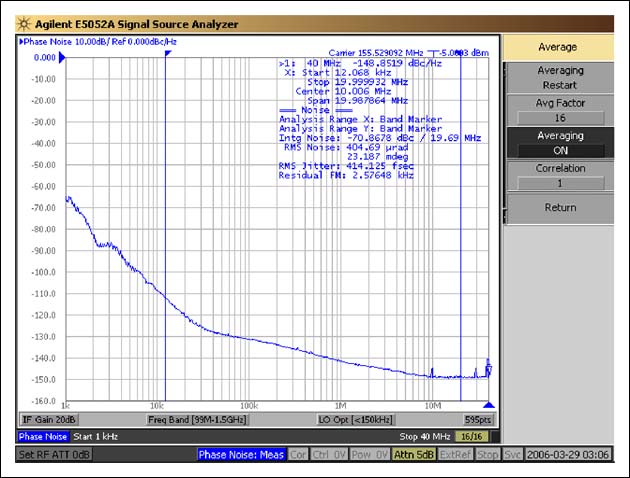

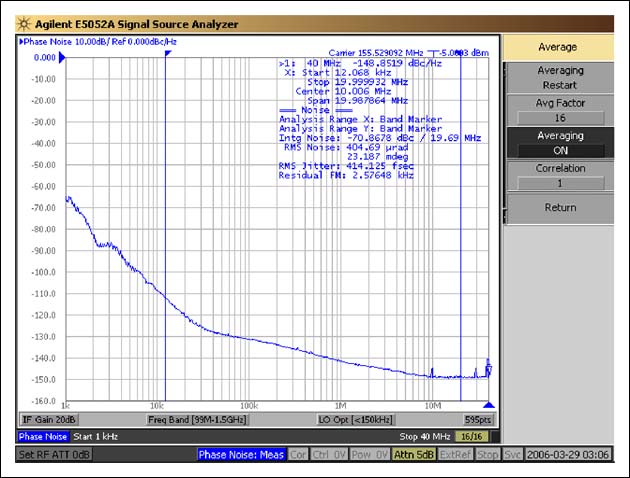

的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。本文将详细讨论

2018-10-18 11:29:03

概述:AD9577是一款既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现最高的网

2021-04-06 06:49:57

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2019-07-30 07:57:42

SNR 性能的影响以及怎样降低一个噪声时钟源的抖动。作为基线,DC1826A-A 的时钟输入采用一个罗德与施瓦茨 SMB100A RF 发生器来驱动,并由 Stanford Research SR1 提供

2018-07-19 16:23:22

AD9520-1 / PCBZ,评估板是一款紧凑,易于使用的平台,用于评估AD9520-1的所有功能。 AD9520-1是一款12 LVPECL / 24 CMOS输出时钟发生器,具有亚皮秒级抖动

2020-04-06 06:30:32

输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。 产品名称:时钟发生器 AD9520-3BCPZ特征低相位噪声、锁相环(PLL)片内VCO的调谐频率范围为

2019-07-09 11:50:41

(LVDS工作模式) AD9571ACPZPEC产品详情AD9571具有多路输出时钟发生器功能,内置专用PLL内核,针对以太网线路卡应用进行了优化。整数N PLL设计基于ADI公司成熟的高性能、低抖动

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140A可编程多时钟发生器评估板。评估抖动性能和功能很容易

2020-07-27 15:01:46

本应用指南讨论了CY2254 PLL时钟发生器的内部结构,并提出一些使用建议。

2014-09-23 10:00:14

NB3N5573DTGEVB,用于SONET的NB3N5573 PLL时钟发生器评估板。 NB3N5573是一款高精度,低相位噪声时钟发生器,支持PCI Express和以太网要求

2019-08-30 08:41:47

NB4L339MNGEVB,GB以太网交换机时钟发生器评估板。 NB4L339时钟发生器评估板,方便有兴趣进行自己的器件工程评估的客户

2019-08-30 08:38:41

SI5324-EVB,SI5324评估板,0.002至710 MHz时钟发生器。 SI5324-EVB为评估SI5316任意速率精度时钟提供平台。 SI5316直接使用器件上的配置引脚进行控制

2019-02-22 09:30:51

特征•单个3.3V电源•高性能时钟发生器,包括集成频率合成器的晶体振荡器电路•低输出抖动,低至380 fs(rms集成在10 kHz–20 MHz之间)•高频下的低相位噪声;在708 MHz时,在

2020-09-10 17:45:08

吗?为什么PLL需要在不同的时钟区域?时钟发生器仅需要1个PLL和MMCM,不使用其他时钟资源。我应该手动限制PLL吗?这个怎么做?我在Kintex 7上有类似的设计,相同的时钟发生器我没有这个错误,我认为Kintex和Artix之间的时钟资源相似

2020-07-20 12:51:25

专业销售、维修、回收 高频 二手仪器。 产品型号: CG635美国斯坦福时钟发生器信息描述:时钟可调频由0.001Hz到2.05GHz少于1PS的RMS抖动可支持CMOS。PECL,ECL,LVDS

2020-08-18 09:08:58

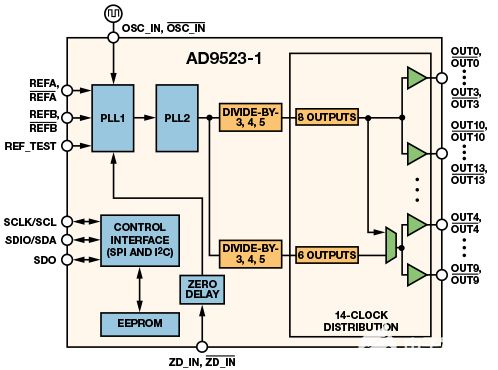

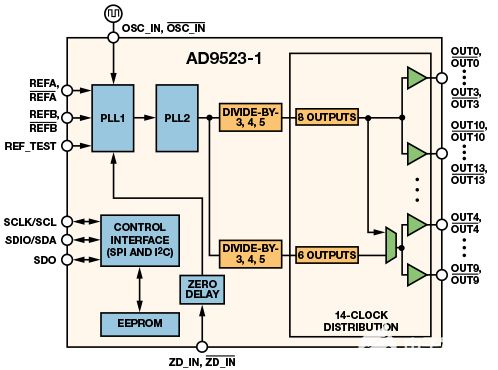

电路板面积,而且允许要求不同频率的 多个器件以同一相位对齐源为时钟源。AD9523, AD9523-1和 AD9524 时钟发生器(如图 1 所示)由 两个串联模拟PLL构成。第一个PLL (PLL

2019-10-31 08:00:00

SI5340-EVB,评估板用于评估Si5340低抖动任意频率时钟发生器。 Si5340采用获得专利的Multisynth技术,可产生多达10个独立时钟频率,每个频率具有0 ppm的合成误差

2019-02-26 09:28:56

SI5341-EVB,评估板用于评估Si5341低抖动任意频率时钟发生器。 Si5341采用获得专利的Multisynth技术,可产生多达10个独立时钟频率,每个频率具有0 ppm的合成误差

2019-02-25 07:03:01

我要做毕业设计 叫 基于lmk03806的高性能可编程时钟发生器的设计与fpga实现,需要有protel 99se画 lmk03806的原理图和fpga的配置电路,用vhdl编程仿真,用fpga来配置lmk03806,求高手求助{:1:}

2013-05-03 23:06:27

找不到联系方式,请在浏览器上搜索一下,旺贸通仪器仪 产品型号: CG635美国斯坦福时钟发生器信息描述:时钟可调频由0.001Hz到2.05GHz少于1PS的RMS抖动可支持CMOS。PECL,ECL

2019-06-16 12:07:43

专业销售、维修、回收 高频 二手仪器。 产品型号: CG635美国斯坦福时钟发生器信息描述:时钟可调频由0.001Hz到2.05GHz少于1PS的RMS抖动可支持CMOS。PECL,ECL,LVDS

2020-12-03 08:39:05

AD9523-1 / PCBZ,AD9523-1评估板旨在支持长期演进(LTE)和多载波GSM基站设计的时钟要求。它依靠外部VCXO提供参考抖动清除,以实现可接受的数据转换器SNR性能所需的限制性

2019-02-22 06:08:25

AD9525 / PCBZ-VCO,用于评估安装了2950MHz VCO的AD9525的所有功能的评估板。 AD9525是一款低抖动时钟发生器,具有正确的LVPECL输出,旨在支持长期演进(LTE)和多载波GSM基站设计的转换器时钟要求

2019-02-26 09:38:38

AD9525 / PCBZ,用于AD9525时钟发生器的评估板。 AD9525旨在支持长期演进(LTE)和多载波GSM基站设计的转换器时钟要求。 AD9525提供低功耗,多输出,时钟分配功能和低抖动

2019-02-25 08:38:34

AD9576 / PCBZ,AD9576评估板提供多输出时钟发生器功能,包括两个专用锁相环(PLL)内核,具有灵活的频率转换功能,经过优化,可作为整个系统的强大异步时钟源,提供扩展功能通过监控和冗余

2019-02-25 09:40:01

SI52147-EVB,用于PoE无线接入点的时钟发生器评估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3标准的9端口PCIe时钟发生器

2020-08-27 14:27:11

?疑问3:是不是使用PLL类型的时钟发生器芯片带来的抖动误差会比较大?针对14位的ADC输入差分时钟有此类型的参考吗? 模拟输入部分:疑问1:参考文档中使用AD8138差分驱动芯片,计划采用5v单电源模式

2018-11-07 09:35:54

噪声抑制和出色的电源抑制比 (PSRR) 来帮助改进无错数据传输。图2显示的是使用LMK03328时对PSRR和TX眼图性能的改进,其原因就在于LMK03328集成了一个LDO。图2:SAW示波器和TI LMK03328时钟发生器的PSRR请在下方给我们留言,告诉我们你在正在研究的、最能从超低抖动中受益的应用。

2018-09-05 16:07:30

描述TIDA-00597 可为时钟发生器提供噪声非常低的输出电源。主要特色低噪声,适用于时钟发生器输出电流高达 800mA低相位噪声输出功率启用和禁用

2018-08-22 07:43:40

~156.25MHz范围的低抖动时钟源。在理想的供电条件下,小数分频PLL可在1 0kHz~20MHz频段内提供低于lps RMS的抖动性能。相反,在有电源噪声的环境中,振荡器很难满足其数据手册中标明的相位抖动参数

2018-09-26 14:33:58

AC1571时钟发生器一款基于PLL的、适用于5G基站应用的时钟发生器。采用数字锁相环技术,以实现最佳的高频低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技术,管脚兼容843N571,可以

2022-08-11 16:26:33

TIDA-00597 可为时钟发生器提供噪声非常低的输出电源。

2009-05-07 15:12:41 0

0 HFAN-04.5.5评估电源噪声抑制比对PLL时钟合成器的影响

Characterizing Power-Supply Noise Rejection in PLL Clock

2009-06-19 07:35:38 50

50 具有单个 PLL 的超低抖动时钟发生器系列 Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:16

具有两个独立 PLL 的超低抖动时钟发生器系列 Function Ultra-low jitter clock generator Number of outputs 8

2022-12-02 13:47:17

汽车类 3.3V 双路 PLL 多时钟发生器 Function Clock generator Number of outputs 4 Output frequency

2022-12-02 13:47:21

8.192MHz 至 36.864MHz、并行控制、3.3V 双路 PLL 多时钟发生器 Function Clock generator Number of outputs 4

2022-12-02 13:47:44

4.096MHz 至 36.864MHz、串行控制、3.3V 双路 PLL 多时钟发生器 Function Clock generator Number of outputs 4

2022-12-02 13:47:45

3.3V 双路 PLL 多时钟发生器 Operating temperature range (C) -25 to 85 Rating Catalog 27-MHz

2022-12-02 13:47:45

8.192MHz 至 36.864MHz、串行控制、3.3V 双路 PLL 多时钟发生器 Function Clock generator Number of outputs 4

2022-12-02 13:47:45

AD9575是一款高度集成的双路输出时钟发生器,包括一个针对网络定时而优化的片内PLL内核。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现线路卡的较高性能。对相位噪声

2023-02-13 10:25:49

AD9571具有多路输出时钟发生器功能,内置专用PLL内核,针对以太网线路卡应用进行了优化。整数N PLL设计基于ADI公司成熟的高性能、低抖动频率合成器产品系列,确保实现较高的网络性能。这款器件也

2023-02-13 10:29:31

AD9572是一款多输出时钟发生器,具有两个片内PLL内核,针对包括以太网接口的光纤通道线路卡应用进行了优化。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现网络的较高性能

2023-02-13 10:37:25

AD9573是一款高度集成的双路输出时钟发生器 , 包括一个针对PCI-e应用而优化的片内PLL内核 。 整数N分频PLL设计基于ADI公司成熟的高性能、低

2023-02-13 10:59:39

针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

2009-12-14 10:22:00 36

36 MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)时钟倍频器,以产生高频时钟输出,用于以太网、10G光纤通道及其它网络设备。Ma

2010-03-01 08:54:52 126

126 AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2023-12-12 14:25:17

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2023-12-29 09:29:50

时钟发生器芯片厂家 时钟芯片是一种基于PLL的时钟发生器,采用ADPLL(全数字锁相环)技术,以实现的高频低相噪性能,并具备低功耗和高PSNR能力,可实现小于0.3ps RMS的相位抖动性能

2024-02-04 11:41:14

MAX9489/MAX9471多输出时钟发生器构建集成时钟源

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如

2008-10-04 20:43:25 922

922

精密时钟发生器电路图

2009-03-25 09:35:22 1054

1054

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL内核和三种不同输出(LVPECL, HSTL,LVDS)的高精度时钟发生器。MAX945x时钟发生器具有四个主要的特点:集成VCXO,工作频率范围宽,PLL

2009-04-22 09:42:01 966

966

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-04-22 10:11:53 407

407

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如MAX9489和MAX9471)的优点,如:降低系统成本、良好的信号完整性、抑制干

2009-05-03 11:07:05 652

652

MAX3625A 低抖动、精密时钟发生器,提供三路输出

2009-08-13 13:01:27 828

828

MAX3624 低抖动、精密时钟发生器,提供四路输出

概述

MAX3624是一款低抖动精密

2009-09-18 08:56:41 682

682

Maxim推出高性能、三路输出时钟发生器MAX3625B

Maxim近日推出高性能、三路输出时钟发生器MAX3625B,适用于以太网和光纤通道网络设备。器件采用低噪声VCO和PLL架构,能够

2009-12-14 17:25:04 1040

1040 MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(PLL)

2010-03-01 08:56:18 1345

1345

MAX3679A高性能四路输出时钟发生器(Maxim)

Maxim推出用于以太网设备的高性能、四路输出时钟发生器MAX3679A。器件采用低噪声

2010-04-14 16:51:49 778

778 DS1091L是一款低成本的时钟发生器,输出频率由工厂预置到130kHz至66.6MHz,标称精度为±0.25%。器件可产生中心抖动或降频抖动扩频输出,具有引脚可选的抖动幅度和抖动速率。

2011-03-16 10:57:41 1036

1036

AD9523提供低功耗、多路输出时钟分配功能,具有低抖动 性能,还配有片内集成锁相环(PLL)和电压控制振荡器 (VCO)。片内VCO的调谐频率范围为3.6 GHz至4.0 GHz。 AD9523旨在满足长期演进(LTE)和

2011-04-11 15:36:28 50

50 德州仪器(TI)(纽约证券交易所代码:TXN)今天宣布推出一款具有业界最佳抖动性能的高度集成的时钟发生器。LMK03806可以帮助设计人员运用一个低成本晶体合成所需的时钟频率,从而

2011-10-08 11:36:42 812

812 MAX3636是一个高度灵活,高精度锁相环(PLL)时钟发生器为下一代网络设备的要求低抖动时钟发生器和强大的高速数据传输的分布进行了优化。

2011-10-11 11:15:22 1329

1329

双环路时钟发生器可清除抖动并提供多个高频输出

2016-01-04 17:41:13 0

0 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。

2017-11-17 02:00:58 752

752

Microchip基于MEMS的时钟发生器

2018-06-07 13:46:00 4534

4534

Microchip基于MEMS的时钟发生器

2018-07-08 01:23:00 3933

3933 AD9523:14路LVPECL/LVDS/HSTL输出 或29路LVCMOS输出 低抖动时钟发生器

2019-07-04 06:18:00 3603

3603 TI推出超低抖动时钟发生器,以实现更可靠的电信基础设施设备,设计人员可以优化系统性能,简化设备配置并减少设计周期时间。

2019-08-09 15:10:28 1652

1652 系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。

2019-08-07 17:51:43 6011

6011

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2020-11-22 11:34:38 2666

2666

AD9523-1:低抖动时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册

2021-03-21 14:28:08 1

1 AD9525: 8路LVPECL输出低抖动时钟发生器

2021-03-21 15:00:20 0

0 AD9540:655 MHz低抖动时钟发生器数据表

2021-03-22 19:57:57 0

0 ADF4360-9:集成压控振荡器数据表的时钟发生器PLL

2021-04-14 14:10:44 0

0 HMC1031:0.1 MHz至500 MHz时钟发生器,带整数N PLL数据表

2021-04-23 20:15:29 6

6 AD9530:4 CML输出、低抖动时钟发生器,集成5.4 GHz压控振荡器数据表

2021-04-24 12:02:38 0

0 AD9551:多业务时钟发生器数据表

2021-04-28 10:30:52 0

0 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515时钟分配IC的高性能ADC的低抖动采样时钟发生器

2021-04-30 09:48:42 13

13 AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

2021-05-08 20:05:05 5

5 AD9575:网络时钟发生器,双输出数据表

2021-05-09 11:06:44 1

1 超低抖动时钟发生器和分配器最大限度地提高数据转换器的信噪比

2021-05-18 20:57:30 0

0 Cypress时钟发生器应用在车辆、工业生产、消费品和网络服务的EMI降低和非EMI降低时钟发生器。 Cypress具有广泛的时钟发生器组合,兼容700MHz的频率和不超过0.7PS的RMS相位抖动

2022-04-22 09:02:09 806

806 超低抖动时钟发生器如何优化串行链路系统性能

2022-11-04 09:50:15 0

0 AD9523、AD9523-1和AD9524时钟发生器(如图1所示)由两个串联的模拟PLL组成。第一个PLL(PLL1)清除参考抖动,而第二个PLL(PLL2)产生高频相位对齐输出。PLL2 还可以产生高基频,从中可以导出各种较低频率。

2023-02-02 17:29:35 829

829

采用PLL的时钟发生器广泛用于网络设备中,用于生成高精度和低抖动参考时钟或保持同步网络操作。大多数时钟振荡器使用理想、干净的电源给出其抖动或相位噪声规格。然而,在实际的系统环境中,电源可能会因板载开关电源或嘈杂的数字ASIC而受到干扰。为了在系统设计中实现最佳性能,了解这种干扰的影响非常重要。

2023-03-08 15:33:00 895

895

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-03-21 19:21:13 0

0 本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量技术,并演示如何可靠地评估参考时钟发生器的电源噪声抑制(PSNR)性能。

2023-04-11 11:06:39 811

811

) 频带内和频带外 (VCO) 噪声的影响。基准时钟发生器的相位噪声性能需要在PLL环路带宽内和带宽外都表现得很出色,以符合更加严格的抖动技术规格要求。

2023-04-17 10:37:30 357

357

9ZXL1951D PCIe 时钟发生器评估板用户指南

2023-07-07 19:19:11 0

0 时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信号的器件。时钟发生器由多个部分组成,其中最核心的是锁相环

2023-10-13 17:39:50 443

443 时钟发生器/PLL频率合成器SOP-82~15V2MHz封装:SOP-8

2022-08-19 15:57:46 3

3 的时钟发生器件的选择上往往少有考虑。目前市场上有性能属性大相径庭的众多时钟发生器。然而,如果不慎重考虑时钟发生器、相位噪声和抖动性能,数据转换器、动态范围和线性度性能可能受到严重的影响。...

2023-11-28 14:33:57 0

0 电子发烧友网站提供《FemtoClock2抖动衰减器和时钟发生器RC325008A数据手册.pdf》资料免费下载

2024-01-14 10:55:06 0

0 电子发烧友网站提供《毫微微时钟网络同步器、抖动衰减器和时钟发生器RC32112A 数据表.pdf》资料免费下载

2024-01-31 10:09:17 0

0

电子发烧友App

电子发烧友App

评论