: 在电路中的某些模块进入休眠或者空闲模式时,我们可以使用之前讲过的Clock Gating技术来降低它们的动态功耗,但是无法降低它们的静态功耗。而Power/Ground Gating技术可以在它们休眠的时候完全关掉它们的电源从而消除它们的静态功耗。 理想情况下,Power gating可以完全消除

2020-09-16 16:04:15 10567

10567

本人在画一个电容式按键控制的智能灯,现在在画触摸部分,白色线内的部分(明显有薄薄的一层)不知道怎样在AD中画这薄薄的一层(把它当作什么来画)。希望大神能给些意见或者建议。

2018-06-20 17:31:09

动态功耗调节介绍

2021-02-05 07:12:25

需求来说,eSR具有更好的图像质量-推理速度均衡。弥补经典与深度学习上采样之间的空白对于大量采用该技术非常重要。 本文贡献包含以下几点: 提出了几种一层架构以弥补经典与深度学习上采样之间的空白

2023-03-06 14:05:36

降低一个MCU的主频就能降低运行的功耗吗

2023-10-11 08:15:48

降低FPGA功耗的设计技术 Design Techniques to Reduce Power Consumption Each generation of FPGAs gets

2009-12-18 16:49:59

设计技巧为什么能够节省功耗?降低FPGA功耗的设计技巧有哪些?

2021-04-30 06:04:19

低功耗∑-Δ产品的演变,以帮助说明所实现的信号链集成的完整性,并突出强调这给我们测量能力带来的需求和进步。我们现在希望让SiP(系统化封装)、微型模块和模块更上一层楼,客户将再次向我们提出新的测量挑战

2018-10-23 14:18:35

AD在复制整块PCB后,如何在粘贴时只粘贴某一层或某几层?

2019-09-12 16:01:25

Altium 中怎么将焊盘盖上一层油,不让画出来的焊盘裸露?就像下图所示一样

2016-10-21 22:02:36

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能够做到如此低的功耗是因为什么?

2021-04-30 06:08:49

技术亚阈值漏电流是静态功耗产生的主要原因之一,降低亚阈值漏电流将有效地降低芯片的静态功耗。亚阈值漏电流的解析模型如下公式所示:Vt为阈值电压,n为亚阈值摆幅系数,W为晶体管的宽度,L为长度,μ为电子

2020-04-28 08:00:00

。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式,允许采用动态电压和频率调节技术来降低系统整体实际功耗。提供可选择

2019-07-05 07:19:19

综合过程中功耗减少的补充。 值得注意的是,功耗是一个"机会均等"问题,从早期设计取舍到自动物理功耗优化,所有降低功耗的技术都彼此相互补充,并且需要作为每个现代设计流程中的一部分加以

2017-06-29 16:46:52

PADS layout中,这里说的可以走线什么意思,每一层不都是可以走线的吗?

2019-04-11 08:36:41

PADS9.5 LAYOUT 设置元件 怎样 可以重叠放置 大的中间小的 同一层的?

2017-08-04 15:39:15

PADS设计4板,第一层基板挖一个大矩形槽,露出第二层基板,再在第二层基板挖一个小矩形槽,嵌套的。请问怎么实现?

2023-03-24 11:16:33

接地层上的ADC。两层之间的接地噪声直接添加到时钟信号,并产生过度抖动。抖动可造成信噪比降低,还会产生干扰谐波。图7. 从数模接地层进行采样时钟分配。混合信号接地的困惑根源大多数ADC、DAC和其他混合

2014-11-20 10:58:30

如题,想要计算内外层每一层的敷铜面积,有没有什么计算方法或者小工具可以使用?有些板子有敷铜百分比硬性要求。

2021-02-23 15:01:28

请问谁知道pcb覆铜在哪一层?

2019-11-05 16:51:51

pcb只显示一层是怎么回事呢

2019-08-16 00:54:47

那一层透明的我不知道按到什么了,怎么关闭啊

2019-08-16 05:35:09

为什么在同一层铺动态铜皮,有的可以自动避让有的就没有呢?

2019-07-23 05:35:22

为什么多晶硅栅上还要再摞一层钨?不用不行吗? 求大虾指点

2012-01-12 17:22:54

正常情况下打开封装库文件像顶层丝层,焊盘层,底层丝印层,都会同时显示出来。现在我在打开封装库文件时只能显示一层,其他层面不能同时显示出来,这是为什么?所有的层面都有打开啊???

2012-08-11 15:05:37

本帖最后由 eehome 于 2013-1-5 09:54 编辑

为什么有的人做PCB封装时要加一层机械层1的网状物?这样做有什么作用吗?做成的PCB上也没有显示啊?

2012-08-23 11:50:22

1、画线时,一直怎么在第一层上,怎么切换,怎么设置;2、画线时,同时放置焊盘,怎么快捷操作,谢谢指点下。

2019-08-13 22:44:23

大大降低系统功耗,这可以从单片机的供电电压、内部结构、系统时钟和低功耗模式等几方面来考察一款单片机的低功耗特性。一般来讲,用户在选择技术供应商和产品过程中,需要对下面的一些重要硬件参数进行更加深入的考量:

2019-06-20 08:06:05

公司最近开发电池供电的低功耗模块,万用表示波器很难测出动态电流,真心问问做低功耗或者穿戴设备方面的工程师或者测试设备技术厂家技术人员或者各路“牛”,你们用什么设备测试?动态定电流范围较大ua - 几十毫安,变化速率快

2015-01-10 22:53:53

的基于使用频率的状态机值的选择等。 为了更好地理解本文将要讨论的设计技巧为什么能够节省功耗,我们先对功耗做一个简单介绍。 功耗包含两个因素:动态功耗和静态功耗。动态功耗是指对器件内的容性负载充放电所需

2012-01-11 11:59:44

请问做单面板元件库时元件面的丝印和焊接面的丝印分别放在哪一层?一些注解文字放在哪一层?

2011-12-13 13:59:13

市场上已有的解决方案,以降低开发成本。在当今对成本和功耗都非常敏感的“绿色”环境下,对于高技术企业,两种挑战都有什么影响呢?第一种挑战意味着开发全新的产品,其功能是独一无二的,具有较低的价格以及较低

2019-08-09 07:41:27

单片机的本质只是一个工具。因此,更为重要的是模拟电子,数字电子以及其它基础的专业课程。第一层 : 我来了第二层 真的打呀第三层 并肩作战,时间,说爱你不容易第四层 状态,你在哪里第五层 时间,还是

2015-11-01 08:50:35

第一层 : 我来了处在这一层的典型是可以用C语言写简单的逻辑控制,如闪烁LED,简单数码管显示,简单外围模块驱动实验。一般对单片机感兴趣,经常动手实践的人,半年左右,可以练到此地步(针对没有接触过

2018-03-22 11:46:51

第一层 : 我来了处在这一层的典型是可以用C语言写简单的逻辑控制,如闪烁LED,简单数码管显示,简单外围模块驱动实验。一般对单片机感兴趣,经常动手实践的人,半年左右,可以练到此地步(针对没有接触过

2018-09-07 10:13:49

在一个平面上铺一层铜和铺两层铜最后的实际厚度是多少。是两倍的关系还是说是一样的厚度,因为考虑到要过大电流,线宽不是很大。

2015-12-23 10:36:38

FPGA的功耗高度依赖于用户的设计,没有哪种单一的方法能够实现这种功耗的降低,如同其它多数事物一样,降低功耗的设计就是一种协调和平衡艺术,在进行低功耗器件的设计时,人们必须仔细权衡性能、易用性、成本、密度以及功率等诸多指标。

2019-08-15 08:28:42

低功耗mcu的选择方法如何降低mcu的功耗

2021-02-24 06:11:07

多层板的某一层中,如何删除一部分负片?因为这部分附近有高压,担心高压会有影响,所以想删掉这附近的负片。

2019-08-22 04:24:44

复杂器件专业技术相结合,将为系统供应商提供低功耗的芯片方案,供他们在此基础上持续提高带宽容量,并完成更智能的处理。此外,TPACK提供的芯片解决方案可以导入到最新的FPGA中,进一步降低功耗。最终实现

2019-07-31 07:13:26

AD中画PCB板时如何将某一层调为高亮?

2019-08-02 05:35:13

易失性FPGA的电源特性是什么?如何在进行板级设计时,降低系统的静态与动态功耗?

2021-04-08 06:47:53

请问如何添加一层机械层?谢谢

2019-09-17 02:56:08

如何采用创新降耗技术应对FPGA静态和动态功耗的挑战?

2021-04-30 07:00:17

节省功耗的特性的实现和各种最少功耗数据存储技术的实现。除此之外,设计中采用一些低功耗技巧,也可以降低静态功耗。 IGLOO具有功耗友好的器件架构,能提供静态、睡眠、Flash*Freeze功耗模式

2020-05-13 08:00:00

高低电平翻转跳变沿期间,电流很大,存在较大功耗,所以,降低硬件电路功耗主要是降低电路动态功耗。 (3)采用多CPU系统 尽管现在已有各种可在不过多加重功耗负担的前提下提高性能的技术,但用一个芯片

2020-07-08 15:52:10

,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。 另一种常用的时钟技术就是可变频率时钟。它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控

2016-06-29 11:28:15

从当前嵌入式消费电子产品来看,媒体处理与无线通信、3D游戏逐渐融合,其强大的功能带来了芯片处理能力的增加,在复杂的移动应用环境中,功耗正在大幅度增加。比如手机,用户往往希望待机时间、听音乐时间,以及看MPEG4时间能更长。在这样的背景下,如何降低入式芯片的功耗已迫在眉睫。

2019-08-28 08:27:58

可以做哪些措施来降低功耗

2023-10-23 07:51:09

自己做了一个电路板,因为功耗除了点问题,怎么降低电路板功耗呢

2019-08-07 22:21:34

图中控件快捷菜单有3层,第一层“3”,第二层“3.2”,第三层“3.2.1”“3.2.2”,通过事件结构里面的“快捷菜单选择”只能触发最后一层的“3.2.1”“3.2.2”,能不能实现第二层和第三层都可以触发?也就是点“3.2”能触发事件,点“3.2.1”也能触发事件

2016-04-14 10:06:36

请问PADS 中金手指部分放在那一层里。是不和镀锡层一个层啊!solderMaks

2012-11-05 08:25:29

请问PADS 中金手指部分放在那一层里。是不和镀锡层一个层啊!solderMaks

2012-11-05 08:38:17

功耗:(1)使用clock gating 技术减小活动因子是降低翻转功耗的办法之一,这个方法已经很成熟,易于采用;(2) 减小毛刺Glitch减少毛刺会使活动因子变小,进而帮助降低功耗;竞争和冒险

2022-06-09 18:06:15

集电极层中杂质浓度的降低,这有助于抑制空穴注入(2)。SiC-SBD在反向恢复和导通损耗方面的改进通过使用SiC-SBD,高速混合模块可以将反向恢复峰值电流降低约60%。SiC-SBD是不带少数

2020-09-02 15:49:13

人们对低功耗设备和设计技术的兴趣激增。通过回顾已提出的降低功耗的技术,深入了解低功耗设计中的一些基本权衡。设计的主要策略是以速度换取功耗,不浪费功耗,并找到一个较低的功耗问题。 文章通过定义

2020-07-07 11:40:06

的重新安排却只能降低5%的翻转次数。在不同的低功耗设计层次,考虑的重点也不相同。比如说只有在工艺级设计时,设计者才考虑通过扩散区的掺杂浓度来影响阈值电压。近年来,降低功耗的技术逐渐从电路层向结构层,从

2013-05-16 20:00:33

文档里说CLA 没有堆栈,不支持函数的嵌套,那请问CLA只允许调用一层函数吗?

2020-07-19 13:49:39

请问FPGA与DDR3是否必须在同一层放置,由于现在不在同一层,软件调试的时候图像有抖动,软件说是因为FPGA与DDR3未在同一层,导致时序有问题。

2018-12-26 09:37:37

什么是TICKLESS?怎么能实现功耗的降低呢?TICKLESS是如何去实现功耗降低的呢?

2022-02-24 08:02:02

pcb裸铜的logo放在哪一层?

2023-10-16 07:29:19

PCB中不在同一层的线形成锐角有关系吗?硬件工程师 说不能这样走,但是我的想法是又不在同一层为什么不能?

2019-05-21 10:00:46

图一是视频里面的,图二是我自己做的。请问如何像图一一样显示一层?不显示背面的?还有怎么切换pcb的正反面?

2019-04-29 00:19:47

基于DSP的测试技术与传统的测试技术相比,有哪些优势?基本的混合信号测试技术包括哪些?采样和重建在混合信号测试中的应用

2021-04-21 06:41:10

如何利用FPGA设计技术降低功耗?

2021-04-13 06:16:21

画PCB怎样,只显示单独的一层,其他层的线看不见?希望大神给予指到

2019-09-12 01:05:14

描述TIDA-00675可使用负载开关动态开启/关闭负载,从而降低功耗。设计指南说明了开关频率、占空比和放电电阻的使用如何影响功耗。特性通过动态开启/关闭负载来降低功耗频率、占空比和负载电流对功耗

2022-09-20 07:17:32

摘要 目前,为了降低功耗,越来越多的芯片支持动态电压与频率调节DVFS(Dynamic Voltage and Frequency Scaling)。本文列举了基于软件和硬件的DVFS实现,验证了DVFS在降低功耗

2009-03-29 15:14:37 2482

2482

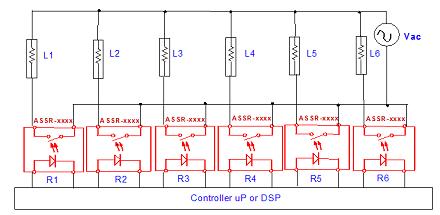

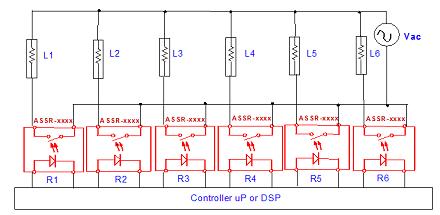

固态继电器的动态功耗和设计考量

1.0 介绍

对于低电压信号或低功率切换应用,具备MOSFET输出的光学隔离固态继电器(SSR, Solid State Relay)可以比传统机电式继

2010-02-22 09:14:58 2474

2474

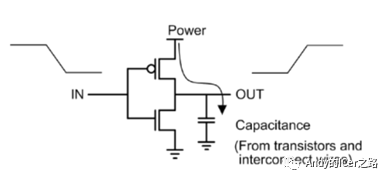

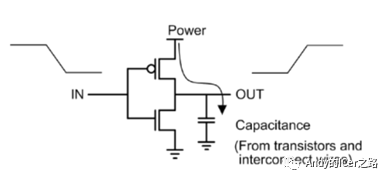

降低移动设计功耗的逻辑技术方法

本文将探讨在混合电压供电的移动设计中,混合电压电平如何提高ICC电源电流及逻辑门如何降低功耗。当前的移

2010-04-15 15:00:46 666

666

设计人员总是在寻找减少不需要的功耗组件的方法,无论是通过以低功耗技术的方式设计设计,还是采用可以降低功耗的工艺。但是,其中一些解决方案的代价是性能,可靠性,芯片面积或其中的几个。最终,人们必须在功率,性能和成本之间达成妥协。下面的文章旨在讨论其中的一些技巧。这些技术分为建筑技术和基于过程的技术。

2019-08-09 14:32:55 14246

14246

电子发烧友网站提供《通过动态切换降低功耗的参考设计.zip》资料免费下载

2022-09-06 15:33:14 0

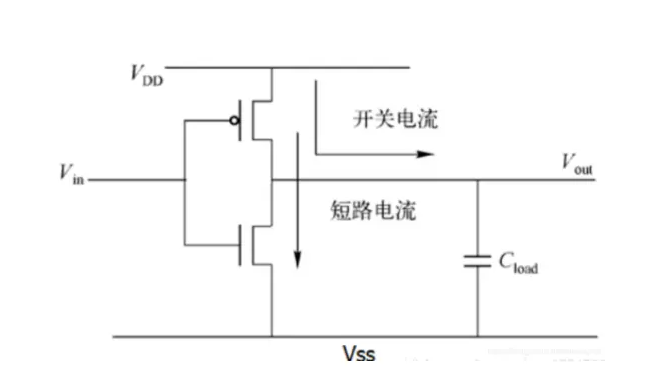

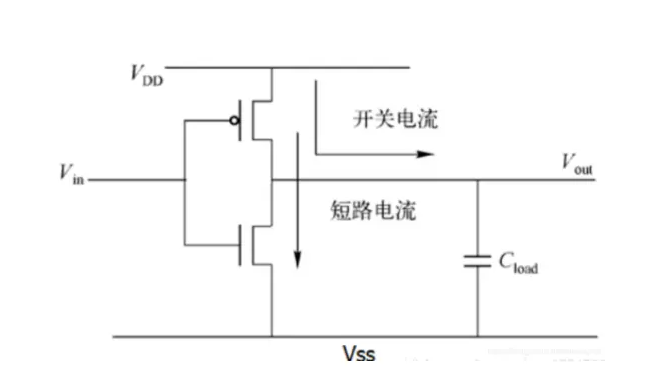

0 翻转功耗是由充放电电容引起的动态功耗,其推导过程很简单,但是这个最终的结果却十分重要。

2023-06-05 17:36:26 2034

2034

CMOS器件是一种采用CMOS技术制造的电子器件,具有低功耗、耐电磁干扰、高噪声免疫性等优点,被广泛应用于现代电子领域。本文将介绍cmos动态功耗公式以及和cmos动态功耗有关的电路参数。

2023-07-21 15:55:55 2317

2317

。 优化软件算法:通过优化软件算法,减少处理器的计算量,从而降低功耗。 休眠模式:对于不需要时时采集数据的设备,采用休眠模式,降低功耗。 动态调整采样率:根据需要采集数据的频率来动态调整采样率,降低功耗。 优化供

2023-10-11 09:29:00 511

511

电子发烧友App

电子发烧友App

评论