在所有的功率电子应用中最优先考虑的之一是获得高效率。随着新标准的出现,在许多应用中有源功率因数校正(PFC)是必需的。电子元件的附加损耗可能增加散热片和和整个应用的尺寸,其目标是把损耗减到最小而不增加成本。

标准 EN61000-3-2 对接到公共电网中的功率应用是强制的。对许多应用而言一个外加的有源PFC的功能不得不被集成到已存在的功能中。这些应用的尺寸大小常常由用于散热的散热片决定。通过把外加的PFC功能集成起来获得尽可能小的散热片是一个重要的手段。

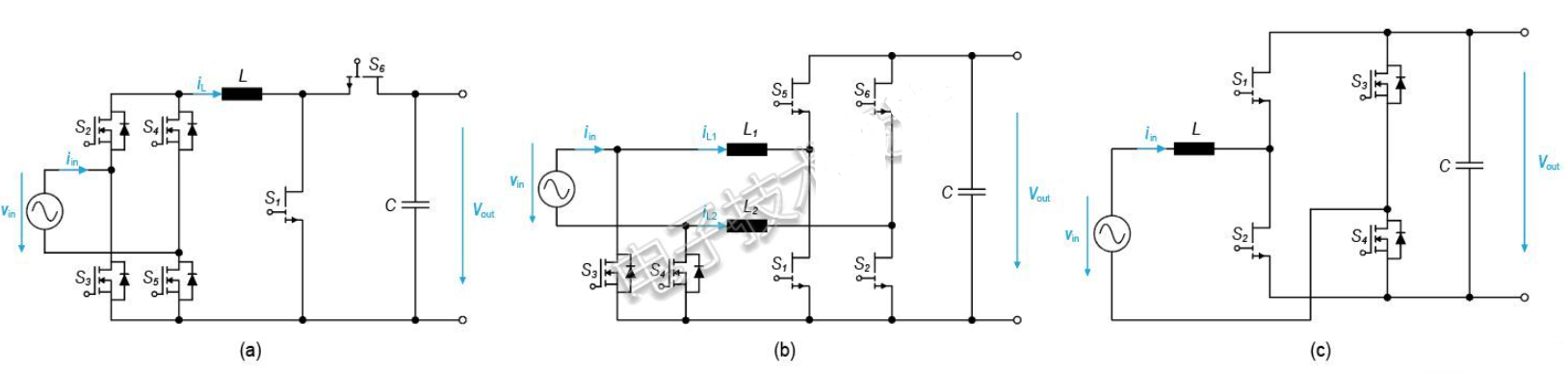

功率损耗产生在半导体芯片和电抗中。通过选择低损耗的元件来优化电路是必需的。采用新概念的一个高效PFC拓扑,4个输入整流管中的2个被省掉了,在每个半波中有一个半导体结的损耗被消除了。

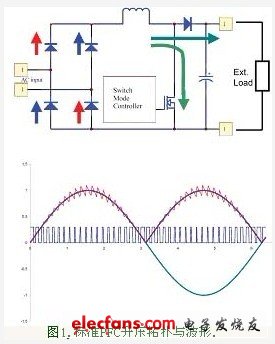

标准的 PFC升压拓扑

在大多情况下升压拓扑结构被用于有源功率因数校正。电流在向输出供电时每半波必须通过至少3个半导体结。

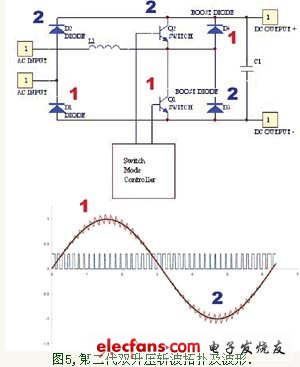

输入整流器把AC电压转换成一个波动的DC电压。PFC电路把两个半波升到DC输出电压。

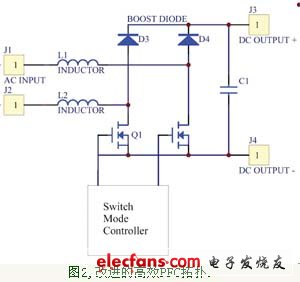

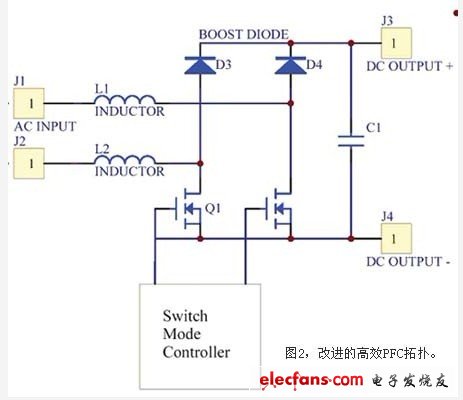

在一种改进的高效PFC中,PFC电抗被分成了2个电感量各为一半的电感。对每个半波而言省掉了输入整流器,只需一个升压斩波。在每个半波电流只需通过2个半导体器件。

在理论上这个新的拓扑看起来好像是减小有源PFC应用中损耗的高效的替换方案。但是下一步我们将采用仿真来检验这个理论。

从仿真结果看,所有的PFC输出信号相对于输入端(参考地)都随着PWM频率而震荡。

这个问题是系统性的,原因是所有的输入都接有一个PFC电抗。这个结果是输出相对输入电源而高频震荡。因此采用外部的滤波器是不可能解决EMI问题的。

DC输出和被连接的电路相对于输入电网高频震荡。由此而产生的高的EMC发射对许多应用而言是不可接受的。用这种拓扑结构,采用隔离变压器的应用设计是很困难的,象电机驱动这样没有变压器的应用是完全不可能的。

因此,人们希望获得一个高效的PFC解决方案,同时没有EMC的缺点。

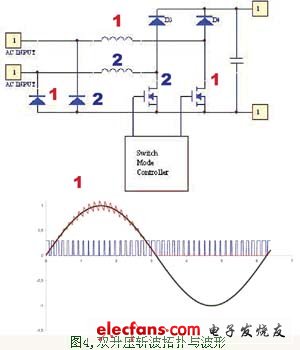

双升压斩波拓扑结构

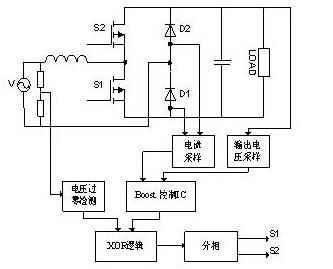

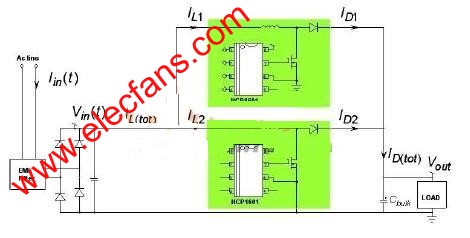

一个由泰科电子发明的新的拓扑解决了这个问题。与第一个设计理念不同的是电抗没有被分开,2个电感与标准升压斩波拓扑使用的电感具有相同的电感量。但是在每个半波中只有一个电感被使用。另一个被另加的整流二极管旁路掉了。

采用这种方案,输出并不相对于AC输入或GND而高频震荡。动作方式与标准的结构是相同的。但是用在标准升压斩波中的输入整流二极管的损耗被砍掉了一半。

1,第一个半波使用第一部分PFC电路升压到DC输出电压。 第二个电抗被第一个整流二极管旁路掉。

2,第二个半波期间, 第二个PFC电路把输入升到DC输出电压。在这儿第一个电抗被旁路掉了。

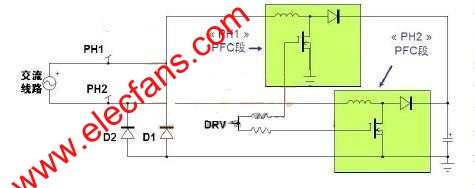

采用第二代拓扑结构,仅用一个电抗就可能获得高效PFC的好处:

在这儿流经PFC电抗的电流是双向的。

1,正半波被低侧的开关和高侧的升压二极管升压。低侧的整流二极管建立了一个返回通路。

2,负半波被通过高侧的开关和低侧的升压二极管而升压。高侧的整流二极管建立了返回路径。

同样采用这个拓扑结构,标准升压斩波的拓扑结构中的输入整流二极管的损耗被砍掉了一半。这个电路的优点是采用和标准升压斩波拓扑结构中同样的PFC电抗。

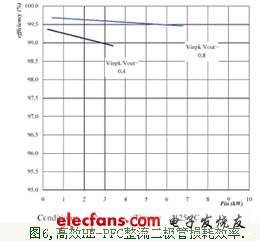

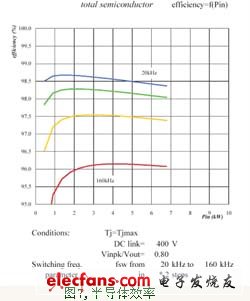

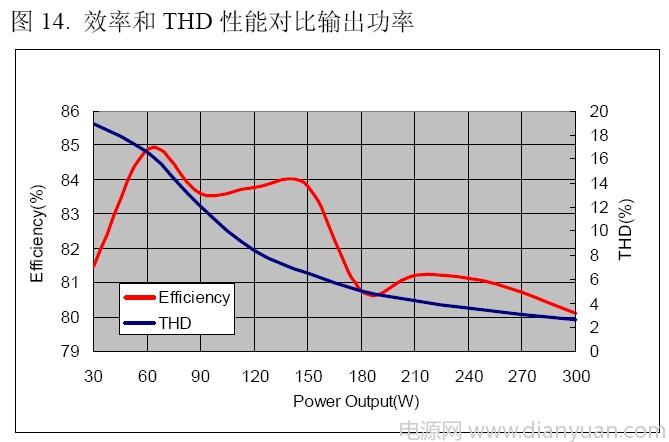

高效拓扑结构的效率

在一个采用230VAC输入电压系统,新的高效的HE-PFC的整流二极管的损耗被计算,是0.5%的总的输入功率 (Vout = 400VDC, Pout = 6kW)。在一个110VAC系统, 新的高效HE-PFC的整流二极管损耗被计算出来,是1%(Vout = 400VDC, Pout = 3kW)。见下图:

在230V系统中半导体的效率是:97.4% (Vout = 400VDC, Pout = 6kW, fPWM = 80kHz)。效率的优势被计算,是0.5%。见图7:

在一个110VAC系统半导体的效率是94.8% (Vout = 400VDC, Pout = 3kW, fPWM = 80kHz)。效率优势被计算,是1%。

在所有的110 VAC 和230 VAC 输入,与标准的升压斩波相比较半导体损耗有大约19%的降低。

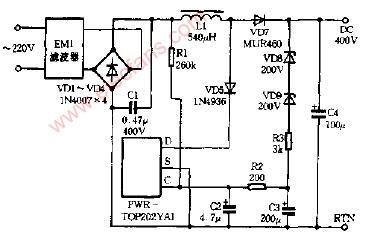

模块解决方案

泰科电子提供了模块支持这两个方案。

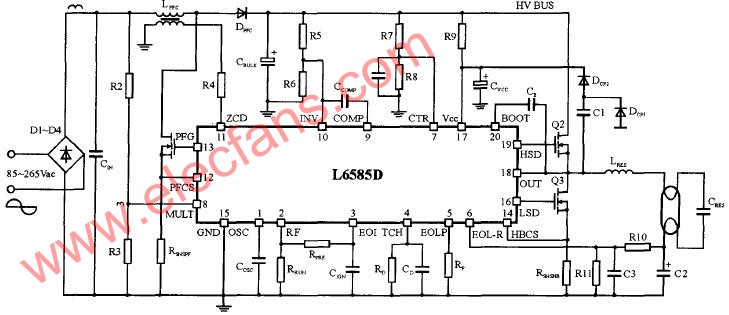

flowPFC 0 - HE

泰科电子模块flowPFC 0 - HE 提供新的双升压斩波拓扑结构。

其特性包括:最大4.5kW在 100kHz;用于双升压斩波的半导体都被集成;为获得低电感输出集成了电容;用于电流检测的分流电阻;温度传感器。

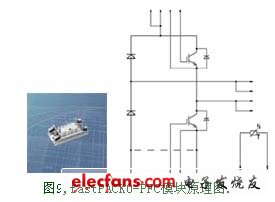

fastPACK 0 - PFC

泰科H桥结构的 fastPACK 0 - PFC 模块支持 高效双向升压斩波拓扑。其特性为:最大 6kW ;所有的用于双向升压斩波的功率半导体都被集成 ;引脚支持在DC输出侧低外加吸收电容的低电感连结;温度传感器 。

电子发烧友App

电子发烧友App

评论