五、实验要求

根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试和实验过程;设计程序、程序分析报告、仿真波形图及其分析报告。

1. 设计思路

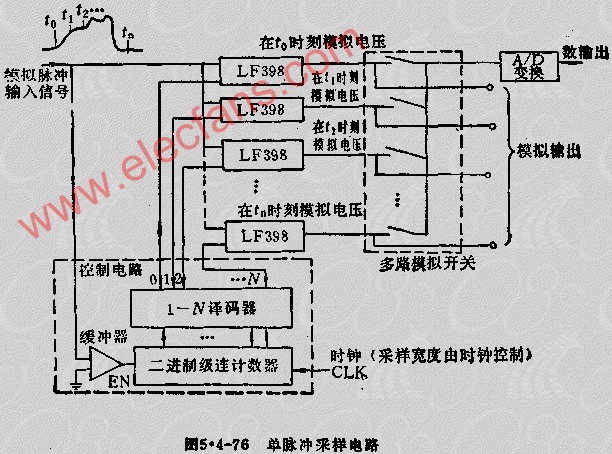

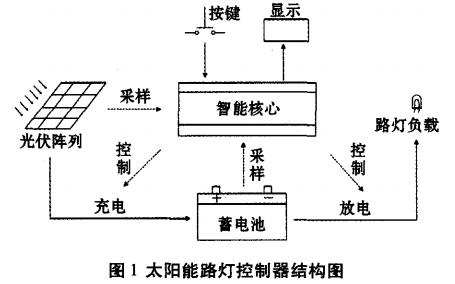

6. 由题意知,我们要设计一个电路与A/D转换器ADC0809相连,通过接受时钟输入来决定状态,通过对不同状态输出不同的控制信号,实现对ADC0809的采样控制,最终输出稳定的采样电压。本实验中将设计如下进程。

设置两个信号Current_State、Next_State,以便实现状态的通知。

① 主控时序进程REG

总体设计思想:用REG控制整个采样控制电路的状态,是整个电路的总指挥。

通过监测ADC0809输出的信号,实现不同状态的转换,进而控制不同不同的进程Process。

主控时序进程REG只输出状态,只接收ST1。

当状态为ST0的时候,开始新一轮的采样;

当接收ST1的时候,通知COM2将采样数据锁存,输出。

进程REG对信号:CLK、Next_State信号敏感

② 组合进程COM1

总体设计思想:用COM1实现COM2对REG的通知,是整个电路的传令兵;用COM2控制整个电路,是整个电路状态改变的具体执行者。

。

当EOC=1的时候,通知REG,以便改变电路状态。

进程COM1对信号Current_State和EOC敏感

③ 进程LATCH

总体设计思想:用LATCH来锁存转换好的数据,并控制数据的输出。

进程LATCH对信号LOCK,REGL敏感

程序设计

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITY ADCINT IS

PORT(D :INSTD_LOGIC_VECTOR(7DOWNTO0);--来自0809转换好的8位数据

CLK:INSTD_LOGIC; --状态机工作时钟

EOC:INSTD_LOGIC; --转换状态指示,低电平表示正在转换

ALE:OUTSTD_LOGIC; --8个模拟信号通道地址锁存信号

START:OUTSTD_LOGIC; --转换开始信号

OE:OUTSTD_LOGIC; --数据输出3态控制信号

ADDA:OUTSTD_LOGIC; --信号通道最低位控制信号

LOCK0:OUTSTD_LOGIC; --观察数据锁存时钟

LED:OUTSTD_LOGIC; --用来指示仿真程序是否正确

-- LED2: OUT STD_LOGIC; --2用来指示仿真程序是否正确

Q :OUTSTD_LOGIC_VECTOR(7DOWNTO0)--8位数据输出

);

END ADCINT;

ARCHITECTURE behav OF ADCINT IS

TYPE states IS(st0,st1,st2,st3,st4); --定义各状态子类型

SIGNAL current_state , next_state : states := st0;

SIGNAL REGL :STD_LOGIC_VECTOR(7DOWNTO0);

SIGNAL LOCK :STD_LOGIC; --转换后数据输出锁存时钟信号

BEGIN

ADDA 《= ‘1’;--当ADDA《=‘0’,模拟信号进入通道IN0,当ADDA《=‘1’,则进入通道IN1

Q 《= REGL; LOCK0 《= LOCK;

------------------进程REG---------------------

--用REG控制整个采样控制电路的状态,是整个电路的总指挥。

PROCESS(CLK)

BEGIN

IF CLK=‘1’ and CLK‘eventTHEN -- 检测时钟上升沿

--LED《=’0‘;

IF next_state=st0 THEN -- 初始化状态机

current_state《=st0;

ELSIF next_state=st1 THEN --开始转换(st1)

current_state《=st1;

ELSIF next_state=st2 THEN --等待转化完毕,检测EOC是否为高电平

current_state《=st2;

ELSIF next_state=st3 THEN

-- LED《=’1‘;

current_state《=st3;

ELSIF next_state=st4 THEN

current_state《=st4;

ENDIF;

ENDIF;

ENDPROCESS;

------------------进程COM2---------------------

--用COM2控制整个电路,是整个电路状态改变的具体执行者。

PROCESS(current_state,EOC)

VARIABLE First_EOC :STD_LOGIC;

BEGIN

--LED2《=’0‘;

IF current_state=st0 THEN -- 初始化状态机

ALE《=’1‘;

START《=’0‘;

OE《=’0‘;

LOCK《=’0‘;

next_state《=st1;

ELSIF current_state=st1 THEN --开始转换(st1)

START《=’1‘;

ALE《=’0‘;

--IF EOC=’0‘ THEN -- 转换结束

next_state《=st2;

First_EOC:=EOC;--在状态1记录EOC,以便后面判断AD是否开始转换

--END IF;

ELSIF current_state=st2 THEN --等待转化完毕,检测EOC是否为高电平

START《=’0‘;

OE《=’0‘;

if ’1‘=(First_EOC XOR EOC)then

IF EOC=’1‘ THEN

-- IF EOC=’1‘ THEN

next_state《=st3;

-- END IF;

-- else

-- next_state《=st2;

ENDIF;

else

next_state《=st2;

ENDIF;

ELSIF current_state=st3 THEN

--LED2《=’1‘;

IF EOC=’1‘ THEN -- 转换结束

OE《=’1‘;

next_state《=st4;

ELSE

OE《=’0‘;

ENDIF;

ELSIF current_state=st4 THEN

OE《=’0‘;

LOCK《=’1‘;

next_state《=st0; --开启下一轮新的转换

ENDIF;

ENDPROCESS;

------------------进程LATCH---------------------

--用来控制电路的输出

PROCESS(LOCK,REGL)

VARIABLE cq :std_logic_vector(7DOWNTO0);--用来保存数值

BEGIN

IF LOCK=’0‘ THEN

cq:=D;

ELSIF LOCK=’1‘ THEN

REGL《=cq;

ENDIF;

ENDPROCESS;

ENDARCHITECTURE behav;

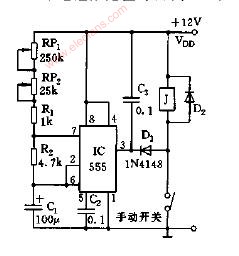

2. 仿真分析

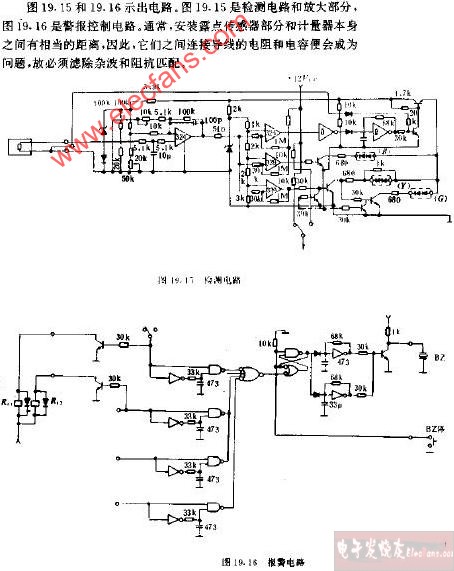

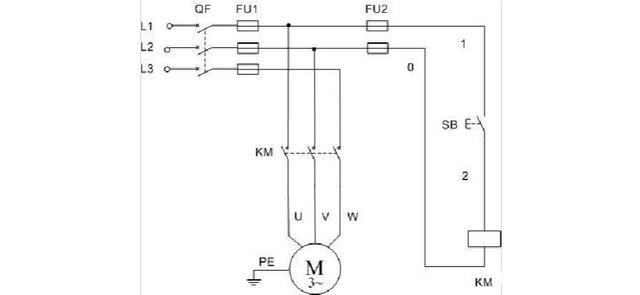

图8-5 仿真波形图

由8-5可知,仿真波形和图8-4控制ADC0809采样时序图一致。

3. 硬件测试和实验过程

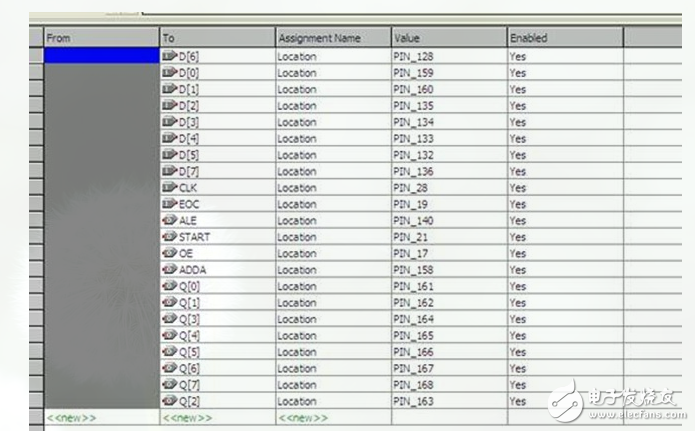

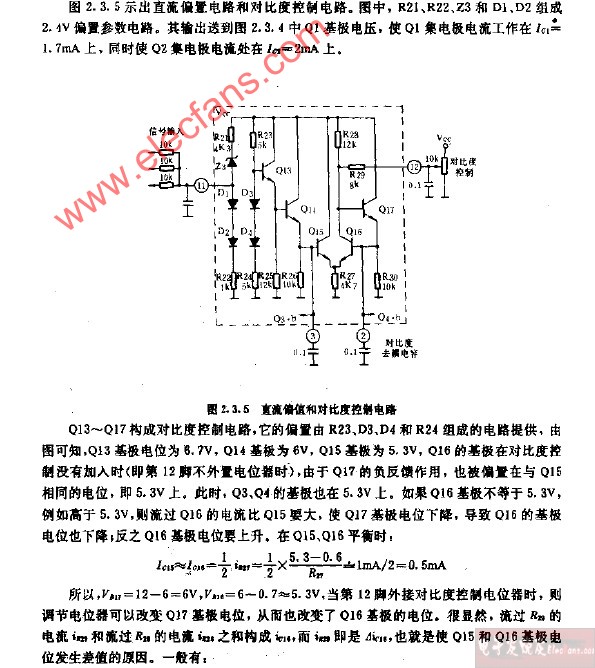

表1-1 ADCINT在GWAC6板上目标芯片EP1C6Q240C8的引脚锁定信息

电子发烧友App

电子发烧友App

评论