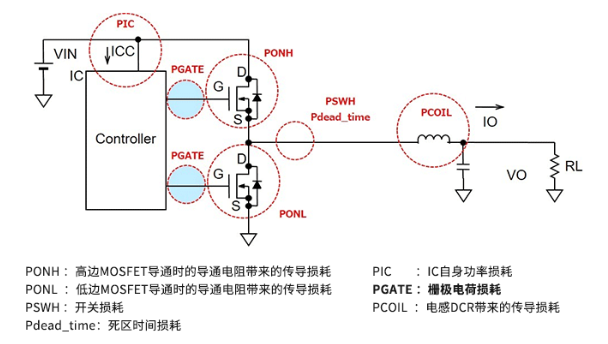

在同步降压电源应用中,降低MOSFET导通电阻对同步整流器而言十分关键,因为多数情况下,快速恢复式整流电流通过MOSFET通道电阻所造成的功率损耗是总功耗中最大的一部分。然而,其他一些因素也不容忽视。

---较高的门极驱动电压电平可将更多电荷充入MOSFET的栅极-源极(gate-to-source)连接点,从而在MOSFET驱动器级造成了更大的损耗。此外,较高的门极充电需求还会造成更长的升降时间,这将在同步降压转换器的高侧MOSFET内影响开关损耗。为了提高效率,施压应用于驱动MOSFET门极,以使增加的门极电荷与开关损耗小于其通过降低Rds(ON)所节省的功率。例如,如果高侧MOSFET增加0.5W的功耗,而同步MOSFET中节省了1W,则该方案可以接受。

门极电压的考虑事项

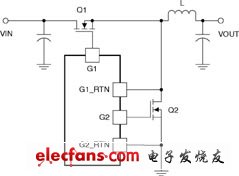

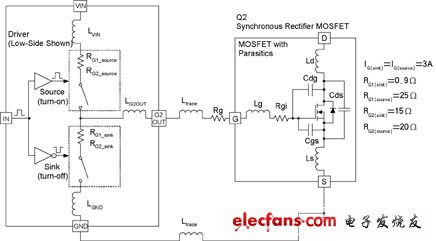

---采用两种相对的电压驱动控制MOSFET Q1与同步MOSFET Q2(如图1所示)的门极需要经过仔细的考虑。额外离散部件的需求、对PCB路由的影响以及最佳驱动电压振幅(可能已获得、也可能暂未获得)的需求,这些权衡因素都对降低MOSFET Rds(ON)以获得潜在效率不利。

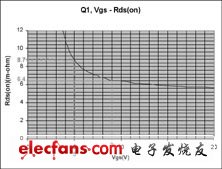

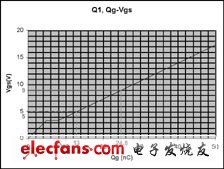

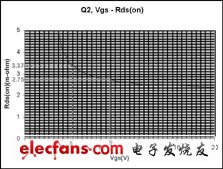

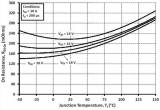

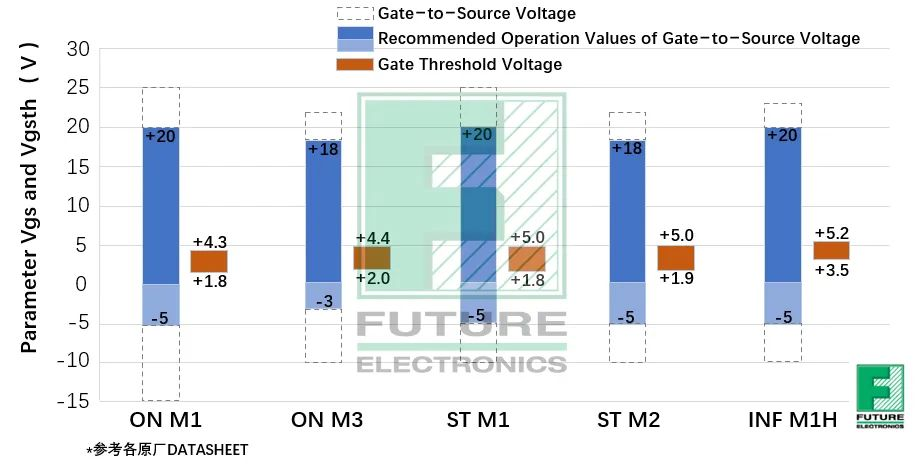

---作为例子,我们使用仲裁器件(arbitrary device)对控制MOSFET与同步整流器MOSFET进行如下分析。为了能够突出门极-源极电压(VGS)相对另一门极-源极电压的优势,必须仔细考察每个MOSFET的Rds(ON)对门极驱动电压以及门极驱动电压对门极电荷的曲线图。

---图2~图5所示是从大多数制造商的数据表中获得的典型MOSFET性能特性曲线图,其将作为下述应用实例的依据。

---图2突出显示了控制MOSFET Q1当VGS=5V以及VGS=9V时Rds(ON)的值。由于Q1更倾向于开关损耗,因此在选择时通常首先考虑较低的门极电荷,其次考虑Rds(ON)。当VGS=5V时,Rds(ON)=8.7mΩ;VGS=9V时,Rds(ON)=6.4mΩ。与此类似,图表示了当VGS从5V增加至9V时对门极电荷的影响。当VGS=5V时,Qg=13nC;VGS=9V时,Qg=24.8nC。表1是对上述结果的总结。

---图4突出显示了整流器MOSFET Q2当VGS=5V以及VGS=9V时的Rds(ON)的值。由于Q2更倾向于导电损耗,因此在选择时首先考虑尽可能最低的Rds(ON),其次考虑门极电荷。当VGS=5V时,Rds(ON)=3.37mΩ;当VGS=9V时,Rds(ON)= 2.75mΩ。与此类似,图5显示了VGS从5V增加到9V时对门极电荷的影响。当VGS=5V时,Qg=37.5nC;当VGS=9V时,Qg=76nC。各VGS所对应的MOSFET参数如表1所示。

---受最大负载电流的影响,由较高VGS产生的低Rds(ON)将导致更低的导电损耗,直至某一特定截至频率上开关损耗开始占优势。在开关损耗占优势的较高频率范围内,应首选由较低VGS引起的低门极电荷。而在导电损失占优势的较低频率范围内,则应选择由较高VGS引起的低Rds(ON)。就提高效率而言,最好的选择可能是采用较低VGS驱动控制MOSFET以最大程度地减少开关损耗,以及采用较高VGS驱动同步整流器以降低导电损耗。然而,由于大多数同步降压MOSFET驱动器不提供以不同电压分别独立驱动控制门极与同步门极的选项,因此该解决方案不具有实际意义。

---下面的应用实例将对两种VGS条件下的效率进行比较。为了简化起见,对每种情况我们都采用相同振幅的VGS用于控制MOSFET及同步MOSFET。

应用实例

--- 首先给定以下条件:

VIN=5V

VOUT=1.8V

IOUT=20A

D=0.36

Fsw=200kHz

Rg=0Ω

LLUMP=50nH

---MOSFET驱动器特性:

---图6显示了具有代表性的模型,其说明了对开关电源性能能够产生影响作用的大多数寄生元件。为了简化,只给出了低侧同步整流器MOSFET和驱动器级。与驱动器汲极和源极阻抗相关联的电阻通常都具有不同值,但制造商的数据表中都应做了指定。需要指出的是,驱动器和MOSFET间寄生电感的作用同样是十分重要的。在进行较高频率操作时,该电感将限制门电流对MOSFET输入电容充电的尝试。公式2表明这将导致更长的上升与下降时间以及额外的开关损耗。在本例中,我们假定总寄生电感LLUMP为50nH。如图6所示,LLUMP由与MOSFET和驱动器封装类型相关的内部引线电感组成。由于设计人员无法真正控制这些参数,因此唯一可以控制的寄生电感组件是线迹电感Ltrace。为此,最大程度地缩短驱动器与MOSFET之间的线迹长度以及直接在接地平面上运行短且宽的线迹,都可降低寄生线迹电感。

---控制MOSFET功率损耗计算:

Pc=Iout2×Rds(ON)×D 公式1

式中tr≈tf,可用下式近似估算:

高侧驱动器功率损耗:

---由于驱动器的汲极与源极电阻远大于MOSFET的内部门极电阻,因此大部分与MOSFET门极充电、放电相关的开关损耗来自驱动器IC。公式5

---采用公式1~公式5,可以估算出各种VGS条件下控制MOSFET与驱动器的总损耗。

---同步整流器MOSFET功率损耗计算:

---为了简化计算过程,我们假定以下基体二极管特性:

tBDR+tBDF=10ns

QRR=48nC

VF=1V

Pbd=VF×Iout×Fsw×(tBDR+tBDF) 公式6

Pc=Iout2×Rds(ON)×(1-D) 公式7

PRR=QRR×VIN×Fsw 公式8

Psw=0 公式9

Pout=0 公式10

低侧驱动器功率损耗:公式11

---采用公式6~公式11,设计人员可以估算出各VGS条件下同步整流器MOSFET与驱动器的总损耗。由于公式1~公式11所表示的单个损耗中有不少取决于频率,我们设计了EXCEL电子表格用于计算并绘制各VGS条件下,高控制MOSFET与低同步MOSFET相对应的总损耗对频率的关系曲线。您可很容易通过电子表格或MathCAD判定VGS值变化所带来的影响。

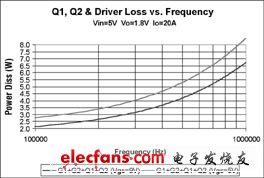

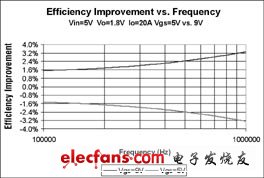

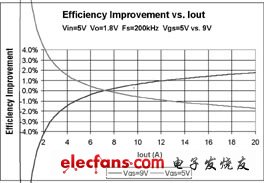

---图7所示的是公式1~公式11在不同VGS条件下频率变化(100kHz~1MHz)时所绘制的曲线图。这些图表可在任何输出负载电流下生成,图为IOUT(MAX)=20A时的输出结果,在此电流下,提高MOSFET连接点温度主要受益于高效率。显而易见,当IOUT=20A时,在所有考虑的频率范围内,VGS=9V都能显著减少耗散功率。通过计算各VGS条件下的总耗散功率,并已知最大输出功率,我们应用公式12绘制了图8中的曲线。

公式12

---在选择最优开关频率时,除了考虑对驱动器与MOSFET的影响,还必须考虑对功率级组件的影响。分析功率级频率的影响作用已经超出了本例的范围,因此我们假定200kHz对于在优化MOSFET与门极驱动电路以及维持相当的高频以使功率级中无源组件尺寸最小化二者之间来说是一个较好的折衷方案。图8中的曲线表明,在VGS=9V且IOUT=20A的条件下,频率为200kHz时,效率提高约1.7%。

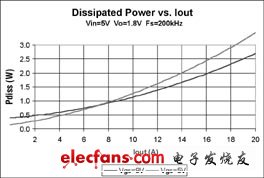

---选择200kHz的开关频率将有助于我们了解在所选频率下VGS对整个负载范围的影响。接下来,我们以200kHz为固定频率,将公式1~公式11绘制成负载电流的曲线图。

---图9所示的是在固定频率200kHz,VGS=5V与VGS=9V两种情况下,负载电流对耗散功率的影响曲线图。正如所预料的那样,图10表明了当VGS=9V且IOUT=20A时,效率提高了1.7%。然而,当IOUT小于7A时,VGS=9V使效率降低,而VGS=5V却能提高效率。这是因为,IOUT小于7A时,低导电损耗所带来的效率提高不再具有主导的作用,这点在公式1与公式7中显而易见。在低负载电流时,频率相关损耗(frequency dependant losses)开始超过电流相关(导电)损耗并起主导作用,因此,应选择低的VGS=5V,也就是低门极电荷。

---有趣的是,通过重复上述绘图过程,能够优化VGS与开关频率的组合。在本例中,如果采用VGS=9V,频率为200kHz,能够在最大输出电流时提高效率1.7%;而在较小负载电流时,代价是使效率降低。相反,如果采用VGS=5V,频率同样为200kHz,则在中低范围的负载电流时效率提高,而在高负载电流时效率降低。

---生成图7~图10中的曲线图所采用的详细计算过程如下:

---控制MOSFET,VGS=5V:

Pc(5V)=(20A)2×8.7×10-3Ω×0.36=1.253W 公式13公式14

Psw(5V)= ×5V×20A×(54.3×10-9s+54.3×10-9s)×(200×103Hz)=1.09W 公式15

Pout(5V)= × ×400×10-12F×5V×200×103Hz=0.27mW 公式16

VGS=5V时驱动器IC中的耗散功率:公式17

---高控制MOSFET与门极驱动器IC的总功率损耗为公式13~公式17的损耗之和。

---PG1_TOTAL(5V)=1.253W+1.09W+0.27×10-3W+21.1×10-3W=2.36W 公式18

---控制MOSFET,VGS=9V:

Pc(9V)=(20A)2×6.4×10-3Ω×0.36=0.922W 公式19公式20

Psw(V9)= ×5V×20A×(30×10-9s + 30×10-9s )×(200×103Hz)=0.6W 公式21

Pout(9V)= × ×400×10-12 F×5V×200×103Hz=0.27mW 公式22

VGS=9V时驱动器IC中的耗散功率:公式23

高控制MOSFET与门极驱动器IC的总功率损耗为公式19~公式23的损耗之和。

PG1_TOTAL(9V) = 0.922W + 0.6W + 0.6W +0.27×10-3W+72.46×10-3W =1.595W 公式24

同步整流器MOSFET,VGS=5V:

Pbd(5V)=1V×20A×200×103Hz×(10×10-9s)=40×10-3W 公式25

Pc(5V)=(20A)2×3.37×10-3Ω×(1-0.36)=0.863W 公式26

PRR(5V)=37.5×10-9C×5V×200×103Hz=37.5×10-3W 公式27

VGS=5V时驱动器IC中的耗散功率:公式28

---同步整流器MOSFET与门极驱动器IC的总功率损耗为公式25~公式28的损耗之和。

---PG2_TOTAL(5V)=40×10-3W + 0.863W +37.5×10-3W+72.88×10-3W =1.014W 公式29

---同步整流器MOSFET,VGS=9V:

Pbd(9V)=1V×20A×200×103Hz×(10×10-9s)=40×10-3W 公式30

Pc(9V)=(20A)2×2.75×10-3Ω×(1-0.36)=704×10-3W 公式31

PRR(9V)=76×10-9C×5V×200×103Hz=76×10-3W 公式32

VGS=9V时驱动器IC中的耗散功率:公式33

---同步整流器MOSFET与门极驱动器IC的总功率损耗为公式30~公式33的损耗之和。

PG2_TOTAL(9V)=40×10-3W+704×10-3W +76×10-3W+265.85×10-3W=1.086W

公式34

---应用实例结果小结如表2所示。

---表2表明,对于Fsw=200kHz且IOUT=20A,采用VGS=9V比采用VGS=5V驱动Q1与Q2能提高整体效率近1.7%。表2中的结果与图7~图10中的计算图形结果完全一致。在本例中,采用VGS=9V驱动Q1与Q2能显著提高整体效率,然而在IOUT低于7A时,效率有所降低。表2中Q1与Q2的总损耗似乎是合理的,然而,每个MOSFET封装的热阻抗也应该考虑在内,这样才能确保连接点温度处于额定的限制范围中。如果连接点温度未超过选定的设计限值,则可进一步提高开关频率。

结论

---使用给定的一组同步降压功率级设计参数,以9V而不是5V驱动MOSFET门极能够实现高达1.7%的满负载效率增加值。

电子发烧友App

电子发烧友App

评论