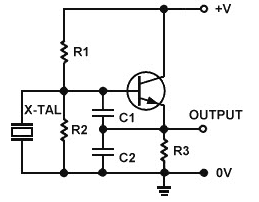

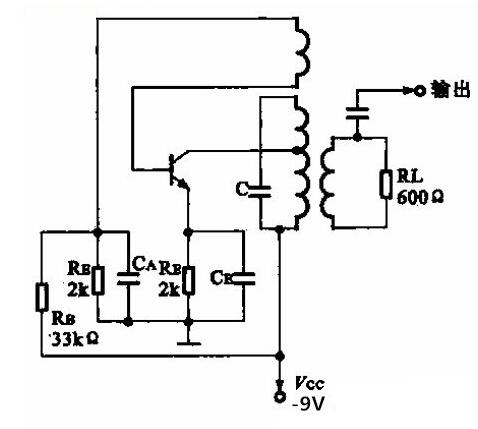

我们在观察晶体振荡电路时,通常会看到这么几个电子元器件,晶振和晶振两旁的电容。电容一端接地,一端接晶振。还有就是两个电阻,一个是跨接在晶振两端,一个接在晶振的输出端,同芯片相连。旁接的电容我们都知道叫匹配电容,它们的大小可以改变振荡电路的频率,通过试验就可以观察的到。而两个分别串并得电阻各自起到什么作用,其值选多大?

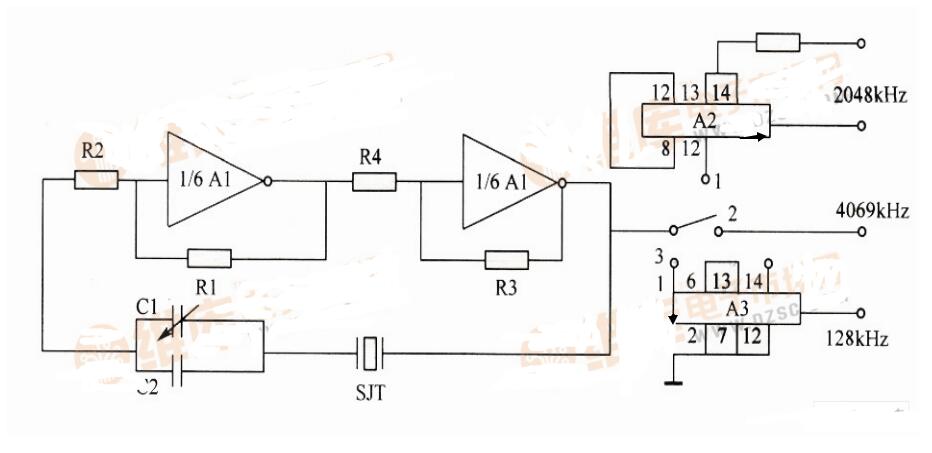

微控制器的时钟源可以分为两类:基于机械谐振器件的时钟源,如晶振、陶瓷谐振槽路;基于相移电路的时钟源,如:RC (电阻、电容)振荡器。硅振荡器通常是完全集成的RC振荡器,为了提高稳定性,包含有时钟源、匹配电阻和电容、温度补偿等。

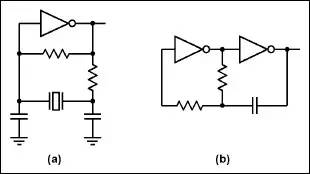

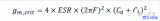

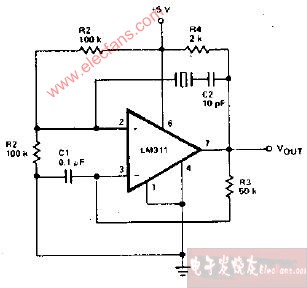

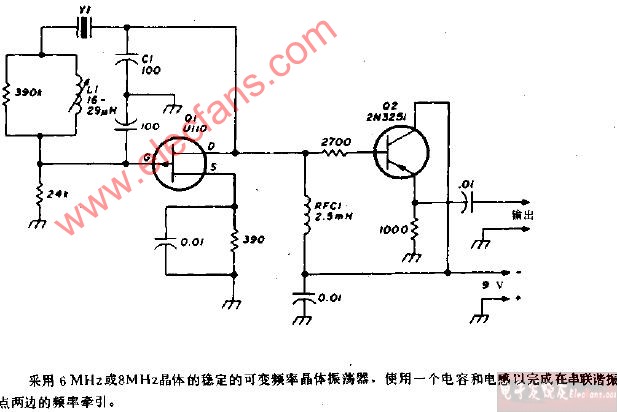

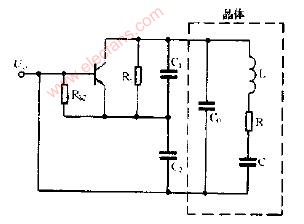

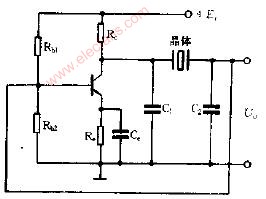

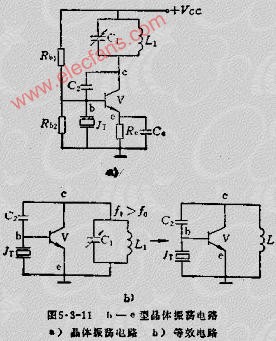

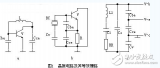

下图给出了两种时钟源。两种分立的振荡器电路,其中图a为皮尔斯振荡器配置,用于机械式谐振器件,如晶振和陶瓷谐振槽路。图b为简单的RC反馈振荡器。

举例,一个振荡电路在其输出端串接了一个22K的电阻,在其输出端和输入端之间接了一个10M的电阻。

并联电阻

电路并联电阻是由于连接晶振的芯片端内部是一个线性运算放大器,将输入进行反向180度输出,晶振处的负载电容电阻组成的网络提供另外180度的相移,整个环路的相移360度,满足振荡的相位条件,同时还要求闭环增益大于等于1,晶体才正常工作。Xin和Xout的内部一般是一个施密特反相器,反相器是不能驱动晶体震荡的。因此,在反相器的两端并联一个电阻,由电阻完成将输出的信号反向。电阻的作用是将电路内部的反向器加一个反馈回路,形成放大器,当晶体并在其中会使反馈回路的交流等效按照晶体频率谐振,由于晶体的Q值非常高,因此电阻在很大的范围变化都不会影响输出频率,但会影响脉宽比的。

晶振输入输出连接的电阻作用是产生负反馈,保证放大器工作在高增益的线性区,一般在M欧级,KHz晶振电路,并联电阻通常为10M欧,MHz晶振,并联电容通常为1M欧左右。

串联电阻

电路串联电阻常用来预防晶振被过分驱动。晶振过分驱动的后果是将逐渐损耗减少晶振的接触电镀,这将引起频率的上升,并导致晶振的早期失效,又可以讲drive level调整用。用来调整drive level和发振余裕度。

电阻Rs常用来防止晶振被过分驱动。过分驱动晶振会渐渐损耗减少晶振的接触电镀,这将引起频率的上升。可用一台示波器检测OSC输出脚,如果检测一非常清晰的正弦波,且正弦波的上限值和下限值都符合时钟输入需要,则晶振未被过分驱动;相反,如果正弦波形的波峰,波谷两端被削平,而使波形成为方形,则晶振被过分驱动。这时就需要用电阻Rs来防止晶振被过分驱动。判断电阻Rs值大小的最简单的方法就是串联一个5k或10k的微调电阻,从0开始慢慢调高,一直到正弦波不再被削平为止。通过此办法就可以找到最接近的电阻Rs值。

输出端串联电阻与负载电容组成网络,提供180度相移,同时起到限流的作用,防止反向器输出对晶振过驱动,损坏晶振。其值的大小通常为几百K 欧姆较多,具体大小需要通过调试,根据过驱程度去选定串接多大电阻。

晶振本身的作用

振荡器是一种能量转换器,石英谐振器是利用石英晶体谐振器决定工作频率,与LC谐振回路相比,它具有很高的标准性和极高的品质因数,,具有较高的频率稳定度,采用高精度和稳频措施后,石英晶体振荡器可以达到10-4~10-11稳定度。

基本性能主要是起振荡作用,可利用其对某频率具有的响应作用,用来滤波、选频网络等,石英谐振器相当于RLC振荡电路。

石英晶体俗称水晶,是一种化学成分为二氧化硅(SiO2)的六角锥形结晶体,比较坚硬。它有三个相互垂直的轴,且各向异性:纵向Z轴称为光轴,经过六棱柱棱线并垂直于Z轴的X轴称为电轴,与X轴和Z轴同时垂直的Y轴(垂直于棱面)称为机械轴

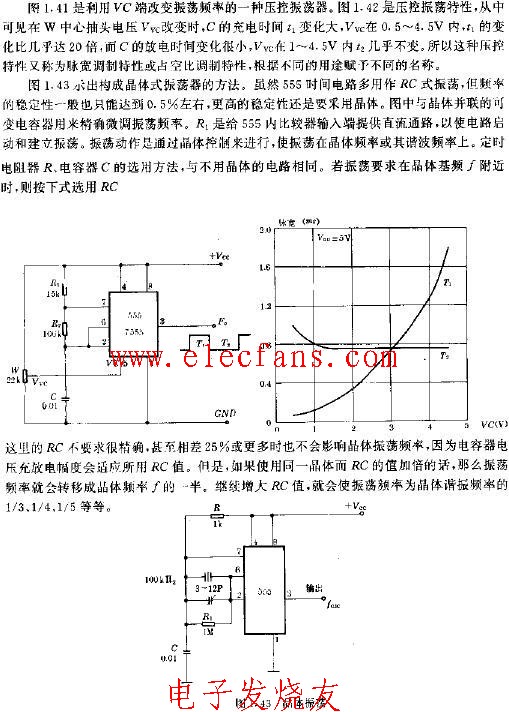

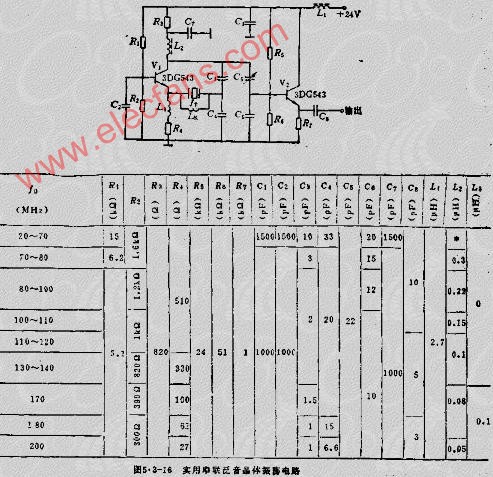

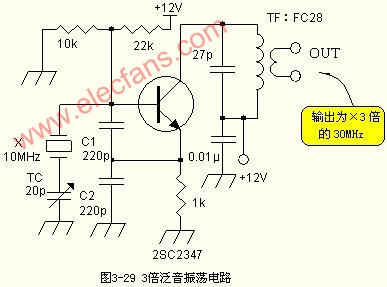

石英晶体之所以可以作为谐振器,是由于它具有正(机械能→电能)、反(电能→机械能)压电效应。沿石英晶片的电轴或机械轴施加压力,则在晶片的电轴两面三刀个表面产生正、负电荷,呈现出电压,其大小与所加力产生的形变成正比;若施加张力,则产生反向电压,这种现象称为正电效应。当沿石英晶片的电轴方向加电场,则晶片在电轴和机械轴方向将延伸或压缩,发生形变,这种现象称为反压电效应。因此,在晶体两面三刀端加上交流电压时,晶片会随电压的变化产生机械振动,机械振动又会在晶片内表面产生交变电荷。由于晶体是有弹性的固体,对于某一振动方式,有一个固有的机械谐振频率。当外加交流电压等于晶片的固有机械谐振频率时,晶片的机械振动幅度最大,流过晶片的电流最大,产生了共振现象。石英晶片的共振具有多谐性,即除可以基频共振外,还可以谐频共振,通常把利用晶片的基频共振的谐振器,利用晶片谐频共振的谐振器称为泛音谐振器,一般能利用的是3、5、7之类的奇次泛音。晶片的振动频率与厚度成反比,工作频率越高,要求晶片越薄(尺寸越大,频率越低),这样的晶片其机械强度就越差,加工越困难,而且容易振碎,因此在工作频率较高时常采用泛音晶体。一般地,在工作频率小于20MHZ时采用基频晶体,在工作频率大于20MHZ时采用泛音晶体。

原理:压电效应

若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。

晶振的作用一句话简单说就是:选择频率,让跟自己固有频率相等的和接近的振荡荡起来。

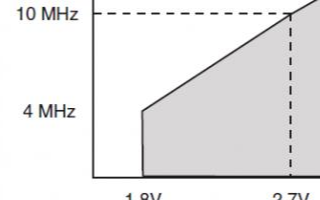

对于一个高可靠性的系统设计,晶体的选择非常重要,尤其设计带有睡眠唤醒(往往用低电压以求低功耗)的系统。这是因为低供电电压使提供给晶体的激励功率减少,造成晶体起振很慢或根本就不能起振。这一现象在上电复位时并不特别明显,原因时上电时电路有足够的扰动,很容易建立振荡。在睡眠唤醒时,电路的扰动要比上电时小得多,起振变得很不容易。在振荡回路中,晶体既不能过激励(容易振到高次谐波上)也不能欠激励(不容易起振)。晶体的选择至少必须考虑:谐振频点,负载电容,激励功率,温度特性,长期稳定性。

晶体的匹配电容

1.匹配电容-----负载电容是指晶振要正常震荡所需要的电容。一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。要求高的场合还要考虑ic输入端的对地电容。一般晶振两端所接电容是所要求的负载电容的两倍。这样并联起来就接近负载电容了。

2.负载电容是指在电路中跨接晶体两端的总的外界有效电容。他是一个测试条件,也是一个使用条件。应用时一般在给出负载电容值附近调整可以得到精确频率。此电容的大小主要影响负载谐振频率和等效负载谐振电阻。

3.一般情况下,增大负载电容会使振荡频率下降,而减小负载电容会使振荡频率升高。

4.负载电容是指晶振的两条引线连接IC块内部及外部所有有效电容之和,可看作晶振片在电路中串接电容。负载频率不同决定振荡器的振荡频率不同。标称频率相同的晶振,负载电容不一定相同。因为石英晶体振荡器有两个谐振频率,一个是串联揩振晶振的低负载电容晶 振:另一个为并联揩振晶振的高负载电容晶振。所以,标称频率相同的晶振互换时还必须要求负载电容一至,不能冒然互换,否则会造成电器工作不正常。

关于晶振

石英晶体振荡器是高精度和高稳定度的振荡器,被广泛应用于彩电、计算机、遥控器等各类振荡电路中,以及通信系统中用于频率发生器、为数据处理设备产生时钟信号和为特定系统提供基准信号。

一、石英晶体振荡器的基本原理

1、石英晶体振荡器的结构

石英晶体振荡器是利用石英晶体(二氧化硅的结晶体)的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片(简 称为晶片,它可以是正方形、矩形或圆形等),在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体 谐振器,简称为石英晶体或晶体、晶振。其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

2、压电效应

若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为 压电效应。如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。在一般情况下,晶片机械振动的振幅和交变电场的振 幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。

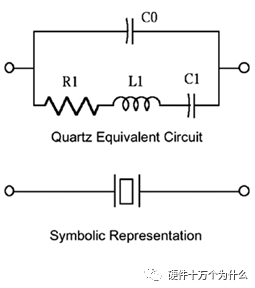

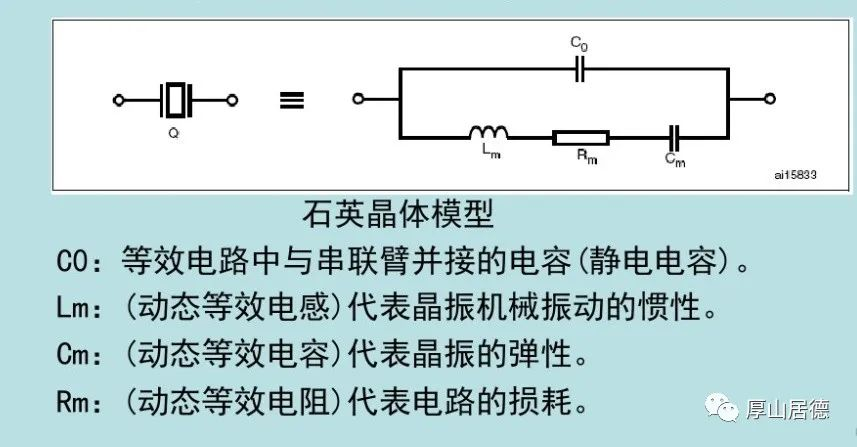

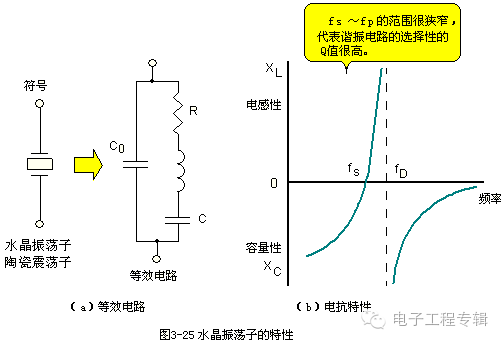

3、符号和等效电路

当晶体不振动时,可把它看成一个平板电容器称为静电电容C,它的大小与晶片的几何尺寸、电极面积有关,一般约几个PF到几十PF。当晶体振荡时,机 械振动的惯性可用电感L来等效。一般L的值为几十mH 到几百mH。晶片的弹性可用电容C来等效,C的值很小,一般只有0.0002~0.1pF。晶片振动时因摩擦而造成的损耗用R来等效,它的数值约为 100Ω。由于晶片的等效电感很大,而C很小,R也小,因此回路的品质因数Q很大,可达1000~10000。加上晶片本身的谐振频率基本上只与晶片的切 割方式、几何形状、尺寸有关,而且可以做得精确,因此利用石英谐振器组成的振荡电路可获得很高的频率稳定度。

4、谐振频率

从石英晶体谐振器的等效电路可知,它有两个谐振频率,即(1)当L、C、R支路发生串联谐振时,它的等效阻抗最小(等于R)。串联揩振频率用fs表 示,石英晶体对于串联揩振频率fs呈纯阻性,(2)当频率高于fs时L、C、R支路呈感性,可与电容C。发生并联谐振,其并联频率用fd表示。

根据石英晶体的等效电路,可定性画出它的电抗—频率特性曲线。可见当频率低于串联谐振频率fs或者频率高于并联揩振频率fd时,石英晶体呈容性。仅在fs

二、石英晶体振荡器类型特点

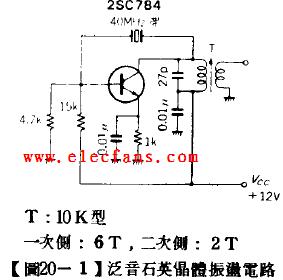

石英晶体振荡器是由品质因素极高的石英晶体振子(即谐振器和振荡电路组成。晶体的品质、切割取向、晶体振子的结构及电路形式等,共同决定振荡器的性 能。国际电工委员会(IEC)将石英晶体振荡器分为4类:普通晶体振荡(TCXO),电压控制式晶体振荡器(VCXO),温度补偿式晶体振荡 (TCXO),恒温控制式晶体振荡(OCXO)。目前发展中的还有数字补偿式晶体损振荡(DCXO)等。

普通晶体振荡器(SPXO)可产生10^(-5)~10^(-4)量级的频率精度,标准频率1—100MHZ,频率稳定度是±100ppm。SPXO没有采用任何温度频率补偿措施,价格低廉,通常用作微处理器的时钟器件。封装尺寸范围从21×14×6mm及5×3.2×1.5mm。

电压控制式晶体振荡器(VCXO)的精度是10^(-6)~10^(-5)量级,频率范围1~30MHz。低容差振荡器的频率稳定度是±50ppm。通常用于锁相环路。封装尺寸14×10×3mm。

温度补偿式晶体振荡器(TCXO)采用温度敏感器件进行温度频率补偿,频率精度达到10^(-7)~10^(-6)量级,频率范围1—60MHz, 频率稳定度为±1~±2.5ppm,封装尺寸从30×30×15mm至11.4×9.6×3.9mm。通常用于手持电话、蜂窝电话、双向无线通信设备等。

恒温控制式晶体振荡器(OCXO)将晶体和振荡电路置于恒温箱中,以消除环境温度变化对频率的影响。OCXO频率精度是10^(-10)至10^(-8)量级,对某些特殊应用甚至达到更高。频率稳定度在四种类型振荡器中最高。

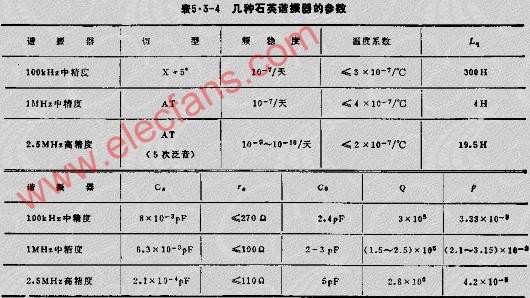

三、石英晶体振荡器的主要参数

晶振的主要参数有标称频率,负载电容、频率精度、频率稳定度等。不同的晶振标称频率不同,标称频率大都标明在晶振外壳上。如常用普通晶振标称频率 有:48kHz、500 kHz、503.5 kHz、1MHz~40.50 MHz等,对于特殊要求的晶振频率可达到1000 MHz以上,也有的没有标称频率,如CRB、ZTB、Ja等系列。负载电容是指晶振的两条引线连接IC块内部及外部所有有效电容之和,可看作晶振片在电路 中串接电容。负载频率不同决定振荡器的振荡频率不同。标称频率相同的晶振,负载电容不一定相同。因为石英晶体振荡器有两个谐振频率,一个是串联揩振晶振的 低负载电容晶振:另一个为并联揩振晶振的高负载电容晶振。所以,标称频率相同的晶振互换时还必须要求负载电容一至,不能冒然互换,否则会造成电器工作不正 常。频率精度和频率稳定度:由于普通晶振的性能基本都能达到一般电器的要求,对于高档设备还需要有一定的频率精度和频率稳定度。频率精度从10^(-4) 量级到10^(-10)量级不等。稳定度从±1到±100ppm不等。这要根据具体的设备需要而选择合适的晶振,如通信网络,无线数据传输等系统就需要更 高要求的石英晶体振荡器。因此,晶振的参数决定了晶振的品质和性能。在实际应用中要根据具体要求选择适当的晶振,因不同性能的晶振其价格不同,要求越高价 格也越贵,一般选择只要满足要求即可。

四、石英晶体振荡器的发展趋势

1、小型化、薄片化和片式化:为满足移动电话为代表的便携式产品轻、薄、短小的要求,石英晶体振荡器的封装由传统的裸金属外壳覆塑料金属向陶瓷封装 转变。例如TCXO这类器件的体积缩小了30~100倍。采用SMD封装的TCXO厚度不足2mm,目前5×3mm尺寸的器件已经上市。

2、高精度与高稳定度,目前无补偿式晶体振荡器总精度也能达到±25ppm,VCXO的频率稳定度在10~7℃范围内一般可达±20~100ppm,而OCXO在同一温度范围内频率稳定度一般为±0.0001~5ppm,VCXO控制在±25ppm以下。

3、低噪声,高频化,在GPS通信系统中是不允许频率颤抖的,相位噪声是表征振荡器频率颤抖的一个重要参数。目前OCXO主流产品的相位噪声性能有 很大改善。除VCXO外,其它类型的晶体振荡器最高输出频率不超过200MHz。例如用于GSM等移动电话的UCV4系列压控振荡器,其频率为 650~1700 MHz,电源电压2.2~3.3V,工作电流8~10mA。

4、低功能,快速启动,低电压工作,低电平驱动和低电流消耗已成为一个趋势。电源电压一般为3.3V。目前许多TCXO和VCXO产品,电流损耗不 超过2 mA。石英晶体振荡器的快速启动技术也取得突破性进展。例如日本精工生产的VG—2320SC型VCXO,在±0.1ppm规定值范围条件下,频率稳定时 间小于4ms。日本东京陶瓷公司生产的SMD TCXO,在振荡启动4ms后则可达到额定值的90%。OAK公司的10~25 MHz的OCXO产品,在预热5分钟后,则能达到±0.01 ppm的稳定度。

五、石英晶体振荡器的应用

1、石英钟走时准、耗电省、经久耐用为其最大优点。

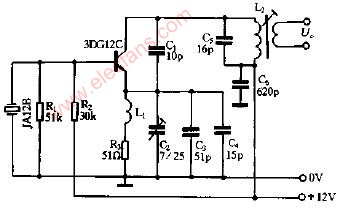

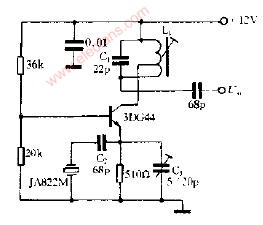

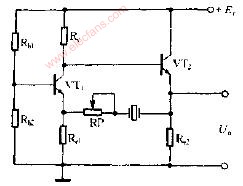

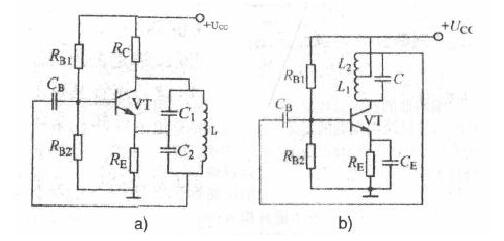

不论是老式石英钟或是新式多功能石英钟都是以石英晶体振荡器为核心电路,其频率精度决定了电子钟 表的走时精度。从石英晶体振荡器原理的示意图中,其中V1和V2构成CMOS反相器石英晶体Q与振荡电容C1及微调电容C2构成振荡系统,这里石英晶体相 当于电感。振荡系统的元件参数确定了振频率。一般Q、C1及C2均为外接元件。另外R1为反馈电阻,R2为振荡的稳定电阻,它们都集成在电路内部。故无法 通过改变C1或C2的数值来调整走时精度。但此时我们仍可用加接一只电容C有方法,来改变振荡系统参数,以调整走时精度。根据电子钟表走时的快慢,调整电 容有两种接法:若走时偏快,则可在石英晶体两端并接电容C,如图4所示。此时系统总电容加大,振荡频率变低,走时减慢。若走时偏慢,则可在晶体支路中串接 电容C。如图5所示。此时系统的总电容减小,振荡频率变高,走时增快。只要经过耐心的反复试验,就可以调整走时精度。因此,晶振可用于时钟信号发生器。

2、随着电视技术的发展,近来彩电多采用500kHz或503 kHz的晶体振荡器作为行、场电路的振荡源,经1/3的分频得到 15625Hz的行频,其稳定性和可靠性大为提高。面且晶振价格便宜,更换容易。

3、在通信系统产品中,石英晶体振荡器的价值得到了更广泛的体现,同时也得到了更快的发展。许多高性能的石英晶振主要应用于通信网络、无线数据传输、高速数字数据传输等

晶振的负载电容

晶体元件的负载电容是指在电路中跨接晶体两端的总的外界有效电容。是指晶振要正常震荡所需要的电容。一般外接电容,是为了使晶振两端的等效电容等于 或接近负载电容。要求高的场合还要考虑ic输入端的对地电容。应用时一般在给出负载电容值附近调整可以得到精确频率。此电容的大小主要影响负载谐振频率和 等效负载谐振电阻。

晶振的负载电容=[(Cd*Cg)/(Cd+Cg)]+Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上电容)。就是说负载电容15pf的话,两边个接27pf的差不多了,一般a为6.5~13.5pF

各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器。 晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联。 在晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十 M 欧之间。 很多芯片的引脚内部已经包含了这个电阻, 引脚外部就不用接了。 这个电阻是为了使反相器在振荡初始时处与线性状态, 反相器就如同一个有很大增益的放大器, 以便于起振。 石英晶体也连接在晶振引脚的输入和输出之间, 等效为一个并联谐振回路, 振荡频率应该是石英晶体的并联谐振频率。 晶体旁边的两个电容接地, 实际上就是电容三点式电路的分压电容, 接地点就是分压点。 以接地点即分压点为参考点, 振荡引脚的输入和输出是反相的, 但从并联谐振回路即石英晶体两端来看, 形成一个正反馈以保证电路持续振荡。 在芯片设计时, 这两个电容就已经形成了, 一般是两个的容量相等, 容量大小依工艺和版图而不同, 但终归是比较小, 不一定适合很宽的频率范围。 外接时大约是数 PF 到数十 PF, 依频率和石英晶体的特性而定。 需要注意的是: 这两个电容串联的值是并联在谐振回路上的, 会影响振荡频率。 当两个电容量相等时, 反馈系数是 0.5, 一般是可以满足振荡条件的, 但如果不易起振或振荡不稳定可以减小输入端对地电容量, 而增加输出端的值以提高反馈量。

设计考虑事项:

使晶振、外部电容器(如果有)与 IC之间的信号线尽可能保持最短。当非常低的电流通过IC晶振振荡器时,如果线路太长,会使它对 EMC、ESD 与串扰产生非常敏感的影响。而且长线路还会给振荡器增加寄生电容。

2.尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。

3.当心晶振和地的走线

4.将晶振外壳接地

如果实际的负载电容配置不当,第一会引起线路参考频率的误差。另外如在发射接收电路上会使晶振的振荡幅度下降(不在峰点),影响混频信号的信号强度与信噪。

当波形出现削峰,畸变时,可增加负载电阻调整(几十K到几百K)。要稳定波形是并联一个1M左右的反馈电阻。

晶振停振的可能原因及处理方法

1,在压封时,晶体内部要求抽真空充氮气,如果发生压封不良,即石英晶体的密封性不好时,在酒精加压的条件下,其表现为漏气,称之为双漏,也会导致停振,

2,由于芯片本身的厚度很薄,当激励功率过大时,会使内部石英芯片破损,导致停振;

3,在焊锡时,当锡丝透过线路板上小孔渗过,导致引脚跟外壳连接在一块,或是晶体在制造过程中,基座上引脚的锡点和外壳相连接发生单漏,都会造成短路,从而引起停振;

4,由于石英晶体在剪脚和焊锡的时候容易产生机械应力和热应力,而焊锡温度过高和作用时间太长都会影响到晶体,容易导致晶体处于临界状态,以至出现时振时不振现象,甚至停振;

5,有功负载会降低Q值(即品质因素),从而使晶体的稳定性下降,容易受周边有源组件影响,处于不稳定状态,出现时振时不振现象;

6,当石英晶体频率发生频率漂移,且超出石英晶体频率偏差范围过多时,以至于捕捉不到石英晶体的中心频率,从而导致芯片不起振。

当遇到以上情况时的正确处理方法:

1,严格按照技术要求的规定,对石英晶体组件进行检漏试验以检查其密封性,及时处理不良品并分析原因;

2,压封工序是将调好的谐振件在氮气保护中与外壳封装起来,以稳定石英晶体谐振器的电气性能。在此工序应保持送料仓、压封仓和出料仓干净,压封仓要连续冲氮气,并在压封过程中注意焊头磨损情况及模具位置,电压、气压和氮气流量是否正常,否则及时处理。其质量标准为:无伤痕、毛刺、顶坑、弯腿,压印对称不可歪斜。

3,由于石英晶体是被动组件,它是由IC提供适当的激励功率而正常工作的,因此,当激励功率过低时,晶体不易起振,过高时,便形成过激励,使石英芯片破损,引起停振。所以,应提供适当的激励功率。另外,有功负载会消耗一定的功率,从而降低晶体Q值,从而使晶体的稳定性下降,容易受周边有源组件影响,处于不稳定状态,出现时振时不振现象,所以,外加有功负载时,应匹配一个比较合适有功负载。

4,控制好剪脚和焊锡工序,并保证基座绝缘性能和引脚质量,引脚镀层光亮均匀无麻面,无变形、裂痕、变色、划伤、污迹及镀层剥落。为了更好地防止单漏,可以在晶体下加一个绝缘垫片。

5,当晶体产生频率漂移而且超出频差范围时,应检查是否匹配了合适的负载电容,可以通过调节晶体的负载电容来解决。

晶振不起振的原因及解决方法

RTC晶体经常出现不起振的问题,很多人在各种电子论坛上求助类似于“求高手指点!RTC晶振不起振怎么办”的问题,而其答案基本可以概括为“这次高手帮不了你了”

更有阴谋论者提出让人啼笑皆非的解释——STM32的RTC晶振不起振是ST与晶振厂商串通后故意搞出来的,目的是提高某晶振厂商高端晶振的销量。。。

最近做的几块板子也用到了STM32的RTC,前后两版一共做了大概6片,幸运的是并未遇到晶振不起振的现象。而我采用的是3毛钱一个的普通晶振,并未选用传说中低负载高精度晶振。。。后来在另外一片实验性质的板子上首次遇到了晶振不起振的问题,而且做了2片都不起振,这才让我意识到这个问题的严重性。

从上述现象来看,我认为对RTC晶振起振影响最大的因素应该是PCB的布线。但是遇到问题时通常是PCB已做好,甚至已经做了几百块,没有回头路了。于是大家更关注的问题似乎就是“如何补救”了。在网上搜索一下,你就会发现世界是如此美好!每个人的经验和建议都不一样,甚至是完全相反的!这种现象告诉我们,除了PCB布线,对晶振起振影响最大的似乎不是电气参数,而是另外一种不可忽略的因素——人品!

各种相互矛盾的经验也告诉我们,导致晶振不起振的原因是多种多样的,也是因“人”而异的。也许,我们无法找到一个绝对有效的经验一举解决STM32的RTC晶振这个让人头疼的问题,但我们可以从各种经验中找到一些线索,为最终摸索到适合自己这块板子的解决方案提供一些帮助和提示。

如果晶振不起振,尤其是你已经使用了传说中的爱普生6pF晶振后还是不行,也许你应该尝试对以下几个方面排列组合,找到适合你这块板子的,更容易起振的方式。

下面就罗列一下可能影响RTC晶振起振的因素

1. 晶振的品牌和负载电容

大家貌似都知道要用6pF的晶振,但我发现其实12.5pF的也可以用。大家都说KDS日本原装的好,我那个3毛钱的国产晶振貌似也没啥大问题。。。

2. 晶振外接的匹配电容

有人说6pF的晶振要配6pF的电容。但有经验公式指出这个电容的值应该是晶振本身负载电容的两倍,6pF的晶振应该配10pF的匹配电容,当然12.5pF的就应该配20pF或者22pF的电容了~电容值不匹配可能造成晶振不起振。更神奇的是,有人指出去掉外接的匹配电容会使晶振起振!这似乎没啥道理,但在我的板子上,有且仅有这个方案是可行的!!!

3. 晶振并联的反馈电阻

晶振可以并联一个高阻值的电阻,据说这样更容易起振。。。这个电阻的阻值有人说是1MΩ,有人说是5MΩ,也有人说是10MΩ,,,当然也有人说不能并联这个电阻,并联了反而不起振

4. XTALout到晶振间串联电阻

这种做法是官方的应用笔记指出的,而且给出了这个电阻的计算公式。对这个电阻的的必要性也是众说纷纭,同样存在两种矛盾的说法,即必须要有这电阻,否则不起振。还有一说不能有这个电阻,否则不起振。。。从官方的应用笔记来看,这个电阻的主要作用是保护晶振,以防晶振发热。由此看来这个这个电阻似乎并非影响晶振起振的主要因素,甚至可能让晶振更难起振。

5. 晶振的外壳是否接地

这个就不用说了吧。。。晶振的外壳是金属的,做封装时可以把那个焊盘做成机械焊盘而悬空,也可以做成电气焊盘,然后连接到GND。对这个说法同样存在争议,有人说外壳必须接地,也有人说接地后反而不起振。

6. 提高Vbat引脚的电源质量

这种说法是有一定道理的,因为RTC部分是由Vbat的来供电的。有人说Vbat引脚对电源质量要求比较高,如果纹波较大可能会影响晶振的起振。更有人说反而需要一些噪声,激励晶振产生正反馈从而顺利起振(本人对此表示呵呵)。。。但不管怎样,提高电源质量对大家都是好事~

7. 晶振周围的环境

有人指出应该仔细清洗RTC晶振周围的电路,甚至是使用环氧树脂胶将晶振密封起来。这种说法得到了一些人的支持,看来也是有相当多的事实依据。

8. 减少晶振焊接时加热的时间

有人认为长时间加热晶振进行焊接会对晶振本身带来影响,却不是彻底损坏晶振,从而使得晶振不容易起振。。。这种说法我没验证过,个人表示怀疑。。。

9. 焊接的焊锡量

这个种说法感觉就更不靠谱了,但真的有人在晶振引脚上多加了点焊锡晶振就能起振了。从原理上说,多加点焊锡确实会改变晶振和PCB间的寄生参数,但我感觉影响微乎其微。。。可能晶振已经徘徊在临界值的边缘了,这种做法才会起到一点作用。

10. 使用有源晶振

个人认为这是一劳永逸解决晶振不起振问题的不二法门!有人对STM32的RTC晶振不易起振的原因做了一个解释,即出于低功耗的考虑,STM32对晶振的驱动功率比较低,所谓“好鼓不用重锤”,一些差的晶振就需要更高的驱动功率,所以不易起振。我认为这种解释是有道理的。使用有源晶振则不存在驱动功率的问题,如果问题确实是因为驱动功率造成的,那使用有源晶振毫无疑问可以彻底解决问题。而且目前网上还没看到说有源晶振不起振的求助帖。但是有源晶振通常比较昂贵,甚至要比一颗外置的RTC芯片还要贵。至于这个问题的取舍,就要看各位看官自己的想法了。

电子发烧友App

电子发烧友App

评论