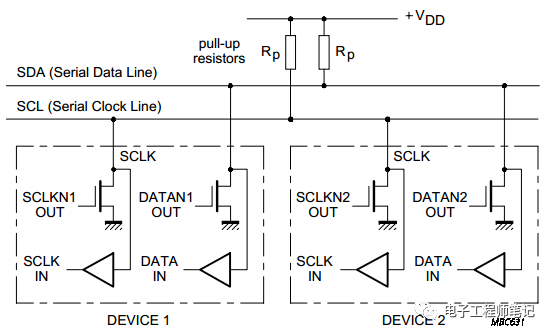

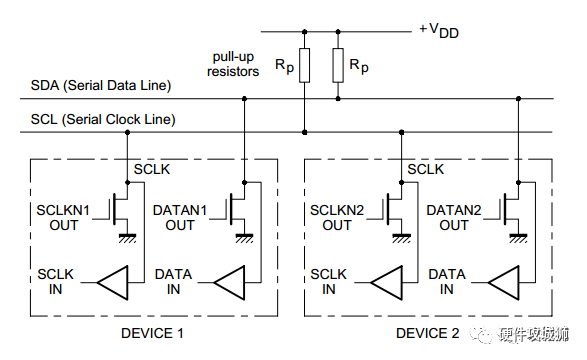

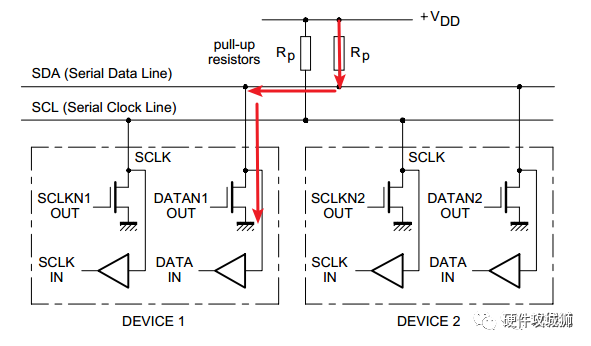

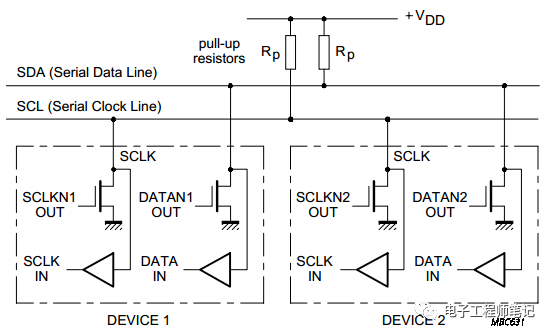

器件都有一个唯一的识别地址,而且都可以作为一个发送器或接收器。当连接在I2C总线上的多个主机器件同时传输数据时,通过仲裁来避免冲突。SDA和SCL都是双向线路,通过一个电流源或上拉电阻连接到电源。器件输出级必须是漏极开路或集电极开路,当总线空闲时,两条线路处于高电平,执行线与的功能。

2019-08-05 06:33:00

接口可编程时钟来实现传输速率的调整,同时也跟所接的上拉电阻的阻值有关。 I2C总线上的主设备与从设备之间以字节(8位)为单位进行双向的数据传输。3I2C总线协议 I2C协议规定,总线上数据的传输必须以一

2019-08-01 16:12:45

、I2C设计数学:电容和电阻了解I 2 C及其随之而来的一些设计挑战,包括逻辑阈值,影响电容的因素以及最小和最大上拉电阻。本文介绍了哪些变量会影响总线的电容。它还考察了用于确定上拉电阻器尺寸并确定电路

2020-09-22 09:31:41

流(Leakage Current)的要求上,I2C最大的漏电流为10uA,SMBus为1uA,但是1uA似乎过度严苛,使运用SMBus的装置在验证测试时耗费过多的成本与心力,因此之后

2018-11-21 19:49:16

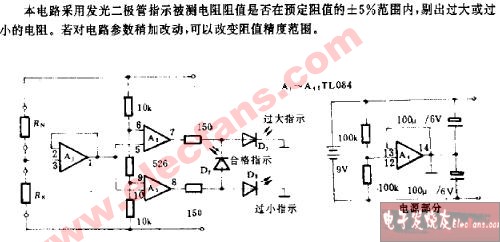

如图,像这种IIC的电路为什么要加这些4.7kΩ、100Ω的上拉电阻?

2019-02-15 09:58:53

Phiilps 公司开发的,由于它引脚少,硬件实现简单,可扩展性强,不需要 USART、CAN 等通讯协议的外部收发设备现在被广泛地使用在系统内多个集成电路(IC)间的通讯。软件I2C将芯片的两个

2021-08-23 06:22:51

I2C信号一般需要外接上拉电阻,如果主控内部有上拉电阻,是否可以省略外部上拉?这个是否需要上拉根据什么来决定?是根据从器件的输入电流来决定的吗?芯片的输入电流参数(Ii 即input current)怎么理解,设计电路时针对这个参数需要注意什么?

2018-06-07 10:01:00

。I2C的两根线SDA(串行数据线)和SCL(串行时钟线)都是双向I/O线,接口电路为开漏输出,需通过上拉电阻

2022-01-20 08:04:17

上周翻了下AT24CM02芯片的数据手册,里面提到了I2C上拉电阻的设计要点,只有两个公式就简洁地把上拉电阻阻值范围确定了,非常实用,详细见图1。实际上,以前我从来没有注意过I2C上拉电阻设计,总是

2022-11-29 08:00:00

SDA,另外一根时钟线SCL,接上拉电阻,总线空闲为高电平。只要有低电平,总线就会被拉低电平。主机通过I2C总线来传输数据给挂载的器件。通过总线仲裁,来判断哪一台主机来控制。SCL...

2022-01-18 07:36:05

定居下来。实际上,这些缩写是指系统管理总线,它与I 2 C总线不同,尽管几乎相同。最初的I 2 C协议是由Phillips Semiconductor开发的,几年后,英特尔将SMBus协议定义为I2C

2020-09-06 10:16:10

在硬件上,I2C 总线是由时钟总线 SCL 和数据总线 SDA 两条线构成,连接到总线上的所有器件的 SCL 都连到一起,所有 SDA 都连到一起。I2C 总线是开漏引脚并联的结构,因此我们外部要

2022-01-07 06:03:45

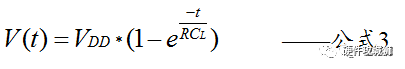

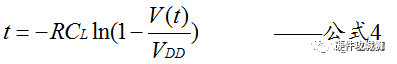

慢于从高到低的过渡,从而产生经典的I2C“锯齿”波形:这两个示波器捕获显示了具有1kΩ上拉电阻和最小电容(总线上只有两个器件,且PCB走线短)的I2C时钟信号的从低到高和从高到低的跳变。上拉电阻的尺寸

2020-09-20 08:37:42

的外部收发设备,现在被广泛地使用在系统内多个集成电路(IC)间的通讯。I2C是半双工通信I2C只有两根双向通信线: 一根是时钟线SCL, 一根是数据线SDAI2C总线通过上拉电阻接电源,当总线空闲的时候,两根线均为高电平。各器件之间的SCL与SDA 都是 “线与” 关系二、I2C的时序1、数

2021-08-20 06:58:20

................................................................... 3016.1 标准模式I2C 总线器件电阻Rp 和RS 的最大和最小值

2009-04-09 18:34:35

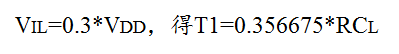

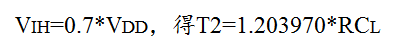

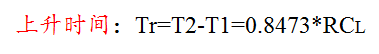

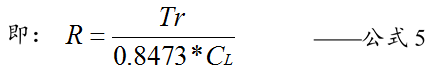

解决RPullUp,它变成:这是用于计算最大上拉电阻的最终形式。数据表中给出了t 上升时间,V 逻辑低和V 逻辑高,并且C Bus是根据电路的特性估算的。选择t 上升时间 = 150 ns,V 逻辑低 = 0.5

2020-09-21 09:00:00

我的I2C通信需要被拉到3.3V,但是我不知道我应该使用什么尺寸的上拉电阻。我读过的其他论坛的帖子,建议2.7k欧姆或4.7K欧姆,但这似乎只是让高可以在3.3V和是在3.0V低。这是正常的吗?我用

2019-04-03 15:13:49

一 、I2C物理层I2C 通讯设备之间的常用连接方式见图:有以下特点:(参考数据手册:上拉电阻一般4.7k~10k ,一般4.7k)(1)由两条总线控制:一条双向串行数据线(SDA) ,一条串行

2021-08-03 07:43:57

是FPGA生成的数据信号在约束.ucf文件中,无论我将sda位设置为i2c还是上拉它,都没有变化。在硬件设备中,i2c总线直接连接到FPGA的引脚。根据传感器数据表,SDATA通过1.5kΩ电阻上拉至VDD

2019-07-01 09:15:23

................................................................... 3016.1 标准模式I2C 总线器件电阻Rp 和RS 的最大和最小值

2008-08-13 17:16:42

的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。7、 长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹匹配,有效的抑制反射波干扰。上拉电阻阻值的选择原则包括:1、 从节约功耗及芯片

2017-08-28 09:27:18

的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。7、 长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹匹配,有效的抑制反射波干扰。上拉电阻阻值的选择原则包括:1、 从节约功耗及芯片

2017-11-16 17:14:38

下拉电阻是电阻匹配,有效的抑制反射波干扰。上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。3、对于高速

2011-09-19 08:55:51

下拉电阻是电阻匹配,有效的抑制反射波干扰。上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。3、对于高速

2008-05-22 08:46:35

要注意上拉电阻的阻值太大的时候,容易产生干扰,尤其是线路板的线条很长的时候,这种干扰更严重,这种情况下上拉电阻不宜过大,一般要小于100K,有时候甚至小于10K。 5、关于I2C的上拉电阻:因为I2C

2018-10-19 16:30:19

。 7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。 上拉电阻阻值的选择原则包括: 1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。 2

2019-06-27 05:55:08

上拉电阻有什么作用?如何去计算上拉电阻的阻值?51型单片机IO口有什么特点?AVR单片机IO口的输入状态有哪几种?

2021-07-07 07:29:25

,考虑到这个项目是带模拟电视芯片的,以前就出现过模拟电视芯片的I2C地址没有去配,导致出现漏电情况,遂立马去看是不是这个问题,结果是遗憾的,配了!那再仔细检查了基带的GPIO口和其他的I2C,发现都配

2011-12-15 18:34:39

引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。(二)上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。2、从确保足够的驱动电流考虑应当足够

2014-05-12 08:24:37

开发板I2C连接到RTC(RX8010)芯片,I2C总线上没有接上拉电阻,LS1012A手册上说它的I2C是open drain输出的,为什么没有上拉电阻? 哪位能帮助解释一下,谢谢

2022-01-05 06:28:48

电阻选择大又会带来信号上升沿的延时,因为负载的输入电容在上升沿是通过无源的上拉电阻充电,电阻越大上升时间越长,下降沿是通过有源晶体管放电,时间取决于器件本身。因此设计者在选择上拉电阻值时,要根据系统

2014-11-17 10:24:15

波干扰。 8、在数字电路中不用的输入脚都要接固定电平,通过1k电阻接高电平或接地。 四、上拉电阻阻值选择原则 1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。 2、从确保足够

2020-12-14 17:21:30

! -------一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似与一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻成为上C拉电阻

2018-06-28 06:21:54

ADXL313加速度传感器用I²C通信协议与外部连接时,上拉电阻的阻值如何确定呢?看数据手册里要参考《UM10204 I²C总线规范和用户手册》,修订版2007年6月03-19日。但是没有找到这个手册,请问可以提供一下吗?

2023-12-27 08:16:53

AVR微控制器的I/O口是双向口。具有如下的特点:AVR IO具备多种IO模式:1 高阻态,多用于高阻模拟信号输入,例如ADC数模转换器输入,模拟比较器输入2 弱上拉状态(Rup=20K~50K

2011-11-15 14:10:42

IO内置上拉电阻的阻值是多少?所有IO都有内置上拉电阻么,阻值是否一样?

2024-02-21 06:17:58

亲爱的大家, 我在我的电路板上使用LSM330DLC陀螺仪,我忘记了SPI / I2C选择引脚上的上拉电阻。但它工作正常。我的问题是我可以在没有这些上拉电阻的情况下开发我的项目吗?在数据表中提

2019-05-16 13:50:24

LTC4311 I2C逻辑缓冲器的典型低压应用电路。利用LTC4311低压I2C / SMBus加速器,利用低功耗总线加速器提高I2C或SMBU数据速率并降低功耗,LTC4311的强上拉电流允许用户选择更大的总线上拉电阻值以降低VOL

2019-06-05 09:06:39

,上拉电阻器的值为4.7kΩ,不过这个值的范围可以在少于1kΩ到10kΩ之间,取决于所使用的从器件。要获得正确的上拉电阻值,请参考器件数据表。多个从器件可以共用一条I2C总线,单个上拉电阻器I2C软件

2018-08-30 15:39:15

正常,I2C寄存器配置如下:IAM有点丢失。我已经尝试了其他上拉值(1K2,10K,12K)。任何线索!谢谢!! 以上来自于百度翻译 以下为原文 regards, Iam trying

2019-05-14 11:56:35

100PF到底就可以正常工作。如果不接电容,需要接一个100K上拉电阻也可以正常工作,请问一下,大神,这是什么原因呢???????

2018-09-26 17:03:56

我已经使用 cube-mx 生成了 I2C 代码。我的从属设备是基于 I2C 的 DIGI-POT。当我检查 HAL_I2C_IsDeviceReady() 函数时 - 它总是出现忙标志。以下是我

2023-01-30 07:39:13

最近在用stm32f401re做一款热成像设备需要用到I2C,这里总结一下遇到的坑。一开始调试我用的是开发板飞线接传感器,SCL SDA加4.7k上拉电阻。使用硬件I2C时读写大量数据时经常会遇到

2020-03-05 19:02:15

查找从机。因为I2C 通信IO口输出结构都是配置为漏极开路或集电极开路输出。所以时钟线和数据线必须外部都接上拉电阻,当一对多输出的时候,很多GPIO口会连接在同一根线上,可能会存在某个GPIO输出高电平

2021-09-07 14:22:56

。6、提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。上拉电阻阻值的选择原则 从灌电流的能力

2018-03-06 14:49:03

上拉下拉电阻的定义以及用法为什么要使用拉电阻上拉电阻阻值的选择原则

2021-04-06 06:06:42

CMOS 输入端接上或下拉电阻是为了预设缺省电位。当你不用这些引脚的时候,这些输入端下拉接 0 或上拉接 1。在I2C总线等总线上,空闲时的状态是由上下拉电阻获得。

6. 提高芯片输入信号的噪声容限

2023-05-18 17:30:56

它输出高电平时,它就断路,什么也不输出,由外接电平决定这个引脚的电平)。如果芯片内部带有上拉电阻(比如BBB的芯片就自带上拉电阻),那不外接上拉也可以。BBB系统自带了一个Linux下的I2C工具

2014-10-22 13:52:44

git上拉取的最新rtthread想着用不到每秒1000次的系统tick,改为100次以后,sht41,bmp180读取都不正确了,改回来就ok。难道是底层软件方式实现的i2c对os tick产生

2023-03-07 13:45:56

I2C分为哪几种模式?I2C的上拉电阻取值是什么?上拉电阻的上限如何确定呢?关于I2C有什么问题吗?那么一般如何解决呢?

2021-06-27 06:59:35

一概而论的。但是可能存在一种情况,比如I2C的上拉电阻,他的选取范围是比较宽的。(不考虑功耗的条件下)作者回复:功耗与速度及初试化需求,一个热情大哥的总结.

2015-10-19 18:06:17

我在设计中使用LSM6DS3组件。我过去曾经使用过这个组件(并且总是喜欢它),但从来没有使用过这个组件。我正在使用I2C与10k上拉电阻进行通信,并且使用与我的微控制器相比的独立电源总线来打开/关闭

2019-03-07 15:42:24

单片机 I2C 时序介绍在硬件上,I2C 总线是由时钟总线 SCL 和数据总线 SDA 两条线构成,连接到总线上的所有器件的 SCL 都连到一起,所有 SDA 都连到一起。I2C 总线是开漏引脚并联

2022-01-07 06:19:47

能力,使得输入信号能够更稳定地传输。

综上所述,上拉电阻在单片机电路中具有限制电流、提供上拉电压、调节电路阻抗和提供驱动能力等作用。根据具体电路需求选择合适的上拉电阻可以有效提高电路的性能和稳定性。

2023-09-05 16:45:53

12mA 电流可根据 HID Over I2C 标准进行软件复位内部上拉电阻器可简化实施过程且无需使用外部组件

2018-07-23 07:02:22

拉下拉。电阻在电路上拉或者下拉,常见于单片机的IO端口,以及MOS的驱动输出或者I2C这样的信号上,有人选择1K,有人选择10K,有人选择100K,那么我们在电路设计中,到底选择多大的电阻比较合适呢

2022-01-14 07:17:24

,一个当从机,由于适配器内部I2C总线上没上拉电阻,所以需要在SDA和SCL两根信号线上分别接一个4.7K的上拉电阻到3.3V,然后运行USB-I2C Classic软件,由于我们要配置适配器工作在从

2019-02-18 10:49:50

刹车电阻需要选择合适的功率和阻值。首先从能量转换和守恒的角度来考虑刹车电阻的选型。我们的设备总体质量约600kg,分摊到每个小车约200kg,每个小车有2个驱动器,分摊到驱动器上的质量约100kg

2021-09-02 07:25:41

I2C上拉电阻 在一些PCB的layout中,大家往往会看到在I2C通信的接口处,往往会接入一个4.7K的电阻,有的datasheet上面明确有要求,需要接入,有的则没有要求。 I2C接口 对于

2022-01-14 07:22:21

CYSTART();I2CysCLSSEDRIVEVMODED(I2CYSCLIL DMYRESIUP);/ /使用内部上拉I2C电阻器I2CysSDAsStudioDrimeMod(I2CsSdAydMyRESIUP);因此,问题是如何在4100系列中做到

2019-10-08 07:43:07

1:仅仅一根线路就可能发生短路(左),一个上拉电阻就可以防止输入管脚悬空,同时防止不必要短路现象的发生那么我们怎样选择合适的电阻呢?正如大多数工程的问题一样,答案取决于你的应用。首先我们以极端条件0

2018-11-30 09:12:02

,上拉电阻器的值为4.7kΩ,不过这个值的范围可以在少于1kΩ到10kΩ之间,取决于所使用的从器件。要获得正确的上拉电阻值,请参考器件数据表。多个从器件可以共用一条I2C总线,单个上拉电阻器I2C软件

2018-06-04 10:43:02

向来实现这一点:如果我们将管脚配置成输入,那么实际上在管脚输出上会出现高电平的输出,因为我们有定义为上拉电阻器的上拉电阻。根据I2c规范,如果我们想把引脚设置为低输出,我们可以把引脚设置为输出,写0,这是

2019-07-26 14:29:14

大家好,我们用i2c来加速这个配置:*分开VDD和VDDIO(这个连接到CS)。* SDA和SCL安装有10K的外部上拉电阻。* SDO / SA0未连接(应该有内部上拉)。是否有任何上电顺序以确保

2019-03-04 11:37:27

效的抑制反射波干扰。5、预设空间状态/默认电位在一些CMOS输入端接上拉或下拉电阻是为了预设默认电位。当不用这些引脚时,这些输入端下拉接低电平或上拉接高电平。在I2C等总线上空闲时的状态是由上下拉电阻

2019-10-11 08:30:00

使用STM32的GPIO模拟I2C总线时序,GPIO设置为开漏模式,SDA和SCK外部必须使用上拉电阻,一般是4.7K。开漏模式的好处是,可以同时读取输入电平,而无需切换输入/输出模式。注意事项:在

2022-02-22 06:48:21

上拉电阻和下拉电阻上下拉电阻的出发点在正常工作或单一故障状态下,管脚均不应出现不定状态从功耗角度考虑,在长时间的管脚等待状态下,管脚端口的电阻不应消耗太多电流上下拉的选择从抗扰角度出发,信号端口优选

2022-01-14 07:42:58

。图1:刚刚运行导线可以实现短路(左)。上拉电阻可防止浮动输入,同时防止不必要的短路(右)。(来源:作者)那么我们如何选择合适尺寸的电阻呢?与大多数优秀的工程问题一样,答案取决于您的应用。让我们首先

2018-11-09 09:14:56

处于稳定状态,具体视设计要求而定!一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似于一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻

2021-08-12 13:35:38

会产生浪涌,特别是火车上的车载电视啊等,电源上要加一些保护装置,如RClamp0504F 等能将电压嵌位10、一般RST,CLK 管脚接上拉电阻选择上拉电阻阻值的原则包括:1、从节约功耗及芯片的灌电流

2014-08-21 09:56:08

的抑制反射波干扰。上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。3、对于高速电路,过大的上拉电阻

2011-06-02 16:03:48

的抑制反射波干扰。上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。3、对于高速电路,过大的上拉电阻可能

2012-06-10 21:25:15

一个上拉电阻接到正电源,因此在不使用的时候扔保持高电平。使用 I2C 总线进行通信的设备驱动这两根线变为低电平,在不使用的时候就让它们保持高电平。每个连到 I2C 的设备都有一个唯一地址,这个设备可以

2018-11-30 11:50:53

使用的从器件。要获得正确的上拉电阻值,请参考器件数据表。多个从器件可以共用一条I2C总线,单个上拉电阻器 I2C软件协议 不论何种应用,每个支持I2C器件都需要遵守针对全部I2C器件所定义的共同

2020-12-14 14:17:25

电路设计的上拉/下拉电阻阻值应该怎样选?随便弄一个,如4.k、10k的成吗?

2023-10-28 07:37:23

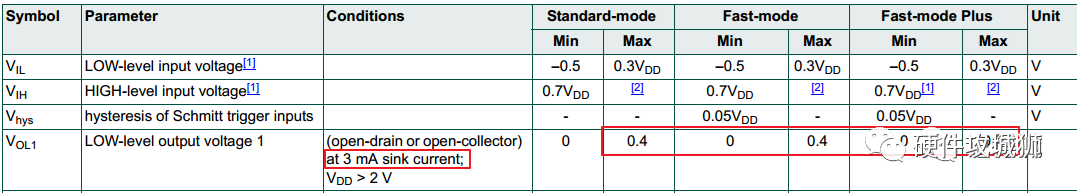

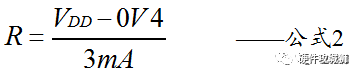

确定上拉电阻值时需要考虑哪些注意事项?稳定可靠的I2C通信的设计计算公式

2021-05-25 06:35:11

。但是,I2C总线拓扑要依赖于阻值合适的上拉电阻才能实现稳定可靠的通信。电阻值选择错误不仅会造成电能浪费,还可能导致总线状态和传输过程由于噪声、温度变化、工作电压变化以及器件间的制造差异而出

2012-12-17 11:52:52

对于I2C总线,拉出电阻值是多少?

2020-12-15 06:24:49

请问用TMS320C5515的GPIO口模拟I2C是否需要加上拉电阻?

2018-07-31 07:48:20

换个说法,如何将28335的GPIO设置成开漏输出呢?之前使用硬件I2C接口,工作正常,但是因为I2C外设管脚和另外一个外设管脚重复了,只能将I2C接口转移到其它GPIO上,使用软件模拟。使用软件

2018-10-08 17:10:19

stm32f051的i2c需要外接上拉电阻吗,直接用内部上拉行不行,还有库中的I2C_Init函数中有这么一句/* Enable I2Cx Peripheral */I2Cx->CR1 |= I2C_CR1_PE;为什么初始化有些i2c寄存器需要使能i2c。最后附上波形,希望哪位大哥帮帮忙,看看是什么问题。

2019-03-12 07:14:31

请问为什么有时在I2C中将SDA和SCL 上加各加个上拉电阻呢?

2023-05-08 18:01:37

请问用TMS320C5515的GPIO口模拟I2C总线需要接外部上拉电阻吗?需要的话阻值为多少比较合适呢?

2019-10-28 09:37:43

1.I2C总线简介I2C(Inter-Integrated Circuit ,内部集成电路)总线是一种由飞利浦Philip公司开发的串行总线。是两条串行的总线,它由一根数据线(SDA)和一根 时钟线

2016-07-06 09:52:35

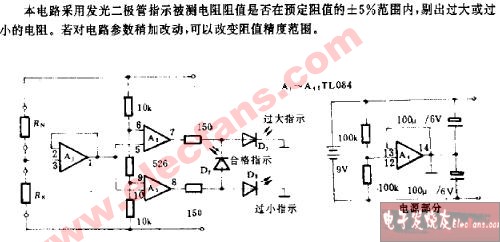

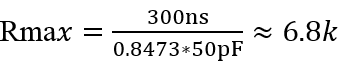

电阻阻值选择电路

2009-02-06 11:53:40 707

707

I2C总线是微电子通信控制领域中常用的一种总线标准,具备接线少,控制简单,速率高等优点。在I2C电路中常见的上拉电阻有1k、1.5k、2.2k、4.7k、5.1k、10k等等,但是应该如何根据开发要求选择合适的阻值呢?下图为I2C内部结构

2023-05-10 16:17:05 2646

2646

电子发烧友App

电子发烧友App

评论