在使用MOS管设计开关电源或者马达驱动电路的时候,大部分人都会考虑MOS的导通电阻,最大电压等,最大电流等,也有很多人仅仅考虑这些因素。这样的电路也许是可以工作的,但并不是优秀的,作为正式的产品设计也是不允许的。

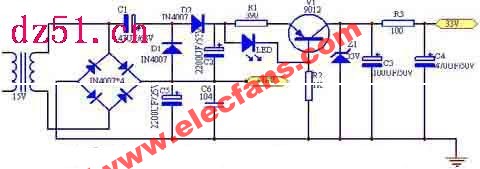

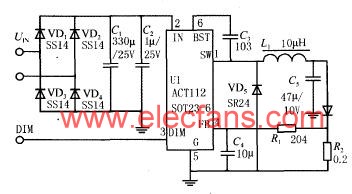

在设计便携式设备和无线产品时,提高产品性能、延长电池工作时间是设计人员需要面对的两个问题。DC-DC转换器具有效率高、输出电流大、静态电流小等优点,非常适用于为便携式设备供电。目前DC-DC转换器设计技术发展主要趋势有:

(1)高频化技术:随着开关频率的提高,开关变换器的体积也随之减小,功率密度也得到大幅提升,动态响应得到改善。小功率DC-DC转换器的开关频率将上升到兆赫级。

(2)低输出电压技术:随着半导体制造技术的不断发展,微处理器和便携式电子设备的工作电压越来越低,这就要求未来的DC-DC变换器能够提供低输出电压以适应微处理器和便携式电子设备的要求。

这些技术的发展对电源芯片电路的设计提出了更高的要求。首先,随着开关频率的不断提高,对于开关元件的性能提出了很高的要求,同时必须具有相应的开关元件驱动电路以保证开关元件在高达兆赫级的开关频率下正常工作。其次,对于电池供电的便携式电子设备来说,电路的工作电压低(以锂电池为例,工作电压2.5~3.6V),因此,电源芯片的工作电压较低。

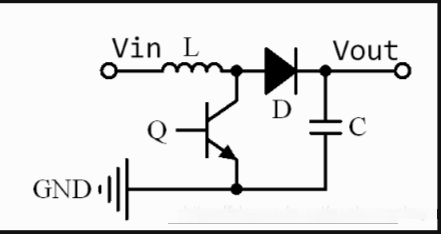

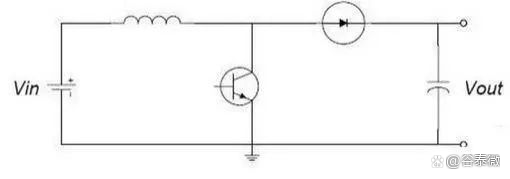

MOS管具有很低的导通电阻,消耗能量较低,在目前流行的高效DC-DC芯片中多采用MOS管作为功率开关。但是由于MOS管的寄生电容大,一般情况下NMOS开关管的栅极电容高达几十皮法。这对于设计高工作频率DC-DC转换器开关管驱动电路的设计提出了更高的要求。

在低电压ULSI设计中有多种CMOS、BiCMOS采用自举升压结构的逻辑电路和作为大容性负载的驱动电路。这些电路能够在低于1V电压供电条件下正常工作,并且能够在负载电容1~2pF的条件下工作频率能够达到几十兆甚至上百兆赫兹。本文正是采用了自举升压电路,设计了一种具有大负载电容驱动能力的,适合于低电压、高开关频率升压型DC-DC转换器的驱动电路。电路基于Samsung AHP615 BiCMOS工艺设计并经过Hspice仿真验证,在供电电压1.5V ,负载电容为60pF时,工作频率能够达到5MHz以上。

自举升压电路

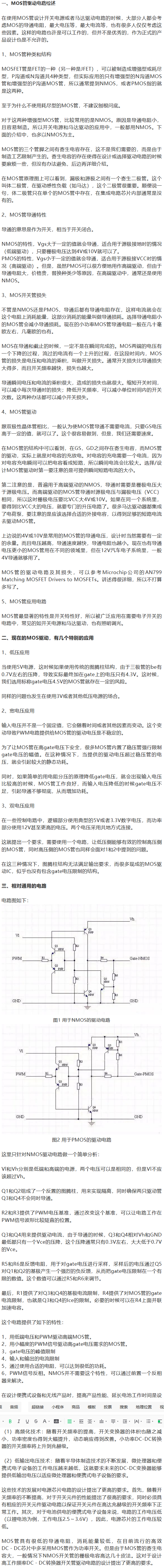

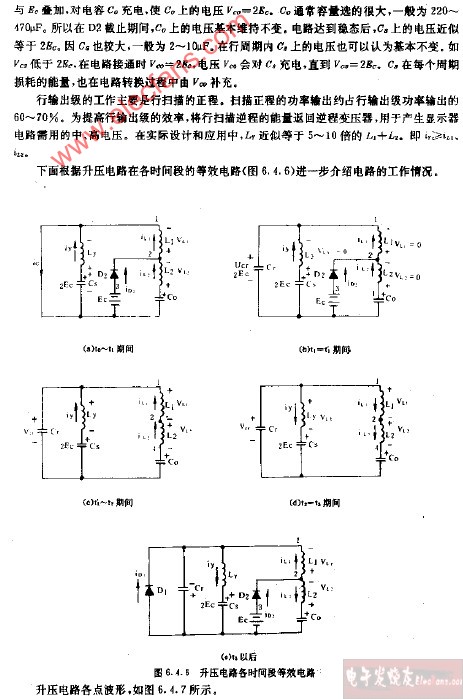

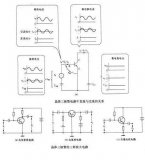

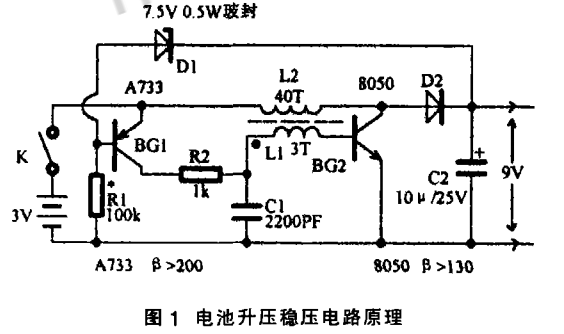

自举升压电路的原理图如图1所示。所谓的自举升压原理就是,在输入端IN输入一个方波信号,利用电容Cboot将A点电压抬升至高于VDD的电平,这样就可以在B端输出一个与输入信号反相,且高电平高于VDD的方波信号。具体工作原理如下。

当VIN为高电平时,NMOS管N1导通,PMOS管P1截止,C点电位为低电平。同时N2导通,P2的栅极电位为低电平,则P2导通。这就使得此时A点电位约为VDD,电容Cboot两端电压UC≈VDD。由于N3导通,P4截止,所以B点的电位为低电平。这段时间称为预充电周期。

当VIN变为低电平时,NMOS管N1截止,PMOS管P1导通,C点电位为高电平,约为VDD。同时N2、N3截止,P3导通。这使得P2的栅极电位升高,P2截止。此时A点电位等于C点电位加上电容Cboot两端电压,约为2VDD。而且P4导通,因此B点输出高电平,且高于VDD。这段时间称为自举升压周期。

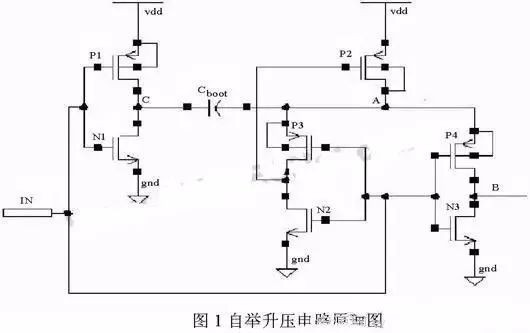

实际上,B点电位与负载电容和电容Cboot的大小有关,可以根据设计需要调整。具体关系将在介绍电路具体设计时详细讨论。在图2中给出了输入端IN电位与A、B两点电位关系的示意图。

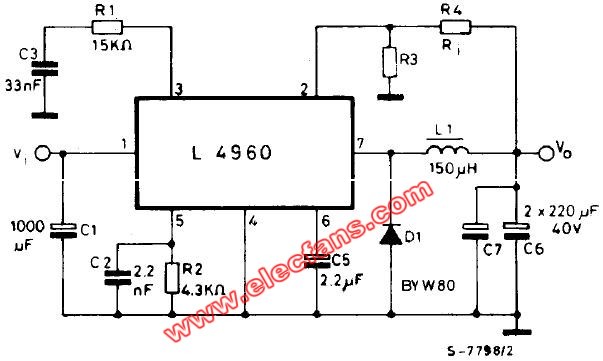

驱动电路结构

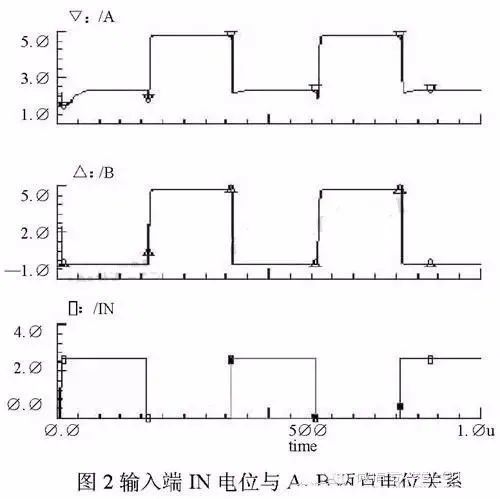

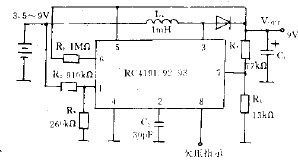

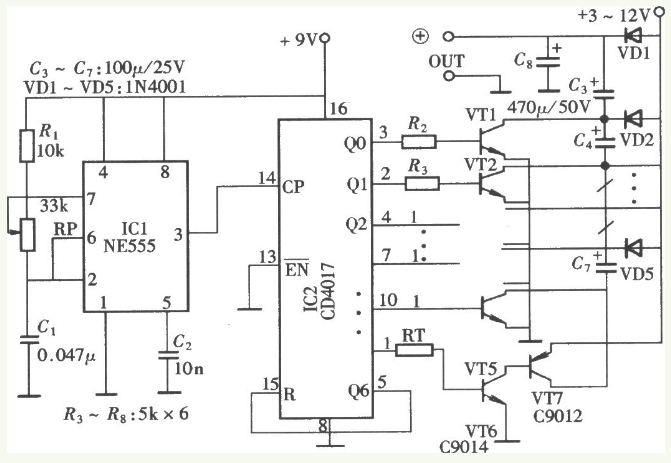

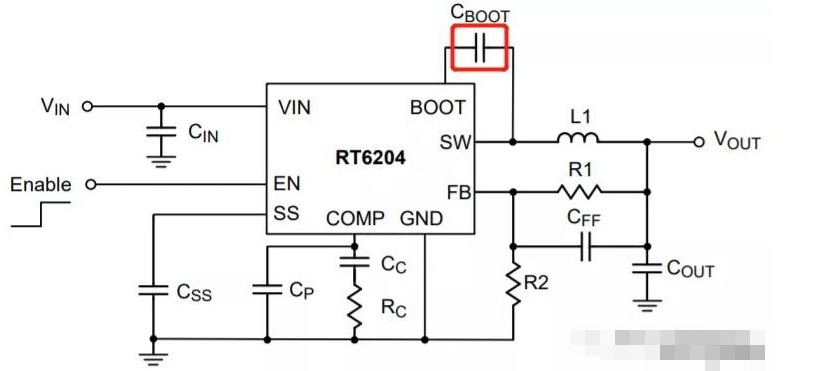

图3中给出了驱动电路的电路图。驱动电路采用Totem输出结构设计,上拉驱动管为NMOS管N4、晶体管Q1和PMOS管P5。下拉驱动管为NMOS管N5。图中CL为负载电容,Cpar为B点的寄生电容。虚线框内的电路为自举升压电路。

本驱动电路的设计思想是,利用自举升压结构将上拉驱动管N4的栅极(B点)电位抬升,使得UB>VDD+VTH ,则NMOS管N4工作在线性区,使得VDSN4 大大减小,最终可以实现驱动输出高电平达到VDD。而在输出低电平时,下拉驱动管本身就工作在线性区,可以保证输出低电平位GND。因此无需增加自举电路也能达到设计要求。

考虑到此驱动电路应用于升压型DC-DC转换器的开关管驱动,负载电容CL很大,一般能达到几十皮法,还需要进一步增加输出电流能力,因此增加了晶体管Q1作为上拉驱动管。这样在输入端由高电平变为低电平时,Q1导通,由N4、Q1同时提供电流,OUT端电位迅速上升,当OUT端电位上升到VDD-VBE时,Q1截止,N4继续提供电流对负载电容充电,直到OUT端电压达到VDD。

在OUT端为高电平期间,A点电位会由于电容Cboot 上的电荷泄漏等原因而下降。这会使得B点电位下降,N4的导通性下降。同时由于同样的原因,OUT端电位也会有所下降,使输出高电平不能保持在VDD。为了防止这种现象的出现,又增加了PMOS管P5作为上拉驱动管,用来补充OUT端CL的泄漏电荷,维持OUT端在整个导通周期内为高电平。

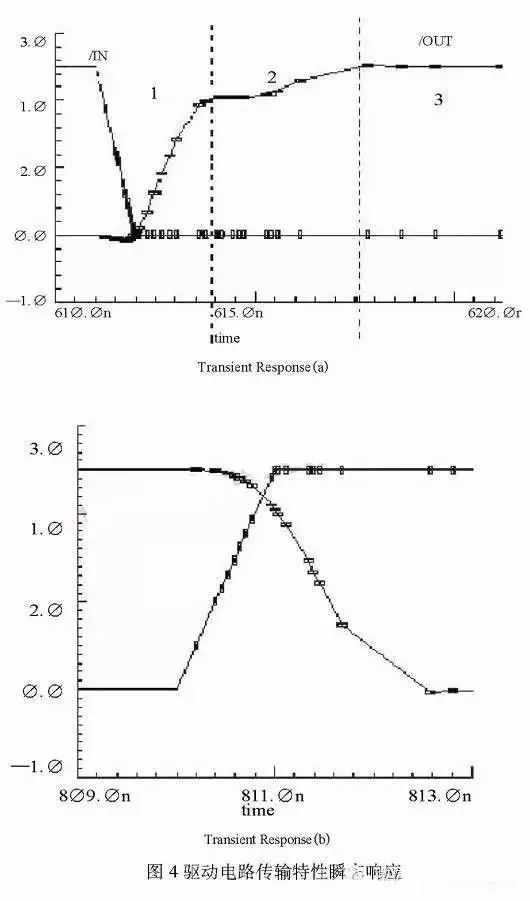

驱动电路的传输特性瞬态响应在图4中给出。其中(a)为上升沿瞬态响应,(b)为下降沿瞬态响应。从图4中可以看出,驱动电路上升沿明显分为了三个部分,分别对应三个上拉驱动管起主导作用的时期。1阶段为Q1、N4共同作用,输出电压迅速抬升,2阶段为N4起主导作,使输出电平达到VDD,3阶段为P5起主导作用,维持输出高电平为VDD。而且还可以缩短上升时间,下降时间满足工作频率在兆赫兹级以上的要求。

需要注意的问题及仿真结果

电容Cboot的大小的确定

Cboot的最小值可以按照以下方法确定。在预充电周期内,电容Cboot 上的电荷为VDDCboot。在A点的寄生电容(计为CA)上的电荷为VDDCA。因此在预充电周期内,A点的总电荷为

Q_{A1}=V_{DD}C_{boot}+V_{DD}C_{A} (1)

B点电位为GND,因此在B点的寄生电容Cpar上的电荷为0。

在自举升压周期,为了使OUT端电压达到VDD,B点电位最低为VB=VDD+Vthn。因此在B点的寄生电容Cpar上的电荷为

Q_{B}=(V_{DD}+V_{thn})Cpar (2)

忽略MOS管P4源漏两端压降,此时Cboot上的电荷为VthnCboot ,A点寄生电容CA的电荷为(VDD+Vthn)CA。A点的总电荷为

QA2=V_{thn}C_{BOOT}+(V_{DD}+V_{thn})C_{A} (3)

同时根据电荷守恒又有

Q_{B}=Q_{A}-Q_{A2} (4)

综合式(1)~(4)可得

C_{boot}=frac{V_{DD}+V_{thn}}{v_{DD}-v_{thn}}Cpar+frac{v_{thn}}{v_{DD}-v_{thn}}C_{A}=frac{V_{B}}{v_{DD}-v_{thn}}Cpar+frac{V_{thn}}{v_{DD}-v_{thn}}C_{A} (5)

从式(5)中可以看出,Cboot随输入电压变小而变大,并且随B点电压VB变大而变大。而B点电压直接影响N4的导通电阻,也就影响驱动电路的上升时间。因此在实际设计时,Cboot的取值要大于式(5)的计算结果,这样可以提高B点电压,降低N4导通电阻,减小驱动电路的上升时间。

P2、P4的尺寸问题

将公式(5)重新整理后得:

V_{B}=({V_{DD}-V_{thn})frac{C_{boot}}{Cpar}-V_{thn}frac{C_{A}}{Cpar} (6)

从式(6)中可以看出在自举升压周期内, A、B两点的寄生电容使得B点电位降低。在实际设计时为了得到合适的B点电位,除了增加Cboot大小外,要尽量减小A、B两点的寄生电容。在设计时,预充电PMOS管P2的尺寸尽可能的取小,以减小寄生电容CA。而对于B点的寄生电容Cpar来说,主要是上拉驱动管N4的栅极寄生电容,MOS管P4、N3的源漏极寄生电容只占一小部分。我们在前面的分析中忽略了P4的源漏电压,因此设计时就要尽量的加大P4的宽长比,使其在自举升压周期内的源漏电压很小可以忽略。但是P4的尺寸以不能太大,要保证P4的源极寄生电容远远小于上拉驱动管N4的栅极寄生电容。

阱电位问题

如图3所示,PMOS器件P2、P3、P4的N-well连接到了自举升压节点A上。这样做的目的是,在自举升压周期内,防止他们的源/漏--阱结导通。而且这还可以防止在源/漏--阱正偏时产生由寄生SRC引起的闩锁现象。

上拉驱动管N4的阱偏置电位要接到它的源极,最好不要直接接地。这样做的目的是消除衬底偏置效应对N4的影响。

Hspice仿真验证结果

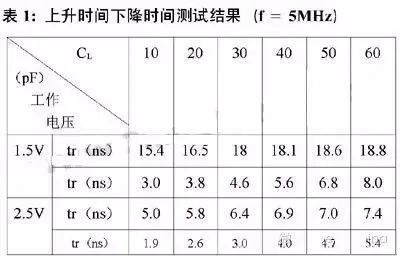

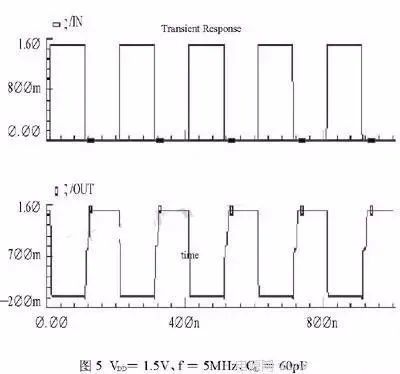

驱动电路基于Samsung AHP615 BiCMOS工艺设计并经过Hspice仿真验证。在表1中给出了电路在不同工作电压、不同负载条件下的上升时间tr和下降时间tf 的仿真结果。在图5中给了电路工作在输入电压1.5V、工作频率为5MHz、负载电容60pF条件下的输出波形。

结合表1和图5可以看出,此驱动电路能够在工作电压为1.5V,工作频率为5MHz,并且负载电容高达60pF的条件下正常工作。它可以应用于低电压、高工作频率的DC-DC转换器中作为开关管的驱动电路。

结论

本文采用自举升压电路,设计了一种BiCMOS Totem结构的驱动电路。该电路基于Samsung AHP615 BiCMOS工艺设计,可在1.5V电压供电条件下正常工作,而且在负载电容为60pF的条件下,工作频率可达5MHz以上。

编辑:黄飞

电子发烧友App

电子发烧友App

评论