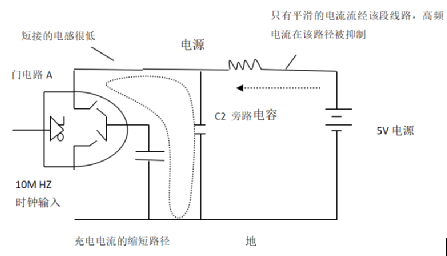

在某单板上,由于CPU芯片GMII接口的电源上只加了磁珠滤波,引起的故障:在网口通信时,当通信包的内容为低速码型(全0全1)时,没有丢包;当更改为伪随机包时(码型速率快),丢包严重。最终在磁珠后加电容,问题解决。

2022-10-25 17:06:18 2314

2314

***怎么显示敷铜时显示走线,走线时怎么在鼠标点击的地方弯折???/谢谢

2016-04-17 14:05:28

消除串扰的方法合理的PCB布局-将敏感的模拟部分与易产生干扰的数字部分尽量隔离,使易产生干扰的数字信号走线上尽量靠近交流地,使高频信号获得较好的回流路径。尽量减小信号回路的面积,降低地线的阻抗,采用多点接地的方法。使用多层板将电源与地作为独立的一层来处理。合理的走线拓朴结构-尽量采用菊花轮式走线

2009-06-18 07:52:34

噪声辐射出去。11、布线时首先考虑大电流走线和容易产生辐射的走线。12、开关电源通常有 4 个电流环:输入、输出、开关、续流,(如图 2 )。其中输入、输出两个电流环几乎为直流,几乎不产生 emi

2021-07-08 09:17:03

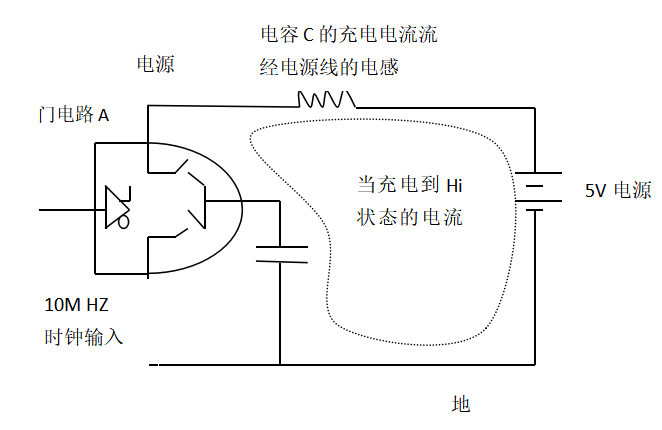

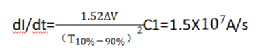

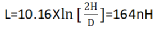

电源的VCC引脚,由于端子较远,VCC走线过长,寄生电感导致的电路振荡现象;增加储能电容之后,这个情况可能不会出现;简单理解就是,在负载需要瞬态变化的电流时,引线电感不能提供,而有储能电容提供;如果

2019-03-27 07:39:54

地,差模电感后电容接输出地。14、高频脉冲电流流径的区域:A:尽量缩小由高频脉冲电流包围的面积上图所标示的5个环路包围的面积尽量小。B:电源线、地线尽量靠近,以减小所包围的面积,从而减小外界磁场环路切割

2020-08-01 07:54:14

噪声辐射出去。11、布线时首先考虑大电流走线和容易产生辐射的走线。12、开关电源通常有 4 个电流环:输入、输出、开关、续流,(如图 2 )。其中输入、输出两个电流环几乎为直流,几乎不产生 emi

2022-04-16 14:30:53

原文链接除电源和接地端外该芯片引线的最少数目是19根。容量是512,512是2的9次方,需要地址线9根,8位则意味着有8根数据线,芯片还需要1根片选线,1根读写线,一共是19根。

2021-12-27 07:44:33

电源布局、网口电路、音频走线的PCB设计

2021-03-04 06:10:24

的安装位置距离电源线入口较远,造成引线太长。由于电源入口到滤波器输入端的引线过长,设备产生的电磁骚扰通过电容性或电感性耦合,重新耦合到电源线上,而且骚扰信号的频率越高,耦合越强,造成实验失败。平行走线

2023-03-11 14:17:49

我想走5000M,5K W .走4平的线。大概能走多远?我要是想走的更远应该加什么设备呢?谢谢!

2019-10-25 08:28:16

`帮忙看下下图那三根线怎么处理合适下图keepout层圆圈边上的顶层那三根线这样好,还是两个一连另外个垂直。或者还有其他办法。下图点亮的那个线是DGND,隔开他们的底层那个线式一个电源线。我就这样走

2011-07-19 16:14:30

本帖最后由 leozh456 于 2012-2-19 00:16 编辑

AD9 自动走线时部分线路已经手动走完了线,后自动走线时那些已经手动走过的线比如电源地等焊盘,软件会在原来基础上从新走线

2012-02-19 00:16:35

https://v.qq.com/x/page/u0348v9g7dw.htmlAD17的新功能优化走线,,,我想知道的是视频中框选了一部分走线后,是按什么按键做到选择了全部走线的

2017-06-04 19:55:08

PCB设计:通常的BGA器件如何走线?

2021-02-26 06:13:16

MIPI走线的6大法则MIPI总线在目前的移动设备手机/平板的LCD或者camera应用的十分广泛。身为硬件工程师,无论是查线或者走线都是一项基本工,下面是基于个人经验总结的MIPI走线的check

2018-05-21 11:53:33

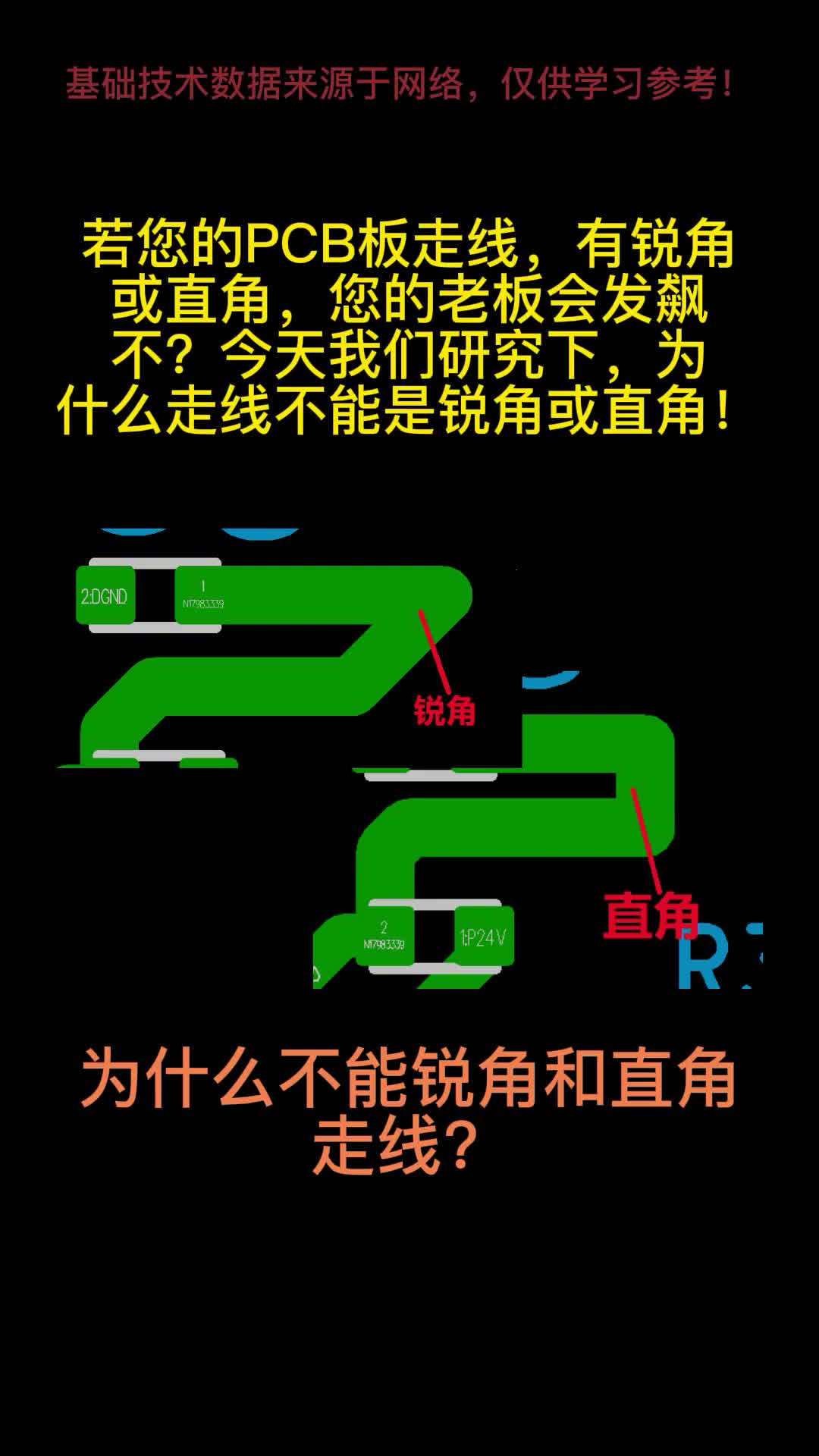

下面从直角走线、差分走线、蛇形线三个方面来阐述PCB LAYOUT的走线。

2021-03-17 07:25:46

的应用中,其产生的任何诸如电容,反射,EMI等效应在TDR测试中几乎体现不出来, 高速PCB设计工程师的重点还是应该放在布局,电源/地设计,走线设计,过孔等其他方面。当然,尽管直角走线带来的影响不是

2017-07-07 11:45:56

敏感模拟信号走线尽量短。 1.5 合理分配电源和地。 1.6 DGND、AGND、实地分开。 1.7 电源及临界信号走线使用宽线。 1.8 数字电路放置於并行总线/串行DTE接口附近,DAA

2018-11-28 17:06:35

好的图像质量的保证。 PCB走线如果可能的话,信号走线使用6mil, 走线间距使用6mil. 放置0.1uF的退耦电容在对应的DSP电源脚上,并尽可能的靠近。它的走线尽可能的粗。电源正极的走线最少要

2023-04-13 16:09:54

1.PCB走线线宽的重要性 PCB载流能力的计算一直缺乏权威的技术方法、公式,经验丰富CAD工程师依靠个人经验能作出较准确的判断。但是对于CAD新手,不可谓遇上一道难题。 对于大电流电源走线

2023-04-12 16:02:23

`为什么下图中PCB走线正反面不同。孔与孔之间为直接通路。为什么背面的走线环绕迂回。小白菜提问,求高手详解。谢谢`

2018-10-29 08:46:46

斯1艾1姆1科1技全国1首家P|CB样板打板所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少是线宽

2013-08-29 15:43:30

2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距>=2

2017-11-22 20:04:14

RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质?恶化,所以要求蛇形线间距最少是线宽的两倍,信号的上升时间越小就越?受分布电容和分布电感的影响。 因为

2018-09-20 11:05:23

、阻抗匹配 2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距

2020-07-14 18:02:17

:1、阻抗匹配 2、滤波电感。 对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线

2018-08-30 10:14:44

合理分配电源和地。1.6 DGND、AGND、实地分开。1.7 电源及临界信号走线使用宽线。1.8 数字电路放置於并行总线/串行DTE接口附近,DAA电路放置於电话线接口附近。

2019-05-30 06:58:19

只可能是连续的,通常相对缓慢。在PCB布局中,应使热回路面积小且路径短,以便最大限度地减小这些走线中的寄生电感。寄生走线电感会产生无用的电压失调并导致电磁干扰(EMI)。中国IC交易网用于降压转换

2019-08-12 11:58:13

本期干货:PCB设计中电源布局、网口电路、音频走线应该注意哪些问题呢?一.电源布局1、电源入口处随着电流方向电容摆放顺序:由大到小2、电源出口处随着电流方向电容摆放顺序:由大到小3、输出开关脚SW

2017-09-14 17:45:50

的数据;在走线时一般遵循3W法则(绕线的间距要两倍于线宽),这样可消除线间78%的互感,尽量减少因电感变化而引起的阻抗不连续。 另外说明我不是高手,抬得越高摔得越痛;若想见识高手,可以到WWW

2014-11-19 11:54:01

请教个问题Pads9.5中怎么设置电源和地在走线中默认大小为0.2而不是是用快捷更改的他的大小

2014-12-02 10:29:38

ad如何把走线隐藏

2015-10-12 14:52:21

设计led电源, 5.5mH, 采用0.19线径,240.5圈的EE10,请问这个电感最大电流是多少?我们打算设计总输出的电流是125mA,电压是85V,小白新手,望指教这个电感可以用到整灯功率为24w的led球泡电源吗?

2020-06-16 21:01:35

短。1.5 合理分配电源和地。1.6 DGND、AGND、实地分开。1.7 电源及临界信号走线使用宽线。1.8 数字电路放置於并行总线/串行DTE接口附近,DAA电路放置於电话线接口附近。2. 元器件

2014-03-14 17:44:44

`想问我这个有问题吗?为什么一动器件走线就走不了,小白跪求大神!!!`

2017-11-16 09:28:32

pcb布局,走线方面,有什么建议吗,该怎么怎么走,怎么提高效率

2016-10-15 14:51:34

2、滤波电感。对一些重要信号,如 INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距>

2019-05-22 02:48:05

2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距>

2016-12-07 22:20:49

原因,走线长度不能进一步减小,则可以通过将电流前向和返回走线并行的方法来减小电感。具体来说,若使用双层板或多层板,将两条平行线置于两层(或相邻层)相对位置,同时,为加强互耦以消除磁场,走线应尽量宽一些。

2017-07-17 17:19:56

走线时shift+空格,为什么改变不了走线模式呢???

2019-09-30 01:34:26

这拷贝的电源走线到信号走线一下线就变细了怎么弄的哦

2019-07-17 05:35:09

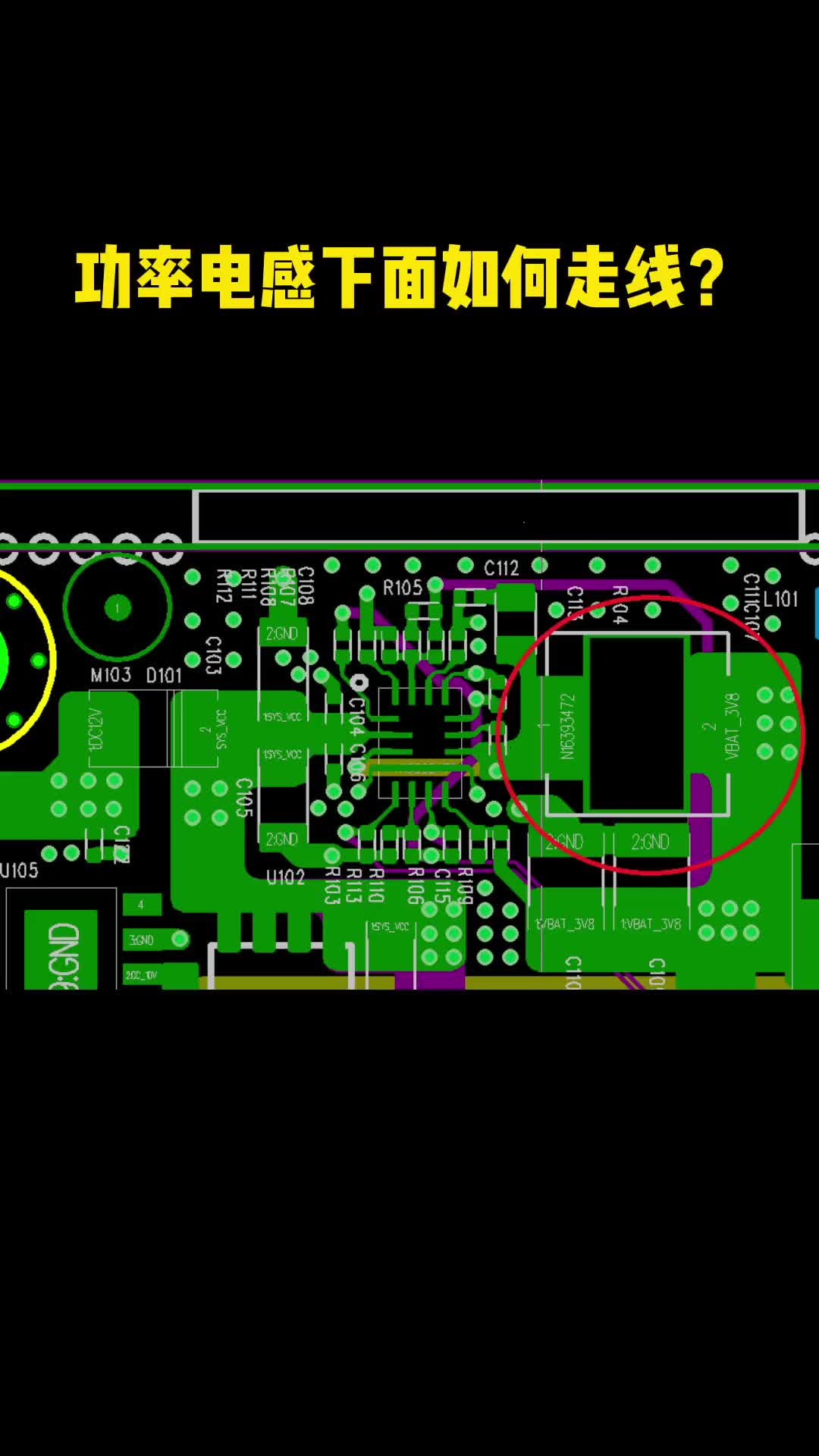

问题: 为何DC-DC 功率电感下方不该铺铜跟走线回答: 从Eddy Current角度分析:如果铺了铜,没有净空[1],则电感的磁场,会在该下方的金属上,产生Eddy Current [2]。而

2020-11-18 13:36:31

近年来,装机行业流行一个术语,即“走背线”,那么走背线是什么?装机之家小编简单介绍下,通俗的说:走背线就是针对电脑机箱,装机的时候,将机箱内部和电源的线材做到最干净整洁,从传统来说,线材都是从机箱

2021-12-29 07:13:36

主板走线和布局设计 对于一块主板而言,除应在零部件用料(如采用优质电容、三相电源线路等)方面下功夫外,主板的走线和布局设计也是非常重要的。由于主板走线和布局设计的形式很多,技术性非常强,因此这也

2021-07-29 08:42:13

对于一块主板而言,除应在零部件用料(如采用优质电容、三相电源线路等)方面下功夫外,主板的走线和布局设计也是非常重要的。由于主板走线和布局设计的形式很多,技术性非常强,因此这也是优质主板与劣质主板

2018-11-23 11:14:34

最近在更改一个板子,发现四层板的叠层,但是电源层和地层没有任何走线

2019-09-10 09:36:00

想问下AD中走线都走成弧形走线,有没有坏处?或者是在哪些情况下,会有明显的弊端?

2015-05-10 20:45:27

`内层的地层与电源层可以走线吗理论上地层与电源层相邻的面积越完整越近高频的阻抗越 低,实务上当外层(top and bottom side)的高速走线电磁幅 射太强的时候,为了降低表层幅射强度,在

2014-02-19 18:23:03

,分布电感越大。 3、印制电路板引线的分布电感 高频电路的印制电路板引起的分布电感不容忽视。为消除分布电感的影响,设计时要加宽电源线和地线,以减少电源线和地线的阻抗。 4、接插件的分布电感

2017-05-17 11:13:12

有的板子在同一层 但是走线和焊盘颜色分信号线和电源线是怎么设置的

2019-11-26 21:30:08

问一个比较弱智的问题,如果我使用的是四层板,中间两层分别为地和电源层,并且想要在电源层走线,我在添加层的时候,是不是只能选择add layer而不是add plane?我现在是add plane,怎么能够实现在电源层走线?

2019-07-04 04:36:10

在AD中运用脚本文件可以进行圆形螺旋走线,那么,如果要进行矩形走线,脚本文件应如何编写?

2016-10-04 19:58:26

如何消除电路中的电感?混沌与混沌同步原理是什么?常用的模拟电感电路有哪几种?

2021-04-22 06:29:49

东西是真的存在吗(还是只有我没怀疑)?说到芯片,就是引脚寄生电感,走线长点,就是引线电感这些东西,说到传输线,也说有寄生电感。那么它们到底是怎么来的呢?

2021-01-28 07:00:38

滤波电容的走线对滤波效果有至关重要的作用,走的不好,可能失去其应有的滤波效果。 图一是副边整流滤波走法,使二个电容效果分摊,避免第二个电容在整流回路中失效。 图二:为输出滤波电容走线,一定不要外挂(也就是被旁路掉),走的不好输出纹波很差。

2020-09-14 16:17:59

开关电源PCB布线原则及走线技巧

2019-03-06 11:43:16

开关电源地如何布局走线

2021-03-11 07:56:58

所有的电源(大电流)走线尽可能短、直、粗。在一块标准PCB板上,最好使走线的每安绝对最小宽度为15mil(0.381mm)。电感器、输出电容器和输出二极管应该尽可能靠在一起。这样可以帮助减少在大开关电流流过它们时,由开关电源走线引起的EMI。

2012-11-04 03:55:14

开关电源的PCB设计(布局、排版、走线)规范

2015-05-21 11:49:28

有一种新概念使您能够只用两条引线进行4线电阻测量为什么使用4条线测量电阻?2x4线电阻测量是怎样的?哪种万用表适合您?

2021-04-09 06:34:22

宽,距电源/地越近,或隔离层的介电常数越高,特征阻抗就越小。 11、PCB板上的走线可等效为串联和并联的电容、电阻和电感结构。串联电阻的典型值0.25-0.55 ohms/英尺。并联电阻阻值通常很高

2014-12-16 09:47:09

有点惬意了,。那要实现这些功能的前提,就必须要有相应的ups电源来支撑。作为支撑ups电源稳定工作的PQ型扁平线电感,那就需要满足外形小巧、损耗低。散热更好等特点,同时PQ型扁平线电感还需要具备抗干扰性

2022-05-19 09:59:30

本身带来很多麻烦电脑假如走线欠妥,众多的电源线就会像面条一样缠成一团,从而影响散热和吸引尘土。纵然你的机箱没有侧透,你也不应当忽略这一点。走线欠妥的后果,可远远不止表面难看,如果到处都是笨重的线,且没有...

2021-12-31 07:16:30

段3mil左右的走线,心想难道是这段走线引起的差异???根据电容频率公式:实际电容的谐振频率与电感L(此处L包括电容寄生电感以及回路电感)和容值有关, L越大,则谐振频率越小。结合此处情况,就是电容PIN到过

2022-12-21 14:52:42

有关,但线过长会增大分布电容和分布电感,使信号质量,所以时钟IC引脚一般都接RC端接,但蛇形走线并非起电感的作用,相反的,电感会使信号中的上升元中的高次谐波相移,造成信号质量恶化,所以要求蛇形线间距最少

2010-10-28 00:05:05

、阻抗匹配 2、滤波电感。对一些重要信号,如INTEL HUB架构中的HUBLink,一共13根,跑233MHz,要求必须严格等长,以消除时滞造成的隐患,绕线是唯一的解决办法。一般来讲,蛇形走线的线距

2018-11-23 17:02:19

计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如 PCI - Clk,AGPCIk、IDE、DIMM 等信号线。二

2023-03-22 10:33:44

请教一下各位pcb板上电源部分布局和走线的有哪些要点哦,可以把主板电源做纹波和噪声尽可能的小,最好能提供一下实物的参考layout板学习哦,谢谢各位了

2014-10-24 15:08:06

AD18 ,PCB,走线,任意走线,在哪里设置?

2019-03-07 01:36:59

ad割铜命名,走线怎么走圆弧型

2019-09-04 22:53:39

PCB长距离走线和短距离加个过孔走线哪种走线更合理?

2019-09-25 22:11:32

各位大侠 ,请教一个问题:1.pcb布线时,信号线,地线,电源线按照什么顺序布线?a.是先走信号线,再走电源线,最后走底线,在铺地?这样走的话,感觉电源线比较乱。b. 还是,先走一对平行的电源线

2019-07-28 23:20:27

在电源内缩上来走线可以吗???

2019-06-13 05:35:05

STM323.3v电源线,地线T字形走线可以吗?可以这样处理吗?

2019-03-01 06:36:02

比如电源走线线宽要加粗(例如20~30mil,第一优先),信号线一般宽度(例如10mli),但有些IC引脚很细,例如8mil左右。这如果选择8mil线宽走线会警报提示不符合10mil宽度,想问下这个怎么设置?

2019-04-12 04:58:24

温度易发生变化的场合.三线制引线方式与不平衡电桥配合使用,两根导线分别接在电桥的两个桥臂上,另一根导线接在电桥的电源上,消除了引线电阻变化的影响。③四线制 在铂电阻元件的两端各连接两根引线的方式称为

2018-07-04 13:59:29

>25,以最小化两个差分对信号之间的串扰; · 使差分对的两信号走线之间的距离S满足:S=3H,以便使元件的反射阻抗最小化; · 将两差分信号线的长度保持相等,以消除信号的相位差; · 避免在差分对

2018-11-27 10:56:15

当走线出现直角拐角时,在拐角处会产生额外的寄生电容和寄生电感,如图1所示, 这种不连续性会造成反射。 在走线确实需要直角拐角的情况下,可以采取两种改进方法,一种是将90°拐角变成两个45

2018-11-27 10:55:56

蛇形走线,因为应用场合不同而具不同的作用:(1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感和阻抗匹配的作用,提高电路的抗干扰能力。计算机主机板中的蛇形走线,主要用在一些时钟信号中,如

2019-03-22 06:20:09

高速中的蛇形走线,适合在那种情况?有什么缺点没,比如对于差分走线,又要求两组信号是正交的。回答:”蛇形走线,因为应用场合不同而具不同的作用:(1)如果蛇形走线在计算机板中出现,其主要起到一个滤波电感

2019-05-09 07:35:35

低阻抗脉冲形成网络引线电感的模拟及实验研究

2018-01-16 18:30:28 0

0

电子发烧友App

电子发烧友App

评论