一.前言

造成IR违例的原因分以下三类:

1.电流I大,这个和cell的选取(驱动能力,Vt类型)以及设计(翻转率,是否同时翻转等)相关;

2.电源网络电阻比较大,可能是弱连接(缺孔,power net密度不够等)导致;

3.电流和电源网络电阻相乘结果比较大。

对于后端工程师,如果说对电流大小能够控制的措施不多,电源网络电阻或者阻抗是可以在项目前期评估,选出比较合理的方案。本篇主要聊电源网络背后的一些理论。

电源网络在设计的时候有两个主要的目标:

2.占用最少的绕线资源.

为了让晶体管获得尽可能接近的供电电压,必须:

1.控制IR drop;

2.控制di/dt响应。

二.简化的电源网络

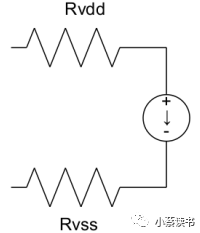

为了最大限度地提高cell利用率,设计的电源网络必须最大限度的减少绕线的congestion和整体面积的消耗。任何电源网络都有电压损失和电流需求。在满足器件、电路和系统在其规格范围内正常运行的要求的同时必须限制电压损失。下图中的电路演示了电源网络中的 IR 压降现象。

Rvdd 和 Rvss 代表电源和接地网络的电阻。电阻是金属线(metal wire)电阻和互连(interconnect)电阻的总和。当设计电源网络时,最小化电阻通常是首先要考虑的。上图中的电流源是一个变量,代表了设计中物理单元的电流消耗。这个电流由AC和DC分量组成,且有效电流随时间变化。因此,电阻两端的电压会发生变化,反过来,器件上的电压也会发生变化。除了为器件提供尽可能多的电压之外,还必须限制这种变化。

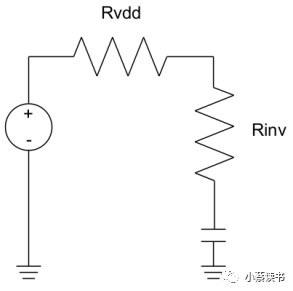

下图是一个RC电路,在其设计中包含了电源网络电阻对瞬态电压响应的影响。电源网络的电阻 Rvdd 和反相器的固有电阻 Rinv 串联,加上器件和接地网络的集总电容。

电源网络任何电阻的增加都会导致整个电路响应的减慢,反相器的开关性能下降。优化电源网络时,您必须最小化 Rvdd。

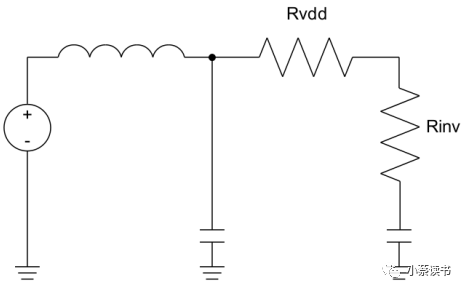

除了IR压降和反相器充电现象外,下面模型开始考虑设计中 di/dt 响应。因此,您必须考虑电感效应,这会将简化的电源网络转变为复杂的电源网络。

三. 电压、电容、电感、电流

1.电压注意事项

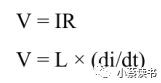

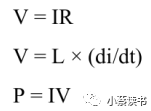

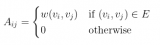

以下两个方程是计算电压时考虑的因素:

电阻是电源网络电压损失的主要原因。电源网络中的电阻越高,网络中的电压降就越大,从而导致到达给定器件的电压更小。因此,器件必须承受足够大的电压,以便有足够的电流。限制 IR 压降的目标是针对设计的平均电流要求提供足够的电流。

还必须考虑电感效应。所有设计在信号和电源或地面网络都具有片上电感。高频和高功率密度设计使电感影响在亚微米技术节点上越来越重要。大信号电阻在低频时可以支配阻抗并减轻电感效应。由于低电阻、高频率和高电流的组合,电感效应会影响电源。

2.电流注意事项

每个设计都有电流需求的变化,即电流随时间变化。时变电流会改变电阻器两端的电压。电感也起作用,但您必须考虑电流需求的变化。存在的总电流是时变电流加上静态电流设计的漏电流。

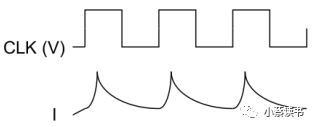

下图显示了包含上升沿触发的时序和组合元素的典型模块的最终电流波形与时钟的关系。时钟上升沿对应的峰值信号电流是正在导通的开关器件的总和。

必须提供足够的电流以满足信号切换要求。将峰值电流计算作为连续供电目标是过度设计。一个好的设计实践是:

1.满足平均电流要求;

2.以恒定电源的平均功耗要求为目标;

3.在需要的地方分配裕量以满足峰值电流和功耗的动态需求。

电源网络的设计考虑了 IR 压降和电感效应或 di/dt。IR 压降考虑针对平均电流要求,di/dt 考虑针对瞬时电流要求。

3.电压和电流的关系

必须注意电压和电流之间的关系。以下等式显示了电压和电流的相互依赖性:

电源网络的 IR 压降考虑旨在提供设计的平均电流要求。

4.电容注意事项

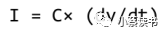

电容是电荷存储器件,它们可以提供电流。当电流从电容器放电时,电压降为:

可以在几个主要位置找到电源和地之间的寄生电容:

1.在金属电源线和地线之间;

2.在N阱和衬底之间;

3.在器件之间。

通常,去耦电容被添加到模块中以提供该瞬时电流。此步骤减少了直接从电源网络汲取的功耗。

5.电感注意事项

电感仅在存在时变电流时影响电压。在开关活动期间存在时变电流。任何开关信号都将电流从输入通过电源网络传送到输出。此步骤创建一个电流回路。电感L与该回路的面积 A 成正比。可以通过最小化该回路的面积来最小化电感。

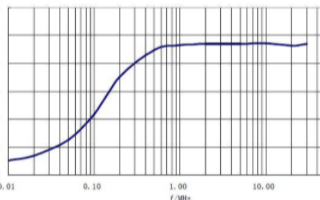

6.整体电源网络

一般整个电源网络由二维网格组成。顶部网格是顶部两层 M(top) 和 M(top-1) 上的粗粒度(course-grain)网格。该网格解决了 IR 压降。下面的网格是 M2 和 M3 上的细粒度(fine-grain)网格,满足设计的 di/dt 要求。上下网格中的每一层都包含电源和地straps。这些straps必须均匀分布。每个网格层之间的通孔的频率取决于设计的功耗密度。

四.电源网络怎么处理 IR Drop、EM、di/dt、电感的?

1.解决 IR Drop

一般推荐使用两个厚的顶部金属层来充分解决电压 (IR) 降。这些层是 M(top) 和 M(top-1)。它们很宽,提供高电容和低电阻,这对电力网络都是有利的。目标是用这两个金属层完全解决所有 IR 压降。

具有高速和高功耗密度的设计可能需要更多层来满足 IR 压降要求。即使使用工艺允许的最厚和最宽的顶部金属,设计也可能需要更多层。这些设计可能需要将 M(top-2) 添加到上部网格。设计可能仍不满足 IR 压降要求。可以将 M(top-3) 重复添加到上格以满足 IR 压降要求。

2.解决EM

可以在上下网格上使用间隔紧密的窄straps,以帮助防止 EM。在典型的设计中,与较不频繁地放置较宽的straps相比,更频繁地放置窄straps会阻止更少的布线资源。较宽的金属比窄金属更适合 EM,因为宽金属的电阻较小。如果放置许多窄straps,平行线的总有效电阻小于较宽、频率较低的带的有效电阻。

通常,上部网格用于 IR 压降,下部网格用于 di/dt。设计阶段与 EM 指南一起确定所需straps的数量、宽度和频率。如果这些网格是完整的,但您仍然无法满足 EM 准则,可以执行以下操作:

1.对于当几个单元紧密放置时在高驱动单元周围发生的局部 EM 问题,请在下部网格上添加额外的straps。这些高驱动单元的优点是引脚密度低,并且不会阻塞很多本地绕线资源。

2.对于高驱动单元中的 EM 问题,放置一个简单的totem pole。将 VIA 放置在上部网格、下部网格和可选的单元电源轨之间,从顶部网格向下。

3.对于全局 EM 问题,您必须使用类似于解决 IR 压降问题的方法解决顶部网格。为了满足 EM 要求,如果顶部网格的层不能更窄和更紧密地间隔,则使用更多层。

3.解决 di/dt

一般建议在 M2 和 M3 上使用细粒度网格,以满足设计的瞬时电流要求。设计可以从顶部电源网格中提取此电流。但是,此步骤可能会导致延迟,因为电流必须通过过孔进出顶部的两个金属层。这个较低网格的参考目标是防止边缘率下降超过 10%。这种退化是解决 di/dt 的主要问题。提供这种较低的网格可以更快地访问存储在设计中的寄生电容和去耦电容中的电流。尽管较低的金属层比顶部网格中的层更窄(宽度和厚度),但要通过的过孔更少。因此,总电阻小于从顶部网格汲取电流时的电阻。然而,下金属层电阻可以大于上金属层。

straps之间的距离越小,di/dt 响应越好。将这些straps彼此靠近放置,以便在各个方向上快速到达更多电容位置。然而,下部网格的间距绝不能比单元本身内包含的电源轨更紧密。如果这个网格太紧,就会阻塞太多的绕线资源。

4.解决电感

电感随着电流返回路径的面积而增加。可以通过以下方式最小化当前返回路径的面积:

1.在下部网格上均匀分布straps;

2.在下部网格上紧密间隔straps。

这些步骤提供了规则和附近的电流路径以减少电感。均匀分布的straps还可以减少局部绕线拥塞。虽然宽线的电阻比窄线低,电感通常较大。

五.电源网络总结

最有效的电源网络由两个电源网络组成,一个上电源网络和一个下电源网络。每个网格由两个正交方向的金属层组成。

下面总结了上面的网格:

1.解决 IR Drop;

2.解决全局EM ;

3.使用顶部厚金属层。

下面总结了下面的网格:

1.解决di/dt;

2.解决局部EM;

3.解决信号电感;

4.使用较低的薄金属层。

审核编辑:刘清

电子发烧友App

电子发烧友App

评论