时钟电路是芯片中最基础的电路,时钟电路性能的好坏关乎SoC中所有电路能否达到预期目标,例如:计算核(CPU/GPU/NPU)的主频,DDR的带宽,高速接口(PCIE)的带宽等。

2022-10-12 15:08:47 4746

4746 For signals requiring low jitter, such as ADC sampling clocks, TI’s ISO73xx family of low jitter devices

2018-10-11 15:18:30

The Keysight 71501C jitter analysis system is designed to help you do a thorough jitter charcterization of your device.

2019-05-15 15:50:52

There are also tutorials for the three main jitter analysis measurements: jitter transfer, jitter tolerance, jitter generation and output jitter.

2019-08-13 09:31:10

This document describes the functions, properties and methods for controlling the Spectral Jitter measurment from a remote application

2019-08-02 11:18:17

Jitter, Noise, and Signal Integrity at High-Speed-Mike PengLi

2015-10-26 15:03:11

ADC 控制控制2:0x48

但从MCLKO/XO却量测到153kHz输出,并且I2S讯号也未输出,SPI已确定能够正常读写。

我试着往上调整MCLK/XI的频率到一定程度时,MCLKO/XO就会量测到Jitter非常大的讯号。

请问是否在电路上有什么地方需要注意? 或是寄存器设定要如何修改?

谢谢您。

2023-11-30 06:18:18

source from FPGA, exactly how much jitter can we expect from the I/O lines. This is very critical

2019-05-17 14:04:07

This product note discusses the nature of Jitter tolerance problems and describes a method

2019-03-27 13:56:20

吗? 以上来自于谷歌翻译 以下为原文Hi I have a DSO80204B 40Gsa/s Infiniium and want to measure jitter of an oscillator.

2019-03-01 15:07:22

floor, lowest jitter measurement floor, lowest trigger jitter and flattest

2019-10-31 12:20:33

include the industrys lowest noise floor, lowest jitter measurement floor, lowest trigger jitter and flattest frequency response.

2019-10-24 07:04:53

the L6206Q using the EVAL6206Q board. The output of the chip exhibits excessive jitter. Is this a regular

2019-03-19 08:00:50

Features specific information on jitter intrinsic performance.

2019-07-11 08:31:00

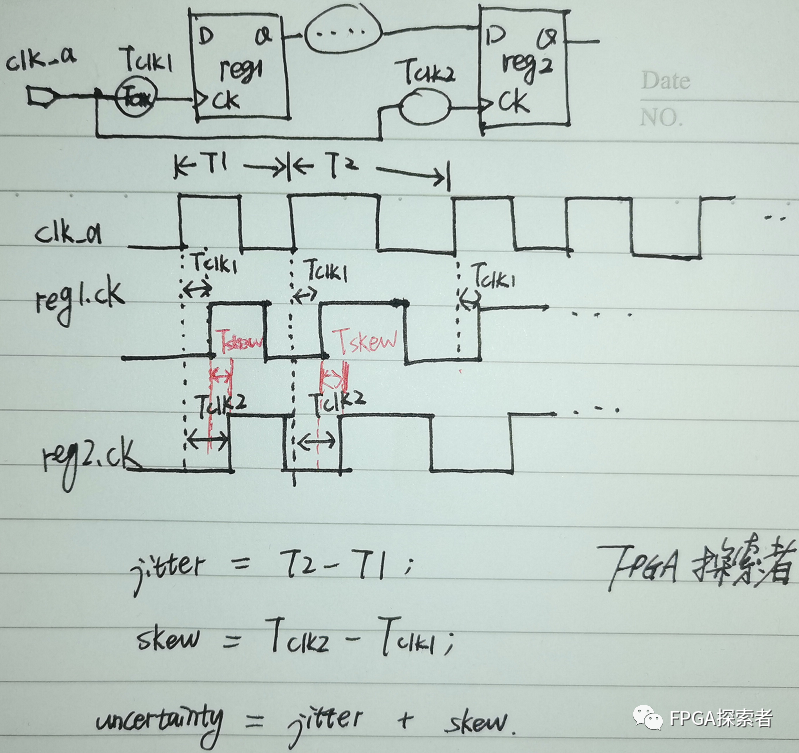

PLL jitter 对建立时间和保持时间有什么样的影响?哪位大神给解答下

2015-10-30 11:16:30

The Clock Wizard reports the individual jitter for each DCM/PLL as DCM0 - 213 ps, DCM1 - 221 ps, PLL0

2019-07-23 14:02:15

的,于是这里就有了数字信号防干扰的需求。 另外,USB的同步和异步传输。USB 音频使用同步传输的时候确实是跟Jitter相关的,因为USB协议会发送一个SOF(起始帧)同步每个采样包,而接受端(比如

2016-09-27 17:16:28

和异步传输。USB 音频使用同步传输的时候确实是跟Jitter相关的,因为USB协议会发送一个SOF(起始帧)同步每个采样包,而接受端(比如USB DAC芯片)需要根据这个起始帧来同步,也就是说传输

2016-12-05 10:46:10

Demo Setup for Stimulated Jitter Measurement with 81134A and 54855A

2019-07-11 08:21:45

Describes how to generate and measure jitter with the 81133/34A and 54855A

2019-08-07 14:26:25

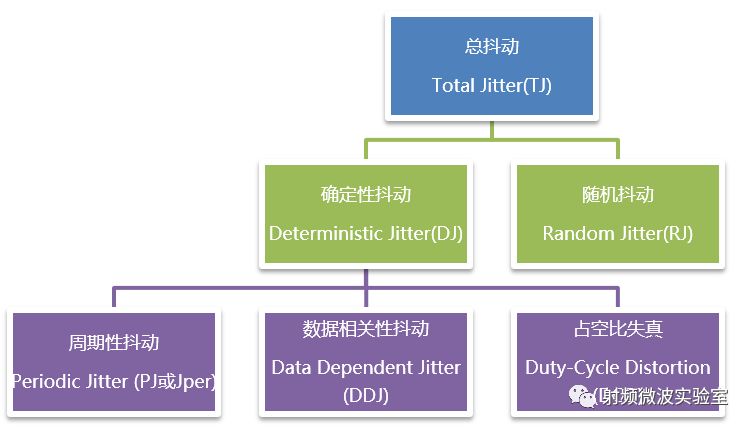

error performance analyzers to determine Random Jitter, Deterministic Jitter, and Total Jitter.

2019-07-19 15:05:39

See how the time correlation of jitter to the real-time signal makes it easy to trace jitter components to their sources (21:30)

2019-09-24 17:15:00

jitter generation capabilities for jitter-tolerance testing (J-BERT) of serial gigabit devices up to 12.5 Gb/s.

2019-09-24 12:18:45

This Application Note emphasizes on the emerging techniques for reference clock jitter analysis

2019-10-14 09:08:46

This white paper describes how various jitter analysis techniques give dissimilar results.Which

2019-10-08 06:54:43

Separating jitter into its random and deterministic components (called “RJ/DJ separation”) is a

2019-09-30 07:23:58

为原文hi,I wonder how much is the jitter of RXRECCLK in spartan-6 GTPs. is there any document describe

2019-07-01 13:31:36

大家好如果I0和I1都连接到BUFGCTRL,如何计算输出时钟的DISCRETE JITTER?我得到335ns DJ,而源时钟有80ps P-P JITTER。以上来自于谷歌翻译以下为原文Hi

2019-03-22 09:30:34

This application note compares different total jitter measurement and extrapolation techniques to the Fast Total Jitter Measurement

2019-09-25 16:22:41

As data rates increase, the effects of jitter and noise become critical. The relationship between

2019-09-29 08:02:51

Explains the fundamentals of Jitter, the various components, challenges, and the capabilites for the ParBERT 81250.

2019-08-08 09:01:52

This applicaiton note describes gain fast and efficient insight into the operation and performance of CDR, clock system and jitter tolerance.

2019-08-21 09:24:16

抖动的知识及测量方法在数字通信系统,特别是同步系统中,随着系统时钟频率的不断提高,时间抖动成为影响通信质量的关键因素。本文介绍了时间抖动(jitter)的概念及其分析方法。关键字:时间抖动

2008-11-27 08:28:56

Mastering Jitter in Serial Gigabit Designs

2019-10-09 10:24:14

As jitter is present in all telecommunications networks to some degree, network elements (NEs) must

2019-02-18 15:14:29

求CycloneIV内置PLL和Spartan 6内置DCM的jitter值.OSC 50MHZ普通有源晶振输入.求个大概值。是1ps、10ps还是100ps级的?驱动两片250MHZ的8位ADC做

2014-02-11 21:52:34

的 phase noise ? 2,我们一般对crystal osc 说的 jitter 指标是不是应该是JCC 或者JCC-K ,因为它没有外加基准参考频率,看JC JC-K 没意义 ? 如果是JCC-K

2021-06-24 07:25:23

EZJIT jitter analysis software from Keysight, combined with Infiniium Series oscilloscopes, provide

2018-10-09 15:27:49

The Keysight 53310A's fast histograms make it easy to get complete view of clock jitter. The shape

2019-04-18 16:38:14

一般翻译为时基误差, 成因并非影像波型资料本身的错误,而是时间部分出错了, 其错误的时间差即称之为Jitter, Jitter 造成振幅没有在准确的时间呈现出来使得影像波型扭曲, 而影像可能会因此而

2015-11-12 14:48:41

请教一下hspice的激励源里怎么增加jitter

2014-09-15 09:06:26

如下的改进:REF1 和REF2被屏蔽掉,由内部VCO直接生成输出时钟,即out0-out3为156.25M,out4-ou5均为25M。请问这样改进芯片是否支持?jitter会不会有所降低?如果可以的话,请给出寄存器配置.

2018-12-25 14:16:11

因为有占空比稳定器,转换器对时钟输入的占空比不敏感,但是对时钟jitter却很敏感,为什么?

2018-10-12 09:08:47

estimate for the output jitter of a PLL in S6.The datasheet says to reference the wizard.Here's our

2019-06-14 08:31:44

TI工程师你好,前端的其他芯片把I2S给到PCM1794的iIS信号,( LRCK,DATA,BCK,SCK,),经常看到有人说JITTER,JITTER超过10PS影响音质啥的.1.然后说外加独立

2019-08-19 08:50:51

There are four kinds of PLL jitter:1.period jitter2.short term jitter3.long term

2021-06-24 06:48:21

看了hspice的demo里用.sn命令跑的,然后有个phasenoise计算jitter啥的看着都是模块的。这个能整个pll跑完再计算jitter吗?还是也得分开跑再按照传输函数噪声拟合?

2021-06-25 07:17:07

嗨,将input_jitter值与周期约束一起使用而不是仅仅收紧周期有什么不同?防爆。输入抖动:+/- 100 ps周期:10 ns约束1和2是等价的吗?1)TIMESPEC TS_clk

2019-03-18 06:28:58

This application note describes how to use a real-time oscilloscope with jitter analysis, along

2019-08-07 14:33:56

Complete solutions for characterization and test of jitter in high-speed digital transmission systems, high-speed I/O connections, and buses.

2019-11-06 09:33:45

Information Theory Computer Science Mike Peng Li Prentice Hall Jitter, Noise, and Signal Integrity

2019-02-15 11:53:51

The MAX3671 is a low-jitter frequency synthesizer that accepts two reference clock inputs

2009-02-08 18:59:42 13

13 The MAX3673 is a low-jitter frequency synthesizer that accepts two reference clock inputs

2009-02-11 18:02:10 21

21 Abstract: The MAX3670 low-jitter clock generator is a monolithic phase-locked loop (PLL) that uses

2009-04-22 11:23:13 20

20 and data recovery at rates of OC-3, OC-12, and 15/14 FEC. All SONET jitter requirements are met, including jitter transfer, jitter generation, and

2009-09-15 08:31:21 15

15 and data recovery at rates of OC-3, OC-12, OC-48, Gigabit Ethernet, and 15/14 FEC rates. All SONET jitter requirements are met, including jitter tr

2009-09-15 09:01:55 21

21 The AD9512 provides a multi-output clock distribution in a design that emphasizes low jitter

2009-09-15 09:32:36 18

18 The AD9513 features a three-output clock distribution IC in a design that emphasizes low jitter

2009-09-15 09:34:16 15

15 The AD9514 features a multi-output clock distribution IC in a design that emphasizes low jitter

2009-09-15 09:35:53 13

13 The AD9515 features a two-output clock distribution IC in a design that emphasizes low jitter

2009-09-15 09:37:34 17

17 pinout minimizeinternal device jitter, while configurable 0/25/50/100%pre-emphasis overcomes external ISI jitter effects of lossy

2009-10-12 15:26:51 5

5 and flow-through pinoutminimize internal device jitter and simplify board layout,while pre-emphasis overcomes ISI jitter effects f

2009-10-12 15:32:00 17

17 and flow-throughpinout minimize internal device jitter and simplify board layout,while pre-emphasis overcomes ISI jitter effects

2009-10-12 15:42:39 25

25 and flow-through pinout minimizeinternal device jitter and simplify board layout, whileconfigurable pre-emphasis overcomes ISI jitter effects f

2009-10-13 08:24:56 19

19 Data-dependent jitter of transmitter for Non-Framed PRBS and SDH-Framed signal weresimulated.

2010-03-03 08:39:48 14

14 JITTER ANA

2010-07-08 15:32:54 8

8 If jitter at the input port of a network element (NE) exceeds a thresholdvalue, errors or loss

2010-07-09 16:59:46 14

14 This application note focuses on jitter measurements of componentsand equipment that make up

2010-07-15 23:59:10 28

28 IntroductionWith higher-speed clocking anddata transmission schemes in thecomputer and communicationsindustries, timing margins arebecoming increasingly tight.Sophisticated techniques arerequired to ensure that

2010-07-19 15:05:07 16

16 Welcome to the second edition of Agilent TechnologiesUnderstanding Jitter and Wander Measurements

2010-07-19 15:09:28 21

21 With the 81134A it is easy toadd jitter to any kind of dataor clock signal. This is veryuseful

2010-07-21 20:04:24 9

9 本文分析了晶振的漂移对GPS接收机的影响,从锁相环理论的角度,重点分析了采样时钟抖动对基带载波跟踪和伪码跟踪性能的影响,并给出一种环路分级降带宽的方法来消除这种影

2010-07-23 10:49:08 6

6 AbstractJitter is increasingly analyzed by separating a signal’s timing noise into its random and deterministic components, yet there is no reference standard for measurement verification. We introduce a precisely cal

2010-07-26 10:43:38 5

5 IntroductionSeparating jitter into its randomand deterministic components(called “RJ/DJ separation

2010-07-28 20:55:57 7

7 Abstract: High-speed applications using ultra-fast data converters in their design often require an extremely clean clock signal to make sure an external clock source does not contribute undesired noise to the overal dynamic performance of

2009-04-16 16:34:23 1576

1576

用DSP实现抖动(Jitter)测量的方法

近年来,抖动(Jitter)已经成为通信工程师非常重视的信号特征。在数字系统中,时钟频率正在变

2009-08-17 17:04:54 990

990

Aperture Jitter Calculator for ADCs

Abstract: This application note clarifies the operation

2009-09-18 08:38:10 1200

1200

抖动/歪斜,抖动/歪斜是什么意思

什么是抖动(jitter)

所谓jitter就是一种抖动。具体如何解释呢?让我

2010-03-22 14:42:49 1895

1895 Abstract: This application note describes how sampling clock jitter (time interval error or TIE

2012-10-12 10:58:23 32

32 The SL16020DC is a low power dissipation spread spectrum clock generator using SLI proprietary low jitter PLL.

2017-09-11 12:53:34 11

11 The SL16010DC is a low power dissipation spread spectrum clock generator using SLI proprietary low jitter PLL. The SL16010DC provides two output clocks.

2017-09-11 13:37:45 4

4 The AD9508 provides clock fanout capability in a design that emphasizes low jitter to maximize

2017-10-19 13:26:20 14

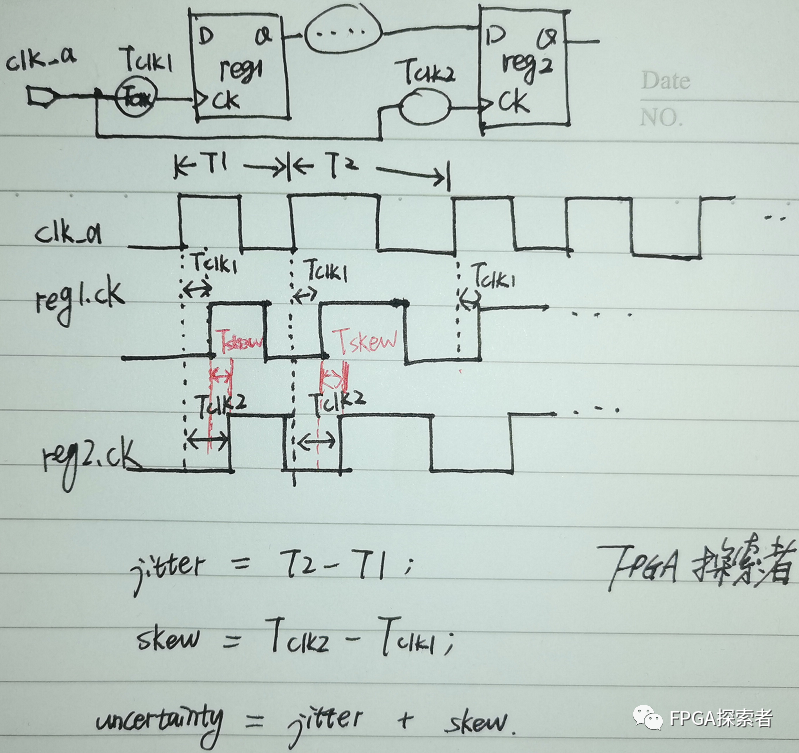

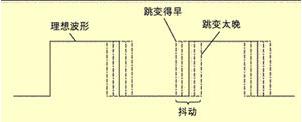

14 在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但不幸的是,这种信号并不存在。如图1所示,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动(jitter)。

2018-03-13 10:21:08 84702

84702

Discrete Jitter是由MMCM/PLL引入的,其具体数值可通过点击图2中Clock Uncertainty的数值查看,如图5所示。通常,VCO的频率越高,引入

2018-11-12 14:40:00 5091

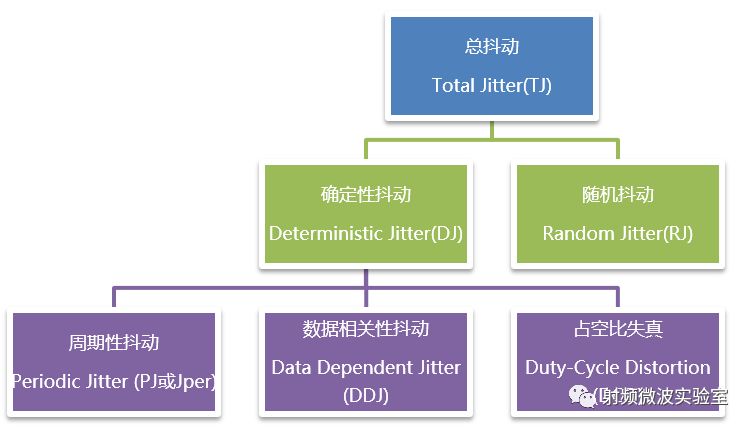

5091 整个jitter可以分为RJ(随机性Jitter)和DJ(确定性jitter)两大类。它们的分类主要跟根据是否有界,也就是是否有最大值来区分。RJ在分布上是高斯分布,其没有边界的也就是没用最大值

2020-05-14 15:37:16 9309

9309

AD9540: 655 MHz Low Jitter Clock Generator Data Sheet

2021-01-28 15:37:31 6

6 前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

2021-04-07 16:43:45 7378

7378

在时钟电路的设计中,存在 jitter 和 skew 问题。

2023-06-26 16:49:17 1011

1011

抖动jitter的有关概念和理论很多,容易把人抖晕;本文目的是帮助产品研发和测试工程师,不需要研究时频域抖动测量的原理和公式,只讲用什么手段测抖动,以及测试值的表达含义。

2023-07-07 17:30:08 2707

2707

相位抖动Phase Jitter,Jitter小一些比较好,比较稳定。但是跟Transient有一定矛盾,需要在两者之间取平衡点。

2023-10-12 15:09:02 260

260

电子发烧友App

电子发烧友App

评论