可编程逻辑控制器是工业自动化领域的重要组成部分。基本的PLC组件必须足够灵活并可配置,以满足不同工厂和应用的需求。本文着重介绍可编程逻辑控制器(PLC)基本操作及功能简介。

2013-04-07 10:05:17 9841

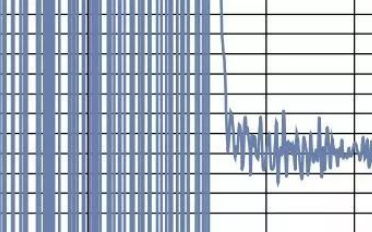

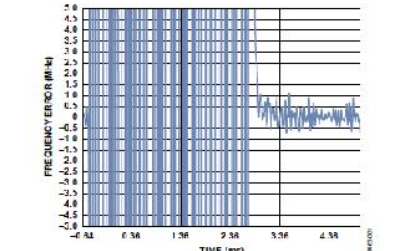

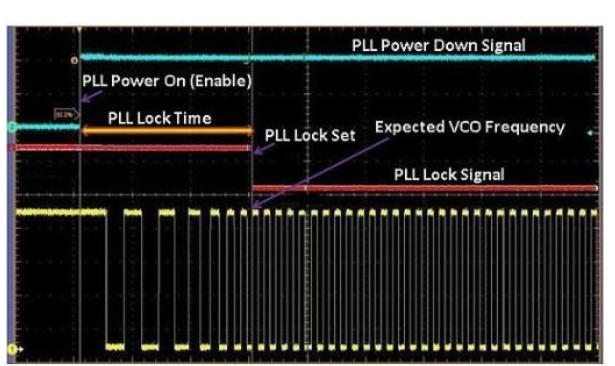

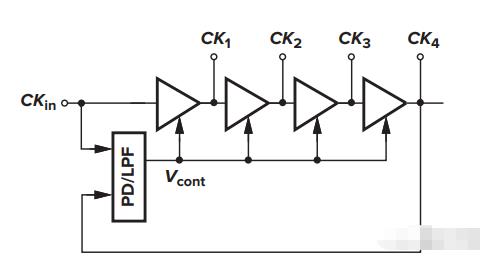

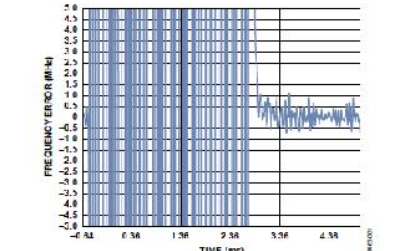

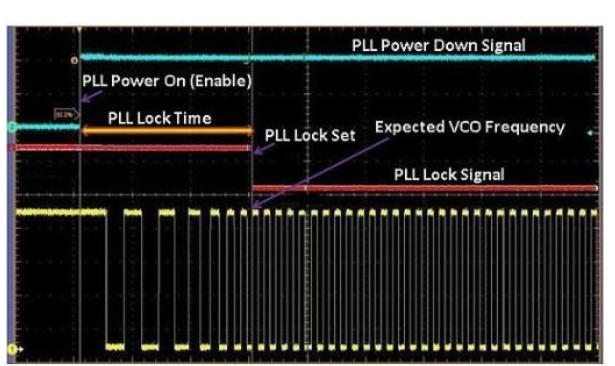

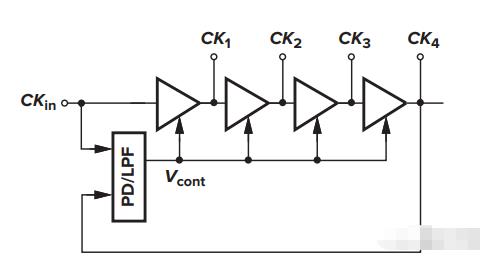

9841 按照上述步骤校准完成后,PLL 的反馈操作使 VCO 锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短。

2018-05-18 08:35:20 5327

5327

使用自动校准模式时,总锁定时间对某些应用来说可能太长。 本应用笔记提出一种通过手动选择频段来显著缩短锁定时间的方案

2021-06-21 09:53:59 4651

4651

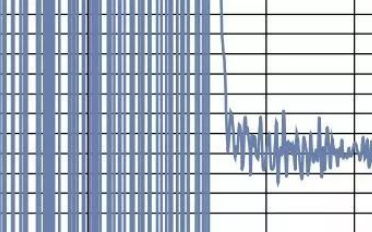

逻辑分析仪是一种类似于示波器的波形测试设备,它可以监测硬件电路工作时的逻辑电平(高或低),并加以存储,用图形的方式直观地表达出来,便于用户检测和分析电路设计(硬件设计和软件设计)中的错误。逻辑分析仪

2017-08-07 10:27:22

逻辑分析仪是一种类似于示波器的波形测试设备,它可以监测硬件电路工作时的逻辑电平(高或低),并加以存储,用图形的方式直观地表达出来,便于用户检测和分析电路设计(硬件设计和软件设计)中的错误。逻辑分析仪

2017-08-18 10:06:38

锁定放大器4053部分如图所示 给电路板只上+-5V的时候 4053逻辑是正确的 4和15脚输出波形互补(正常)但一旦供上+-12之后 就会出现逻辑功能错误的现象,4和15波形一样了(不正常) 求

2016-06-28 19:07:21

本帖最后由 893053742 于 2016-6-27 23:45 编辑

锁定放大器4053部分如图所示 给电路板只上+-5V的时候 4053逻辑是正确的 4和15脚输出波形互补(正常)但一旦

2016-06-27 23:22:17

您好工程师:

当我使用AD9122时,内部锁相环无法完成锁定,参考时钟来自AD9518产生的500MHz时钟,频率倍增产生1GHZ DACCLK

配置如下

0B 20

0C E1

0DD4

0A 电容

0A A0

最后读到0E的7位不能是1,不能完成锁定,希望能帮忙解决,谢谢

2023-12-01 07:29:29

之前使用开发板,进行配置,BBPLL可以锁定,但自己做的单板却无法锁定,检查电平和时钟都没有问题,使用的配置寄存器的值@和开发板的一样,请问还有什么可能的原因导致BBPLL无法锁定。@

2019-01-11 10:49:26

你好,请教个关于本振的问题:ADF4193的锁定:从手册上看,当前向分频之后的频率和VCO输出频率分频之后两个频率差在一定范围之内,内部逻辑检测到连续几个脉冲之内在范围内,就判定为锁定,从手册上看是

2018-09-04 10:42:32

DC逻辑综合详解DC软件简介逻辑综合DC命令DC软件简介DC( Design Compiler )为Synopsys公司逻辑合成工具。DC得到全球60多个半导体厂商、380多个工艺库的支持。据

2021-07-29 08:07:14

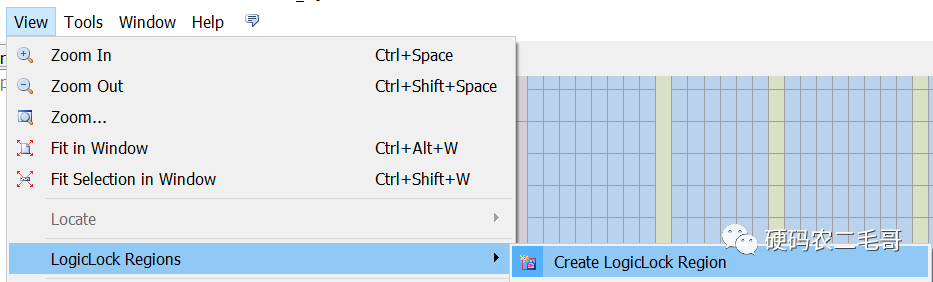

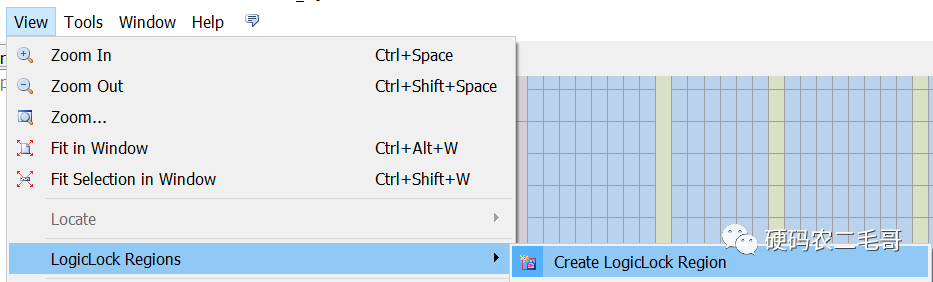

工程设计文件 5.6 编译及仿真工程 5.7 约束及配置工程 5.8 LogicLock逻辑锁定工具使用技巧 5.9 SignalTap II在线逻辑分析仪的使用方法 5.10 典型实例9

2012-02-09 15:45:32

(1.28Gbps))。所以我有6个PLL。我的GTP设计是完全对称的。只有一个MGT_USRCLK模块的PLL(PLL0)被锁定,另一个(PLL1)被锁定一小段时间,然后再被锁定一小段时间再重新锁定一小段时间等等

2019-06-19 11:27:42

MIPS P5600简介高端32位MIPS CPU的演进

2021-02-04 07:42:08

宏定义LEDS_CTL 的使用Makefile脚本语法简介Makefile测试

2020-12-22 06:39:05

为什么在选用MAX7000系列的器件的时候,总是提示“该器件不支持logiclock”的问题啊?编译的时候也是这个问题。该怎么解决么??谢谢。“The device or device family does not support logiclock regions”........

2015-03-14 12:07:07

一.GPIO简介每个通用IO口包括4个32位配置寄存器:GPIOx_MODERGPIOx_OTYPERGPIOx_OSPEEDRGPIOx_PUPDR2个32位数据寄存器

2022-01-18 09:29:25

XE164FN40芯片被锁定,DAS可以扫描出能连接上,但是keil5在线仿真时显示芯片被锁定。有没有办法擦除锁定,里面的东西不重要,片子能用就行。

2024-02-06 08:30:53

PS和PL互联技术ZYNQ芯片开发流程的简介

2021-01-26 07:12:50

altium designer 锁定“导线”和“所有器件”锁定,最主要目的是防止PCB生产厂家拼板时“不小心”改变PCB走线和器件位置等。快捷键解释: Shift+F单击对象以显示Find

2016-01-12 20:30:17

:matlab版本是否学生版 isunix :是否unix版本 isa() :指定对象是否属于指定类 logical() :把数值数组转变为逻辑数组 A(B) :A为数值数组,B为逻辑数组时,按B索引的非零元素返回A中相应位置元素 mislocked() :当前文件是否锁定 ..

2011-07-13 14:08:24

《数字逻辑电路CAI》课件简介成都航空职业技术学院 邱寄帆 在深化教育体制改革、全面推行素质教育的今天,教学方法和教学

2009-10-11 09:26:37

具有逻辑运算和逻辑处理功能,用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字逻辑电路,包含门电路、触发器、缓冲及驱动器、计数器、译码器、复用器、多谐振荡器、模拟开关等电路。74HC1648

2020-03-28 11:05:02

我的CFR3=32'h1a1f_4132,输入时钟是25MHZ。使用示波器侧得LOCK锁定,达到预期156(625/4)。把FTW改变之后竟然LOCK失锁,且156MZH的时钟变为240MHZ。为什么FTW会影响锁定的时钟呢?

2018-12-29 14:16:27

你好,我一直在用户电路板设计上使用ST25RU3993,但尚未成功锁定PLL。我试图手动和使用auto命令设置VCO范围。我尝试了各种载波频率/基频/参考频率设置的组合。在尝试解决问题时,我注意到

2019-08-12 10:09:46

什么是同步逻辑和异步逻辑?同步电路和异步电路的区别在哪?时序设计的实质是什么?

2021-09-29 07:33:38

线锁定同步 (LINE LOCK)是一种利用交流电源来锁定摄像机场同步脉冲的一种同步方式。当图像出现因交流电源造成的网波干扰时,将此开关拨到线锁定同步(LL)的位置,就可消除交流电源的干扰。

2008-12-29 13:47:50

目录1.GPS导航简介2.伽利略导航简介3.Aeroflex GPS测试产品简介4.GPSG-1000测试应用

2019-07-24 06:20:48

vhdl描述13.2.2 滤波器设计和结果13.3 logiclock优化设计——底层模块设计13.3.1 建立底层模块工程13.3.2 建立父区域13.3.3 定义逻辑锁定子区域13.3.4 将设计实体

2016-09-27 22:29:03

什么是可编程逻辑? 在数字电子系统领域,存在三种基本的器件类型:存储器、微处理器和逻辑器件。存储器用来存储随机信息,如数据表或数据库的内容。微处理器执行软件指令来完成范围广泛的任务,如运行字处理

2019-07-10 08:16:49

你好在DCM中有一个RESET输入引脚。我已将RESET引脚指定为分配RESET = ~LOCKED // DCM锁定,希望这将使RESET从开始起至少保持三个时钟周期。当我使用这种类型的赋值

2019-06-06 07:23:45

如何将PROTEL99画好的原理图中所有元件锁定在一起。

2014-04-16 23:53:40

如何手动缩短PLL锁定时间?你知道吗?利用手动频段选择,锁定时间可从典型值4.5 ms 缩短到典型值360 μs。本文以高度集成的解调器和频率合成器ADRF6820 为例,告诉大家如何手动选择频段以缩短PLL锁定时间。

2019-07-31 07:54:28

,但是每次我只能看到中断发生一次,并且不会重置。还有,有人告诉我,也许我MCU上的#19(RE9/RPI89/AN21)引脚被锁住了,所以我应该解锁,映射它,然后使用下面的命令和语法再次锁定它。f我们知道

2020-03-20 09:53:37

嗨,我有Digilent的ZYBO板,我是从Trenz购买的,因为我在英国。当我买它时,我无法获得带有锁定Zynq 7010设备的设计工具凭证的配件包。当时它甚至没有列出,现在已经上市,但没有库存

2018-12-12 10:45:18

最近使用ADF5356 | 小数N分频锁相环 (PLL)实现信号源,FPGA控话制SPI,始终不能锁定,初始化配置899MHZ没问题,但是更改N,F值不能锁定,按照手册更改各种参数和配置顺序,硬是

2018-11-18 20:47:39

一个移动电源的芯片,芯片的BAT锁定电压是3.15V,但是现在电池的过放都是3.0V,等到电池过放保护时,远远超过了芯片锁定电压了。问一下论坛里的高人,有没什么来使BAT端电压达到3.0V以上?比如在电池端串一个电阻之类什么的。先以为在电池的负极串一个二极管会提高,结果电压还低了。

2017-11-23 11:00:52

] BUFDS类型为clkingen_ML_BUFDS,原因如下。 这个问题的原因: 与此结构相关的一些逻辑被锁定。这应该导致 要锁定的其余逻辑。我们应该找到一个问题 将BUFDS

2018-10-17 14:29:54

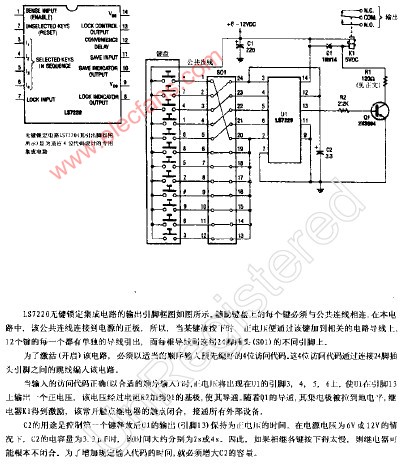

`电脑键盘锁功能及使用方法简介一、功能简介: 本程序为电脑键盘按键锁定工具。用户可以有选择地锁定或解锁电脑键盘上的某些按键。二、注意事项: 1、用户自行设置的程序密码请务必牢记,否则将会导致键盘无法

2011-12-30 15:04:22

我购买了一个virtex-7 fpga vc709连接套件,es- 节点锁定设备锁定许可证。我打算将软件安装到我的电脑上。我想知道我将来是否可以某种方式将许可证转移到另一台计算机上,如果是这样的话

2018-11-30 14:55:33

最近调试有两个问题需要您释疑: 1.9548有频率锁定和相位锁定。两者之间有关系吗?锁定有无先后顺序的要求? 2.在9548频率和相位都锁定之后,9548还是在不停的校准,为什么还会时不时的失去锁定,这是什么原因?配置问题吗?谢谢!

2018-09-05 11:45:27

pcb板手动布线锁定以后怎么解除锁定

2019-07-04 05:35:12

Ben Zhang简介ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于高级通信系统。它内置一个宽带I/Q解调器、一个小数N/整数N分频锁相环 (PLL) 以及一个低相位噪声多核

2018-10-31 10:16:46

【产品简介】高端逻辑分析仪产品简介(简版英文)

2022-10-17 07:08:32

逻辑分析仪原理及相关术语简介。逻辑分析仪的工作原理简介逻辑分析仪的组成结构如图1所示,它主要包括数据捕获和数据显示两大部分。由于数字系统的测试一般要观察较

2008-11-27 13:06:23 11

11 本文从延迟锁定环路(DLL)的线性模型出发,运用信号统计分析的方法,详细研究了延迟锁定环路的同步性能与相关区间、环路带宽与信噪比之间的关系,得出了采用窄相关可以显

2009-08-07 10:03:30 24

24 Altera 公司出品系列器件所用设计软件――Quartus®II,提供了一种其独有的优化方法:逻辑锁定(LogicLock)。本文介绍了一种在实际工程中应用逻辑锁定的方法,并加以仿真验证

2009-09-03 08:39:59 11

11 基于PLD芯片的时序逻辑设计与实现:原理图输入设计直观、便捷、操作灵活;1-1、原理图设计方法简介QuartusII已包含了数字电路的基本逻辑元件库(各类逻辑门及触发器),宏

2009-10-29 22:03:10 0

0 LogicLock功能演示本节旨在通过Quartus软件自带的工程实例——“lockmult”来熟悉Altera Quartus II逻辑锁定功能LogicLock的使用方法。在本节中,将主要讲解下面知识点。&#

2010-02-08 16:38:06 0

0

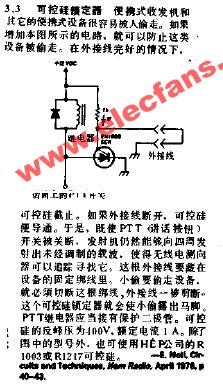

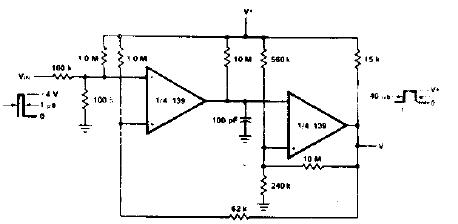

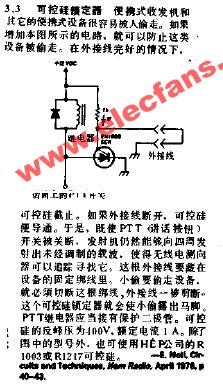

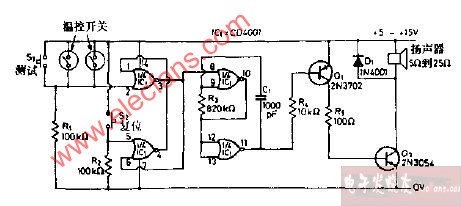

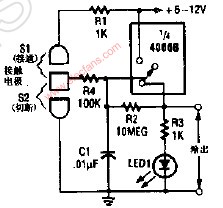

可控硅锁定器电路

2009-01-11 22:47:37 543

543

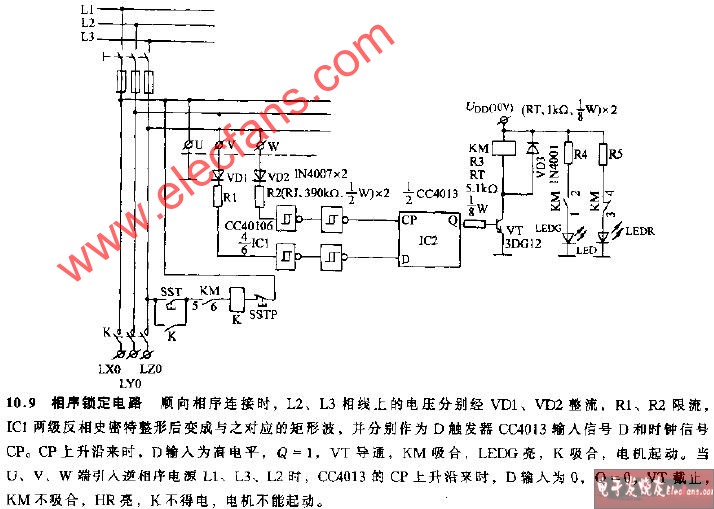

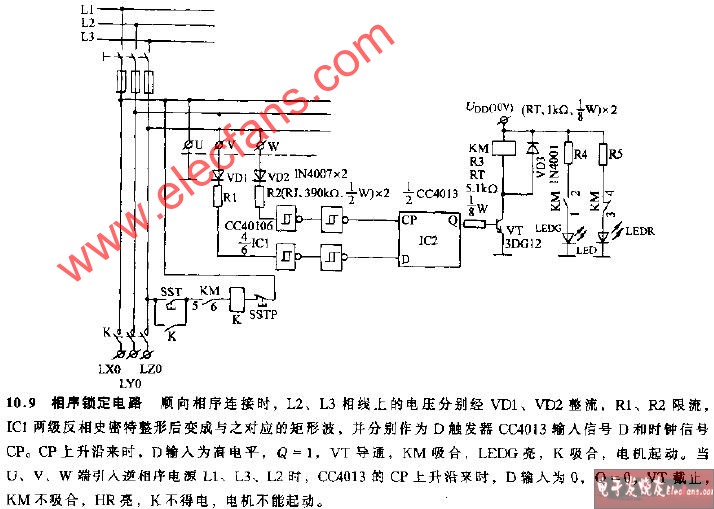

相序锁定电路

2009-02-17 20:28:39 747

747

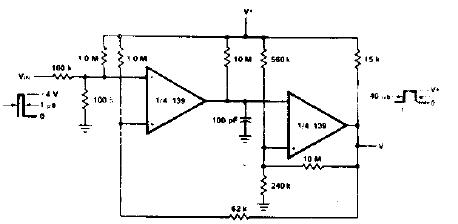

输入锁定的单穏触发器电路图

2009-04-06 08:43:18 333

333

800Hz单音锁定式锁定式火警电路图

2009-06-10 08:57:58 1664

1664

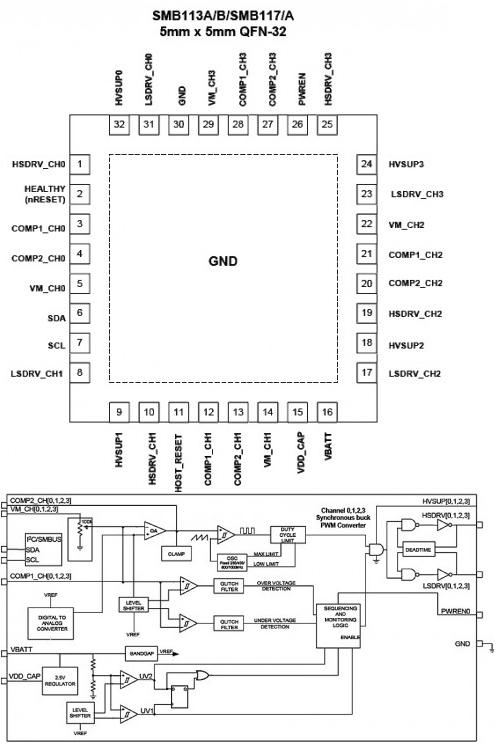

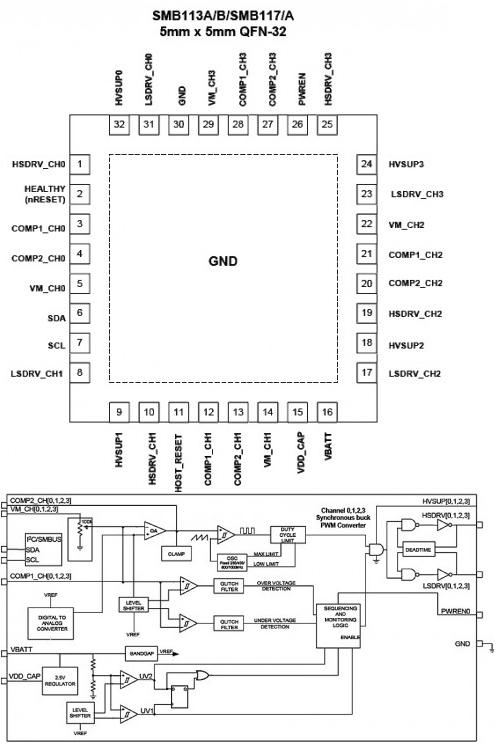

Summit Microelectronics发表两款锁定高功耗应用的新元件SMB113A和SMB117A

Summit Microelectronics发表两款锁定高功耗应用的新元件SMB113A和SMB117A,

2009-07-01 08:34:39 636

636

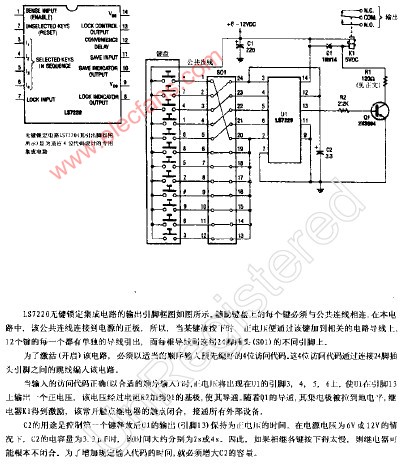

数字式输入锁定电路

2009-09-15 11:07:49 492

492

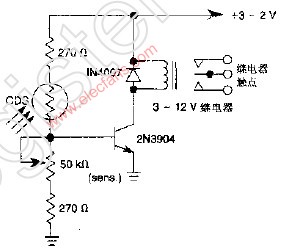

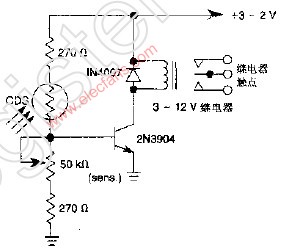

简单的非锁定式光电光开关

CDS光电管用来驱动

2009-09-22 17:07:58 624

624

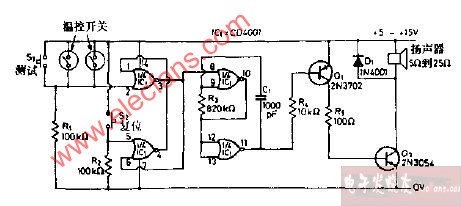

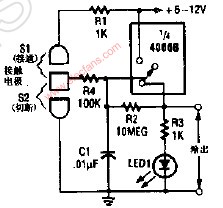

用CD4066B的锁定触摸开关

当

2009-10-09 16:30:29 1472

1472

硬盘逻辑结构简介

一. 硬盘逻辑结构简介

1. 硬盘参数释疑到目前为止, 人们常说的硬盘参数还是古

2009-10-11 12:15:40 1559

1559

各种逻辑电路简介

逻辑电路:

以二进制为原理、实现数字信号逻辑运算和操作的电路。分组合逻辑电路和

2009-11-24 13:27:04 2959

2959 常用逻辑门及其符号简介

2009-12-03 10:59:42 62570

62570 FPGA教程之频率简介

每个CPU都有一个工作频率,FPGA也不例外(当然,只有你的设计应该是时序逻辑),那该频率是

2010-03-24 10:41:03 4284

4284

PC-Based逻辑分析仪简介

逻辑分析仪是利用时钟从测试设备上采集和显示数字信号的仪器,最主要作用在于时序判定。由于逻辑分析仪不像示波器那样有许多电压等级,

2010-04-02 13:49:39 971

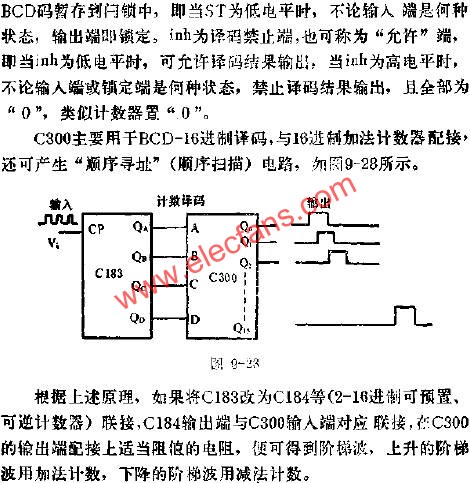

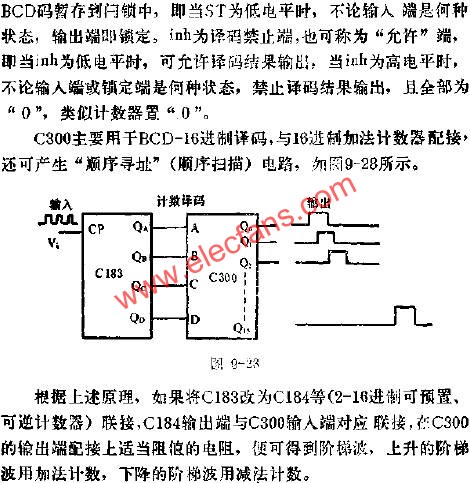

971 C300四位锁定4线-16线译码器的逻辑功能和外引线排列同美国RCA公司的CD4514可方便地进行互换.它的主要特点是带有

2010-10-20 10:43:33 2156

2156

首先介绍了光电跟踪仪锁定机构检测调试仪研制的必要性和紧迫性,接下来介绍了方位锁定机构的特点及主要功能是完成对设备方位锁定机构状态的检测,能够在单板上实现对方位锁定

2011-03-18 16:20:26 28

28 电子发烧友网核心提示: GAL是众多英文单词的缩写,分别涉及电子、物理、游戏等领域,但是在电子行业中指的是通用阵列逻辑(Generic Array Logic),是简单PLD其中的一种。电子发烧友

2012-10-12 14:16:33 5540

5540 可编程逻辑器件简介,相关详细学习。

2016-04-26 16:55:36 0

0 华清远见FPGA代码-LogicLock功能演示

2016-10-27 18:07:54 3

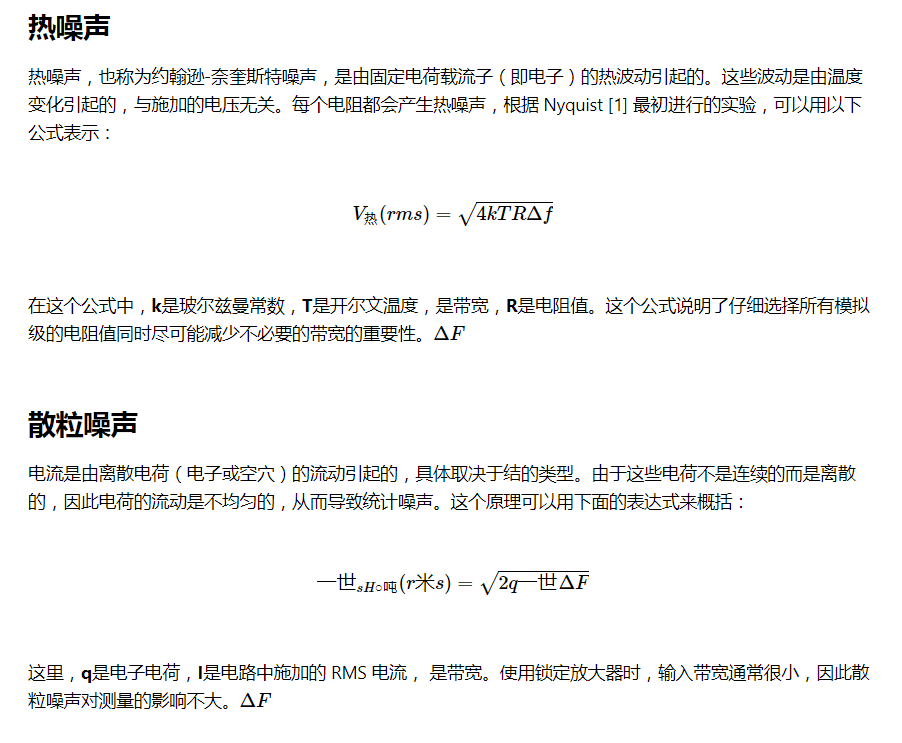

3 研究了锁定放大器的实现原理, 并根据该原理用 MATLAB的

SIMULINK工具箱对锁定放大器进行了建模和仿真。仿真结果表明

锁定放大器具有卓越的微弱信号检测能力。在实际测试中, 所设计的

锁定放大器也很好的完成了信号的检测和拾取。

2022-07-08 16:31:58 28

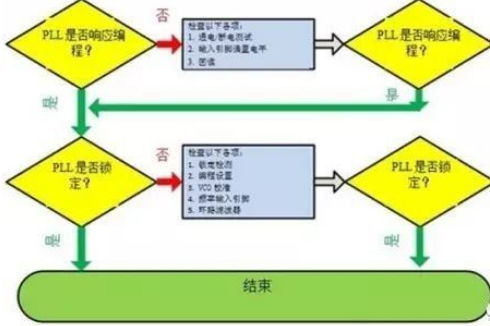

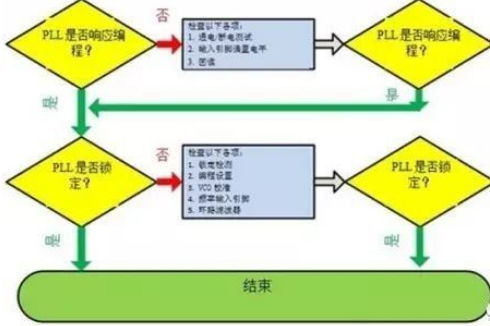

28 在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以下验证通行与建立锁定的程序,调试过程可以变得非常简单。第 1 步:验证通信 第一步是验证PLL响应编程的能力。如果PLL没有锁定,无法读回,则尝试发送需要最小量硬件命令工作的软件命令。

2017-04-08 01:56:13 881

881

在尝试将锁相环(PLL)锁定时,你是否碰到过麻烦?草率的判断会延长调试过程,调试过程变得更加单调乏味。根据以

2017-10-16 11:49:30 5147

5147

本文包含两部分内容:1)AXI接口简介;2)AXI IP核的创建流程及读写逻辑分析。 1AXI简介(本部分内容参考官网资料翻译) 自定义IP核是Zynq学习与开发中的难点,AXI IP核又是十分常用

2018-06-29 09:33:00 14957

14957

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17:00 6065

6065

PLL锁定有那些检测方法,它们特点是什么?一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测方式,判决方式简单,判断的结果只有锁定和非锁定两种情况。

2018-03-14 16:37:00 4972

4972

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短。

2018-05-11 15:14:34 10847

10847

蠢蠢欲动了这么久,美国又将目光锁定在了中国LED产业。

2019-04-24 11:39:43 3391

3391 本文针对Vivado中实现的逻辑锁定和增量编译进行的工程实例介绍,文中有对应工程的下载地址。友情提示:(1)增量编译只允许修改当前工程不超过5%的时候才有效,一般应用于较大工程添加修改

2019-07-06 10:32:42 6745

6745

哈希锁定模式是指用户在规定的时间段对于哈希值的原值进行猜测来支付的一种机制。简单讲,就是在智能合约的基础上,双方先锁定资产,如果都在有限的时间内输入正确哈希值的原值,即可完成交易。

2019-09-10 10:56:55 3917

3917 布局并保持fMAX性能。层次结构包含一个用于顶层设计的VQM文件和一个或多个用于底层模块的VQM文件。通过维护单独的VQM文件,您可以将各个模块放置到LogicLock区域中,以控制可编程逻辑器件(PLD)中的放置,并在将其他模块添加到项目中时保持模块的性能。

2021-01-15 14:38:00 11

11 时控开关锁定屏幕:就是把屏幕给上锁,无法对时控开关进行手动控制,以及修改删除定时时间。

2021-10-18 17:21:07 844

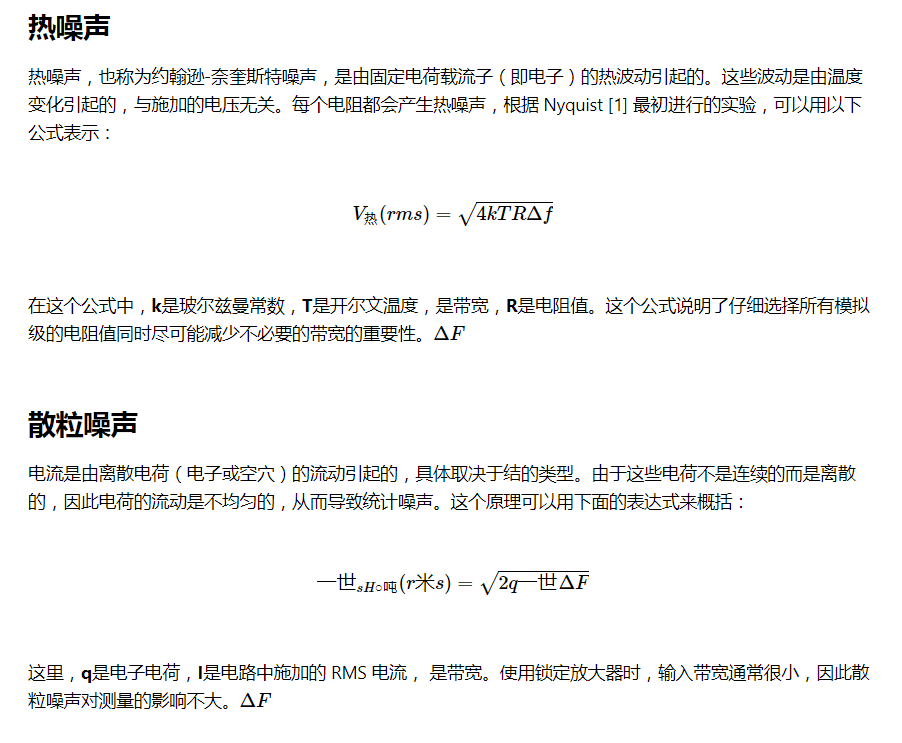

844 在本文中,我们将讨论市售锁定放大器的实用方面,包括不同类型的锁定放大器及其主要特性。

2022-04-25 16:33:13 1428

1428

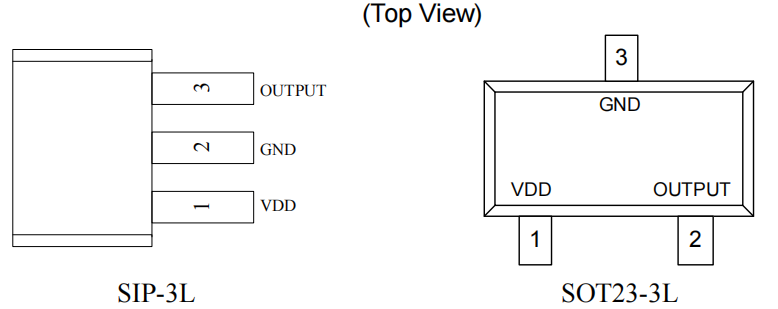

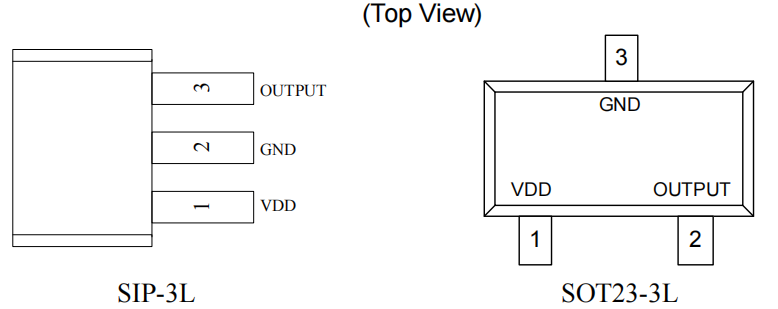

OCH184(霍尔效应锁定传感器)

2022-06-06 15:40:29 852

852

电子发烧友网站提供《高端逻辑分析仪产品简介(简版英文).pdf》资料免费下载

2022-10-14 10:22:19 0

0 如何解决锁相环无法锁定

2022-11-02 08:16:21 3

3 欠压锁定 (UVLO) 可防止下游电子系统在异常低的电源电压下运行,这可能导致系统故障。例如,当电源电压低于规格时,数字系统的行为可能不稳定,甚至冻结。当电源是可充电电池时,欠压锁定可防止电池因深度放电而损坏。

2022-12-16 11:47:43 1712

1712 举个简单的例子,假如一个250MHz的DLL,其正常锁定后的整个延时链(VCDL)的总延时为一个周期T,即4ns。但在某些特别情况下,VCDL可能延时2T,即8ns,这就发生了谐波锁定。这时候Loop虽然锁定在一个稳定状态下,然而却是一种错误情况。

2023-03-23 14:25:23 755

755

逻辑锁定功能可以将FPGA中的代码模块在固定区域实现,优化时序性能,提升设计可靠性。 增量编译功能,可以使设计更快速时序收敛,加快编译速度。

2023-05-25 11:22:11 800

800

怎样把PCI总线速度锁定 PCI总线速度锁定是指限制PCI总线传输速度的方法。当系统中出现某些硬件兼容性问题或者不稳定性问题时,锁定PCI总线速度可能是一个有效的解决方案。在本文中,我们将详细介绍

2023-09-02 15:12:39 1194

1194 当锁相环无法锁定时,该怎么处理的呢?如何解决锁相环无法锁定? 锁相环作为一种常见的电路设计,具有广泛的应用领域。然而,在一些情况下,由于种种原因,锁相环可能无法正常锁定,这时需要进行一系列的测试

2023-10-30 10:16:33 969

969 锁相环锁定时间取决于哪些因素?如何加速锁定? 锁相环(PLL)是一种常见的电路,用于稳定频率。PLL中的关键是相锁。相锁发挥着将输入频率与参考频率调整到相等的重要作用。在锁相环设计中,锁定

2023-10-30 10:51:18 899

899 “锁定”在cache中的块在常规的cache替换操作中不会被替换,但当通过C7控制cache中特定的块时,比如使某特定的块无效时,这些被“锁定”在cache中的块也将受到相应

2023-10-31 11:31:21 314

314

电子发烧友App

电子发烧友App

评论