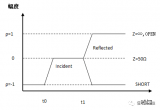

一、OTDR的工作原理:光纤光缆测试是光缆施工、维护、抢修重要技术手段,采用OTDR(光时域反射仪)进行光纤连接的现场监视和连接损耗测量评价,是目前最有效的方式。这种

2010-08-09 10:05:59 4902

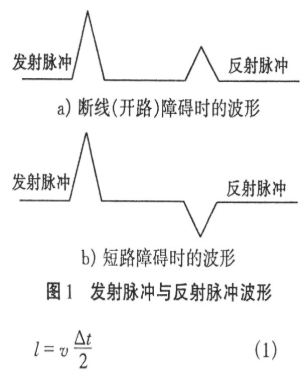

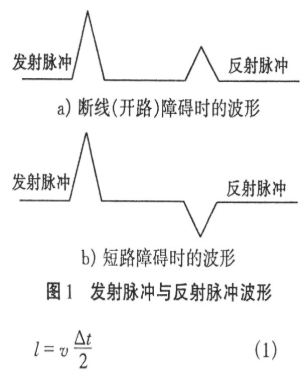

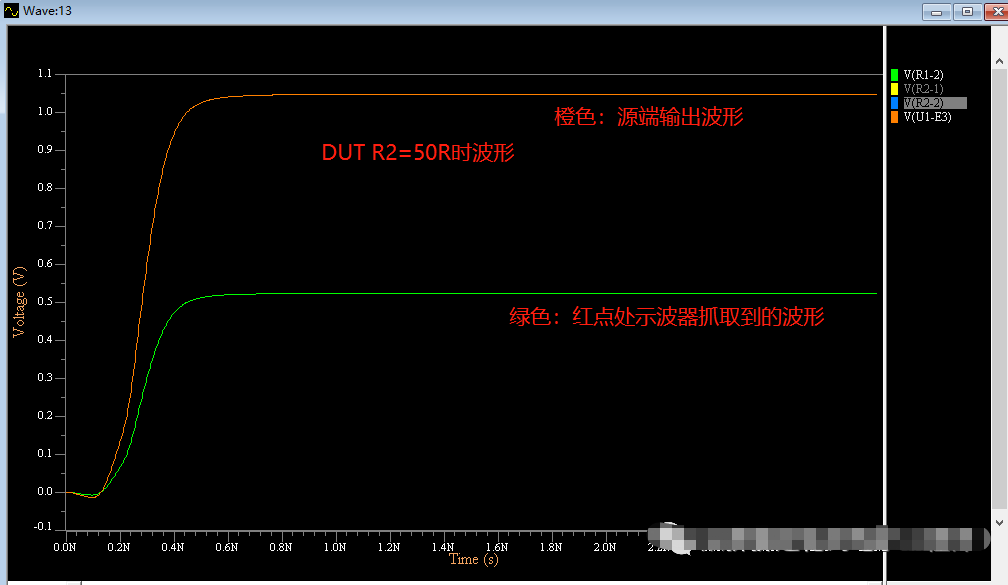

4902 电缆故障是通信行业中的常见故障,电缆测距是排除故障的前提条件,准确的电缆测距可以缩短发现故障点的时间,利于快速排除故障,减少损失。窄脉冲时域反射仪利用时域反射技术TDR(Time-Domain

2020-08-10 15:55:58 1067

1067

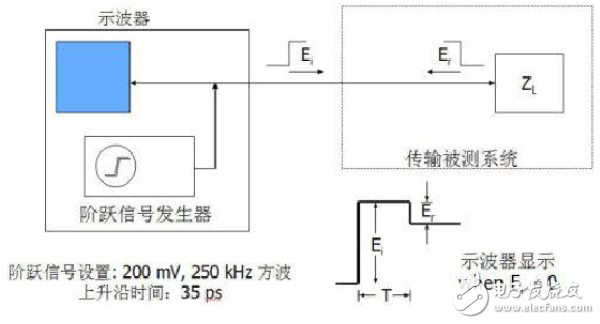

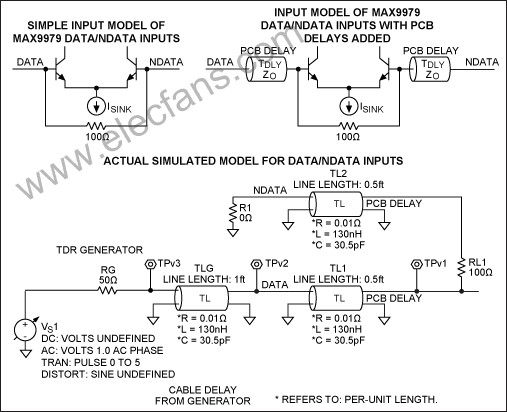

TDR(Time Domain Reflectometry)即时域反射技术,是一种对反射波进行分析的测量技术,主要用于测量传输线的特性阻抗,其主要设备为网络分析仪。

2023-09-13 09:39:54 1009

1009

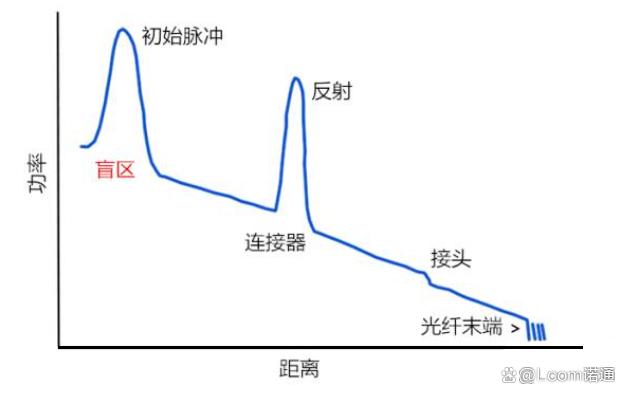

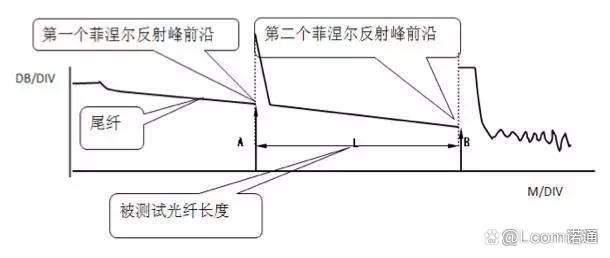

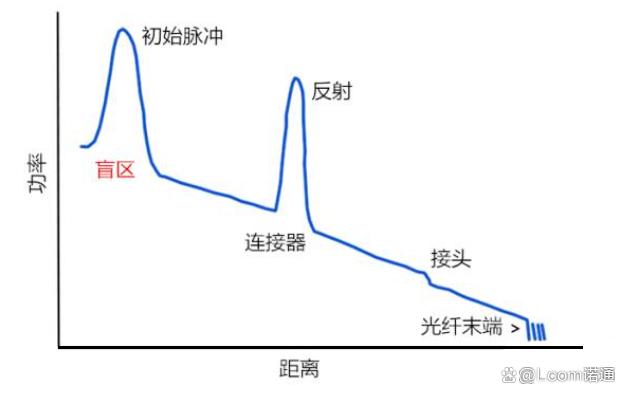

在使用光时域反射仪(OTDR)时,针对不同测试中的不同曲线,有着不同的分析要点,本文将围绕这些常见曲线,介绍其中的方法和解析。

2023-11-24 11:20:26 649

649

1818A时域反射仪操作和维修手册

2018-11-13 16:37:08

探头误差的方法,有助于提高传输延时测量精度。 分析方法 本文基于以下三个前提: 1.利用TDR (时域反射计)减小探头误差。TDR通常用来测量信号通路长度与阻抗变化的关系。TDR也是测量传输延

2012-04-17 15:30:38

测量传输系统中反射波与入射波的场强之比的仪器。早期的反射计仅限于测量两者的幅值之比。

2020-04-07 09:01:32

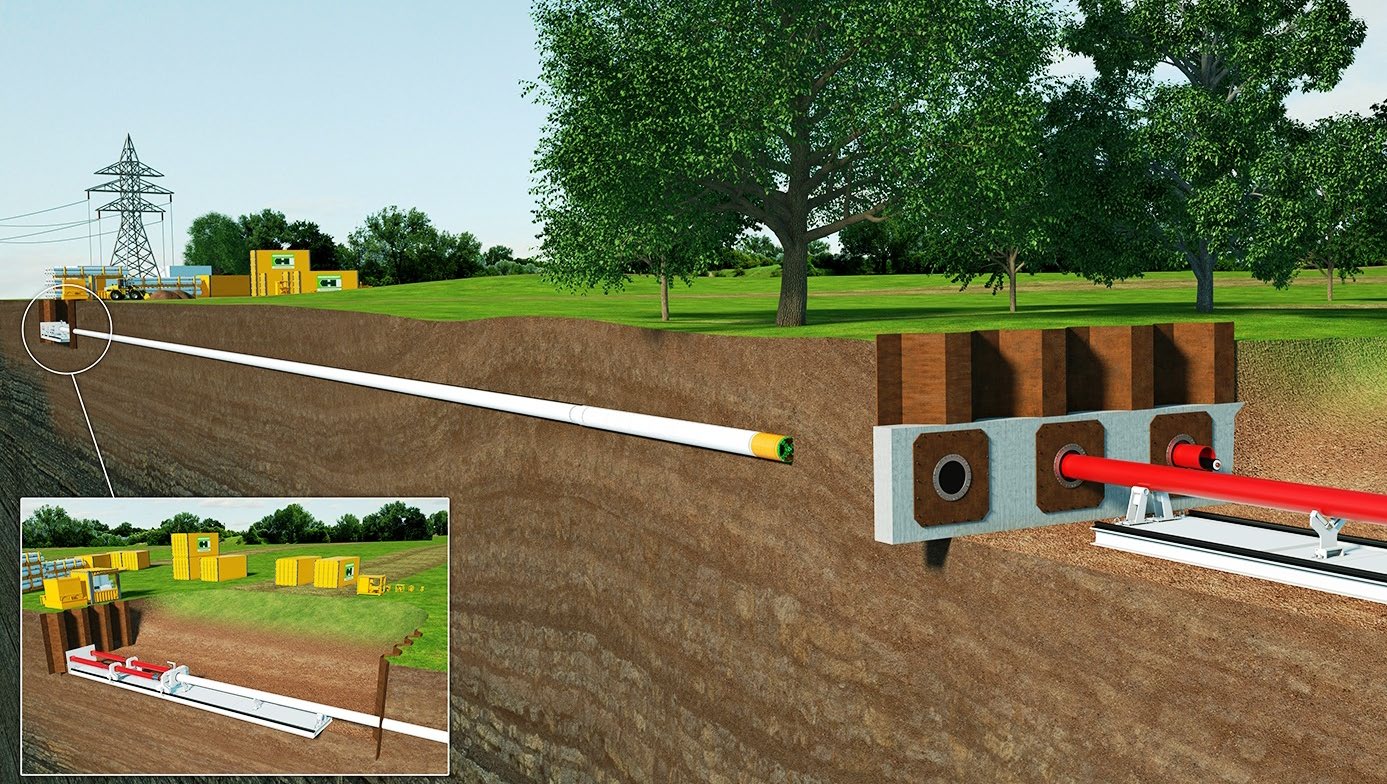

华天电力专业生产电缆故障测试仪,接下来华天电力为大家分享测量电缆故障的时域反射原理。时域反射(TDR)有时被称为“ 有线雷达 ”,因为它们都使用反射信号来确定距离。TDR沿着电缆发送信号脉冲。电缆

2019-01-17 10:59:58

时域反射计(TDR)提供了一种快速、准确的金属电缆故障定位方法。如果一根电缆至少有两个导体被电介质(即双绞线或多芯电缆)或导体和屏蔽(即同轴电缆)隔开,则可以使用时域反射的方法进行测试。时域反射将

2019-01-28 11:50:55

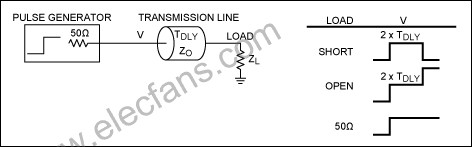

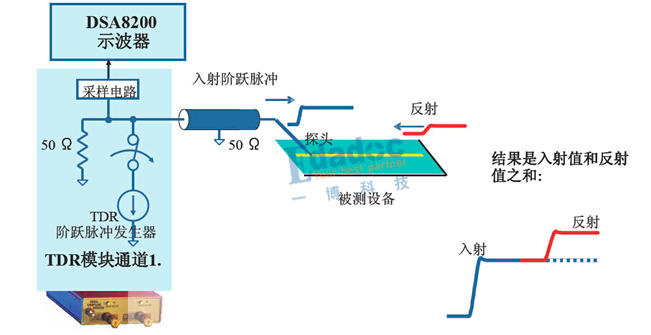

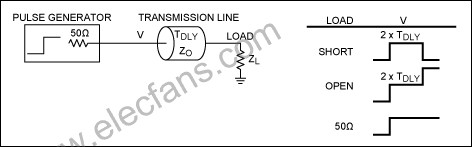

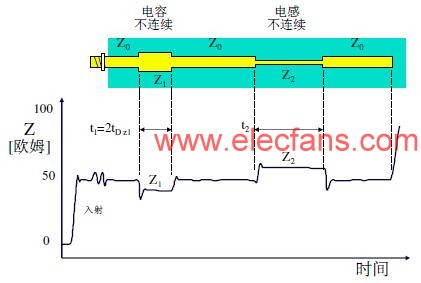

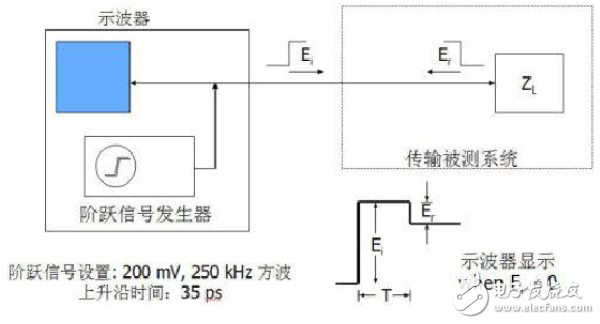

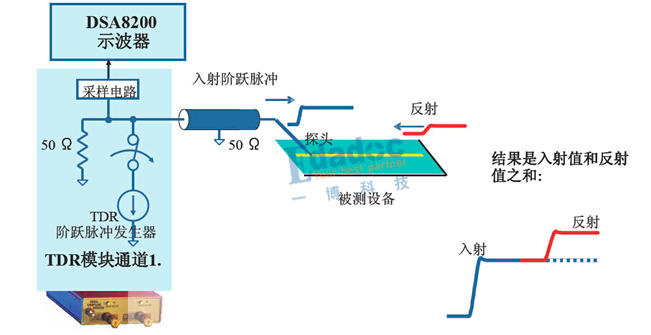

传统时域反射计工作原理时域反射计TDR是最常用的测量传输线特征阻抗的仪器,它是利用时域反射的原理进行特性阻抗的测量。图1是传统TDR工作原理图。图1时域反射计TDR工作原理

2019-07-01 08:23:02

时域反射法(Time Domain Reflectometry,TDR)是一种利用送入传输线的脉冲的反射能量来测量传输线阻抗的方法。当脉冲送入传输线时,脉冲以光在介质中的传播速度进行传播(通常为真空

2020-03-20 07:43:15

: 示波器,带宽超过50 GHz,可确保进行最精确的波形测量 眼图分析仪,用于发射机一致性测试 时域反射计/时域传输(TDR/TDT),用于高精度S参数阻抗分析 一键式操作简单方便后向兼容

2021-04-27 13:08:25

,同时接收模块采集反射信号的时域波形。电脉冲信号在导体中传输速度大约为2 * 10 8米/秒。所以如果需要测量达到1米的精度,那么要用100M以上宽带的示波器;如果需要测量达到1毫米的精度,那么要用

2014-09-04 19:27:38

YOKOGAWA:光时域反射仪 AQ7280 在光纤网络铺设和维护作业中,市场对现场测试 设备的可靠性和易用性需求正在不断攀升。为响 应这一需求,YOKOGAWA专门设计出全新的光 时域反射仪

2018-08-30 09:29:25

光时域反射仪:OTDR仿真软件 AQ7932 测量数据分析和报告创建工具。 AQ7932是一个应用软件,用于在PC上分析AQ7270和AQ7275 OTDR得到的波形数据并生成报告

2018-11-26 20:41:46

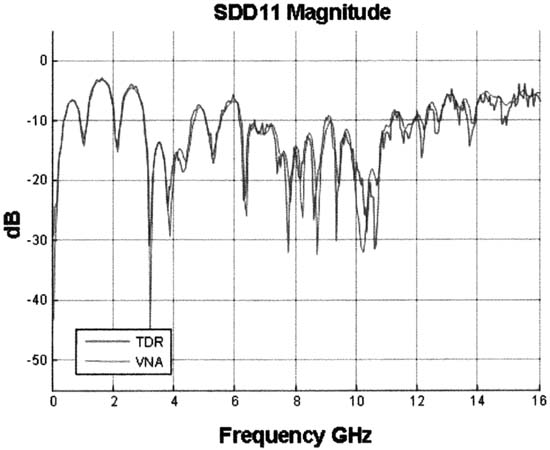

DomainReflectometry,简称TDR)或时域传输计(TimeDomain Transmission,简称TDT);频域测试仪器为矢量网络分析仪(Vector Network Analyzer

2018-09-17 17:32:53

与技术指标数字通信分析仪模式:示波器,带宽超过50 GHz,可确保进行最精确的波形测量眼图分析仪,用于发射机一致性测试时域反射计/时域传输(TDR/TDT),用于高精度S参数阻抗分析一键式操作简单

2021-03-13 14:15:56

改为阶跃脉冲发生器,从时域反射(TDR)和时域传输(TRT)参数导出S参数。最简单的一个物理同轴线连接点的二端口S散射矩阵见表达式(1),它是由输入端口和输出端口的入射波和反射波来定义的四个Sij参数

2019-07-18 07:01:25

测量并刷新仪表屏幕上显示的测量结果能够快速进行测量并刷新所显示的测量结果可以使产品的设计效率更高并提高生产吞吐量。 传统上,基于采样示波器的时域反射计(TDR)一直用于电缆和印刷电路板的测试。由于这种

2011-09-06 14:07:03

如何用LOTO示波器TDR方法测试电线长度?TDR也就是时域反射(Time-domain reflectometer),它可以通过观察导线中反射回来的电信号波形对导线长度进行测量,或者对传输

2022-03-23 16:32:39

`光时域反射仪(OTDR) 是光纤线路测试和验收中非常重要的工具,借助于OTDR,技术人员能够看到整个系统轮廓,识别并测量光纤的跨度、接续点和连接头。在诊断光纤故障的仪表中,OTDR是最经典的,也是

2015-02-09 15:56:54

: 0.5mm-2.54mm弹簧探针,能够独立进行 Z 轴移动描述N1021B 差分时域反射计和时域传输探头套件详细介绍N1021B 是一款符合人体工程学设计的手持式探头,可以将 TDR/TDT 模块(例如

2021-09-23 14:44:29

MT9083A8 OTDR 光时域反射仪品牌日本安立型号MT9083A8测量范围0~100KM测量精度1m电源电压220(V)尺寸284*200*77(mm)重量2.9(kg)用途光纤事件和断点测试

2019-04-15 08:23:16

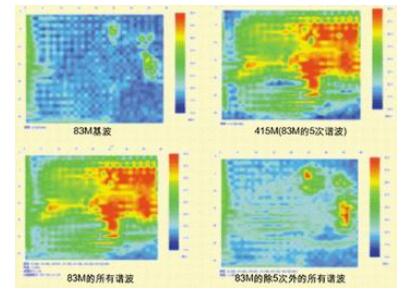

至少可以缩短一个数量级。本文还讨论了该技术中用到的信号处理算法和利用时域电磁干扰系统(TDEMI)进行实际测量得到的测量结果。随着新技术的飞速发展,新的电子产品层出不穷。如何使电子产品满足电磁兼容要求

2019-04-26 06:21:53

1.引言微波测量方法是将电磁波作为探测束入射到等离子体中,对等离子体特性进行探测,不会对等离子体造成污染。常规微波反射计也是通过测量电磁波在等离子体截止频率时的反射信号相位来计算等离子密度。当等离子

2019-06-10 07:36:44

光纤长延时器件的特点与应用 光纤通信在数字通信领域已得到相当广泛的应用,且得到了快速的发展。由于光纤通讯具有带宽宽、损耗低、抗干扰、保密性好、重量轻、性能价格比高等优点,近年来通过光纤传输

2019-06-03 06:35:26

: 0.5mm-2.54mm弹簧探针,能够独立进行 Z 轴移动描述N1021B 差分时域反射计和时域传输探头套件详细介绍N1021B 是一款符合人体工程学设计的手持式探头,可以将 TDR/TDT 模块(例如

2021-09-10 16:21:59

的光时域反射仪就成为了保证工程质量与线路传输性能的关键。日本横河电机株式会社(横河)的最新型号AQ7275 OTDR模块采用良好技术,以其出色的性能和独特的设计深受广大工程技术人员的青睐。不论对于传统

2020-04-14 23:04:24

横河测试测量OTDR光时域反射仪 AQ7277是RFTS(远程光纤测试系统)的一个OTDR模块,沿用了AQ7275高性能OTDR的先进技术。 横河远程光时域反射仪AQ7277的特点如下

2020-04-23 15:26:27

时域反射(TDR)是易于使用的测试仪器,通常与查找电缆和天线中的故障相关。它们的工作方式很简单:将具有快速上升时间的脉冲发送到被测电缆中,并测量反射阻抗信号,这些反射信号通常是由于线路中断或干扰而在

2020-11-13 13:47:11

时域中测量网络特性的方法就是对被测件进行瞬态响应的测试,即在被测网络输入端加入理想的冲击函数或阶跃函数信号,观察其输出波形和反射波形的畸变情况,从而判断网络的传输特性和反射特性。网络分析仪除主要从频域

2009-11-04 16:55:10

请教一下关于脉冲反射(行波反射)在simulink中仿真的问题。根据几篇硕士论文的指导,我利用里面列出的simulink模型进行脉冲反射法的研究。即利用行波在波阻抗发生变化处发生波反射的原理。但是我

2014-07-27 21:18:59

任何博士都能说出Agilent 86100A Infiniium DCA时域反射仪的等效模型是什么。实际上我想测量高达12Ghz的时域参数,所以请告诉我以下型号的等效型号是什么:86100A

2019-07-24 10:39:33

时域反射仪测试阻抗(电阻)的变化,这可能是由电缆故障,安装不当,电缆类型变化或电缆中的水引起的。安装人员使用金属时域反射仪对所有类型的双绞线和同轴电缆进行故障排除和测量。TDR沿电缆传输电脉冲,当

2019-02-28 10:49:18

、驻波比或时域格式来显示反射和传输参数的任意组合,便于使用的专用功能键能迅速访问各个测量功能,榀以利用达4个刻度格子在分辨率的LCD彩色显示器上以重叠或分离屏面的形式来观察测量结果为了驱动更大的外部

2016-05-26 08:05:12

于测量光纤衰减、接头损耗、光纤故障点定位以及了解光纤沿长度的损耗分布情况等,已经成为光缆施工、维护及检测中必不可少的工具。一、 光时域反射仪的应用领域测试光纤光缆的长度,均匀性传输损耗,光纤的传输衰减

2021-01-30 10:38:15

仪CSF15系列土壤水分传感器基于时域反射TDR原理,是一种电介质型传感器,此原理有较强的独立性,其结果与土壤类型、密度、温度基本无关。因此当土壤中的水分含量变化时,土壤的介电常数也随之发生

2021-12-10 15:58:03

lecroy力科T3SP15D差分时域反射计T3SP10D(10 GHz)和T3SP15D(15 GHz)通过真正的差分信号激励DUT,TDR提供50 ps(T3SP10D)和35 ps

2022-08-08 16:32:24

;示波器主机配备 1 到 4 个 N1055A 时域反射仪(TDR)/时域传输(TDT)模块,打造经济型

2022-10-09 16:55:18

利用多模光纤缠绕钢绳式传感阵列网络,对智能材料与结构的受力,应变等状态参量进行监测和估计,并采用光时域反射(OTDR)技术实时处理并行分布式传感信号,给出了识别结果。

2009-06-29 10:34:27 9

9 特性阻抗测量课程:第一部: 第一部: TDR时域反射测量阻抗原理概述 第二部: 传输线理论概述 第三部: TDR阻抗测量的分辩率与误差 第四部: 使用IPC-TM-650标准去除阻

2009-10-17 17:18:28 73

73 加拿大EXFO FTB-200光时域反射仪FTB-200是加拿大EXFO公司的新产品,是针对多层和多介质测试而设计的超强型模块化平台。FTB-200 包含两个现场可更换模块的插槽,可测试物理层、传输

2023-04-27 16:18:49

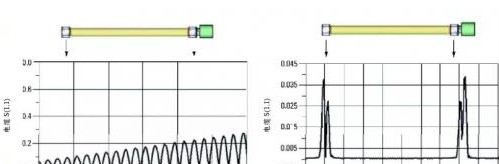

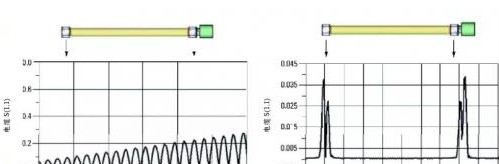

倒谱域滤波能够有效的滤除多次反射回波。该文将倒谱域滤波方法引入TDR(Time Domain Reflectometry)波形分析,通过将TDR 波形在倒谱域内做滤波,滤除多次反射回波对时域波形的影响,进

2010-02-10 12:06:54 12

12 超宽带(UWB)冲激雷达目标探测中时域天线阵列波束延时控制扫描是通过天线阵列单元间精确的延时控制实现的。在介绍UWB时域波束延时控制扫描原理的基础上,研制了用

2010-03-05 15:08:52 30

30 综述当您用Agilent 54754A TDR模块或任何其它TDR仪器进行TDR测量时,您需要有接至被测装置的适用探头。我们这种通用的TDR探头套件为您提供进行精确TDR测量所需的一切,无论测量的

2010-07-26 11:26:47 13

13 时域反射和传输的S参数测量

在频域、时域、阻抗域三种电学基本特性测试测量仪器中,以阻抗域测试测量仪器所用电路结构最复杂、测试操作最费时间

2009-08-18 10:45:33 3455

3455

安捷伦发布E5071C与TDR相结合的高速串行互连分析综合处理方案

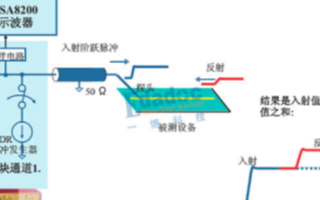

安捷伦科技公司宣布推出适用于 Agilent E5071C ENA 网络分析仪的时域反射(TDR)应用软件选件。E5071C 与 TDR

2010-03-04 10:14:09 1769

1769 TDR原理

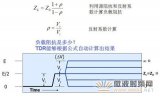

TDR测试方法中,沿信号通路传输高速信号边沿,并观察其反射信号。反射能够说明信号

2010-03-17 08:44:29 2672

2672

TDR概述原理

TDR是时域反射计英文(Time Domain Reflectometry)的第一字母缩写– 可以直观显示和测量电路反射的电能(PCB,

2010-08-05 14:41:12 53073

53073

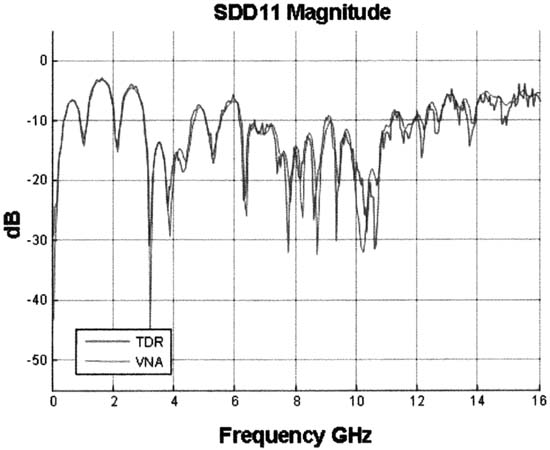

本文对比了 VNA TDR (E5071C-TDR)和示波器 TDR的测量限制与精度。结果显示,在 E5071C-TDR上执行的 TDR测量与在传统 TDR示波器上执行的测量相关。此外,我们还讨

2011-09-06 11:00:22 3461

3461

提出了一个考虑FP 效应的半导体材料参数测量方案。利用该方案可以在时域波形中,截取多个反射回峰,以提高材料参数提取的精确度。另外,考虑到多重反射对样品厚度的准确性

2012-04-26 14:19:15 32

32 光时域反射仪AQ7275基本操作界面介绍。

2012-08-31 15:46:35 3

3 光纤传感资料,文章介绍了基于双光束干涉的相位敏感光时域反射技术,并描述了相应的光路

2016-05-27 17:20:16 4

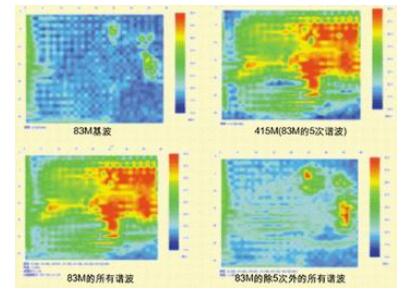

4 调试PCB的传统工具包括:时域的示波器、TDR(时域反射测量法)示波器、逻辑分析仪,以及频域的频谱分析仪等设备,但是这些手段都无法给出一个反映PCB板整体信息的数据。本文介绍用EMSCAN电磁干扰扫描系统获得PCB完整电磁信息的方法,并介绍如何利用这些信息来帮助设计和调试。

2016-12-29 11:22:30 2217

2217

LFT 液位传感器采用TDR 时域反射技术(Time Domain Reflectometry),传感器的电子装置产生低电磁脉冲,发射到同轴探杆中,并沿此探杆传送。当此脉冲到达待测量液体的表面

2017-10-20 18:02:01 20

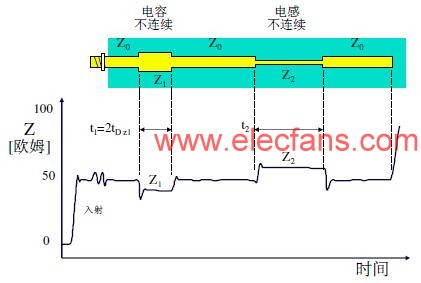

20 矢量网络分析仪(以下简称矢网)的时域测试功能是模拟时域反射测试(TDR)的一种测试方式,与频域响应测试不同,时域测试反映的是被测件在时域的响应,因此可以准确的判断传输线的阻抗不连续的位置及其

2017-11-10 17:23:00 11

11 传统时域反射计工作原理 时域反射计TDR是最常用的测量传输线特征阻抗的仪器,它是利用时域反射的原理进行特性阻抗的测量。 图1是传统TDR工作原理图。 图1时域反射计TDR工作原理 TDR包括三部

2017-11-23 03:30:00 769

769

安捷伦科技公司(NYSE: A)(Agilent)推出可用于Agilent 86100D DCA-X平台的Agilent N1055A 35/50GHz(8ps)时域反射和传输模块。利用该模块

2017-12-05 20:22:23 523

523 天线测试技术发展到目前,其测量方法已经涉及到频域、时域、空域及数字域。但常用的测量方法仍然以频域为主,而频域测试的指标只是得到该指标对应于频率的综合响应,而无法分析和区分其他因素如接头,传输线,馈电

2017-12-06 07:54:32 4002

4002

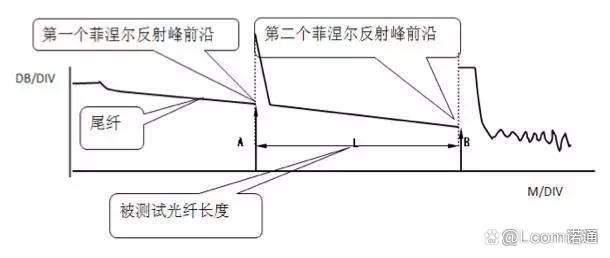

光时域反射仪是通过对测量曲线的分析,了解光纤的均匀性、缺陷、断裂、接头耦合等若干性能的仪器。它根据光的后向散射与菲涅耳反向原理制作,利用光在光纤中传播时产生的后向散射光来获取衰减的信息,可用于测量

2017-12-27 17:57:51 10703

10703 光时域反射仪是光纤线路测试和验收中非常重要的工具,借助于OTDR,技术人员能够看到整个系统轮廓,识别并测量光纤的跨度、接续点和连接头。在诊断光纤故障的仪表中,OTDR是最经典的,也是最昂贵的仪表。那么怎么样选择光时域反射仪呢。使用时要注意什么呢?如下所述

2017-12-28 08:44:03 2773

2773 光时域反射仪全球主要品牌有:美国安捷伦,加拿大EXFO,日本安立(收购网泰),日本横河(原日本安藤),AT800系列是由艾特(AETeP)等等如下所述

2017-12-28 10:07:04 26121

26121 时域反射计技术包括产生沿传输线传播的时间阶跃电压。用示波器检测来自阻抗的反射,测量输入电压与反射电压比,从而计算不连续的阻抗。

2018-01-24 14:52:54 23612

23612

时域反射技术,一种对反射波进行分析的遥控测量技术,在遥控位置掌握被测量物件的状况。

2018-01-24 15:11:55 6483

6483

TDR(时域反射)测量可以为一根电缆或 PCB(印制电路板)走线的信号完整性提供直接描述,以及分析 IC 的性能与故障。TDR 测量沿电缆或 PCB 走线发送一个快速脉冲,并显示返回的反射,用于表示阻抗的变化。

2018-02-08 20:01:20 1520

1520 时域反射法,TDR,线缆故障测试解决方案

2018-05-13 10:24:31 22

22 在频域、时域、阻抗域三种电学基本特性测试测量仪器中,以阻抗域测试测量仪器所用电路结构最复杂、测试操作最费时间、成套价格最高。

2018-11-01 17:37:35 8398

8398

受控阻抗印刷电路板(PCB)通常包括测量“试样”,其通常包括6英寸长的样品迹线,并构造为印刷电路板面板的一部分。测量它们以确保PCB叠层和PCB传输线的精度。这些试样以及实际的PCB信号走线,互连和电缆通常使用时域反射仪(TDR)测量。 TDR通常是一种昂贵的大型仪器,包括高速边沿脉冲和采样示波器。

2019-09-15 15:37:00 2444

2444

光时域反射仪是通过对测量曲线的分析,了解光纤的均匀性、缺陷、断裂、接头耦合等若干性能的仪器。它根据光的后向散射与菲涅耳反向原理制作,利用光在光纤中传播时产生的后向散射光来获取衰减的信息。

2019-12-18 11:26:31 4927

4927 TDR (Time Domain Reflectometry)时域反射技术的原理是,信号在某一传输路径传输,当传输路径中发生阻抗变化时,一部分信号会被反射,另一部分信号会继续沿传输路径传输。TDR

2021-07-24 17:02:11 2311

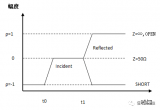

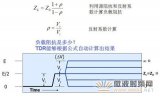

2311 测试信号的运行特征参考图2所示。由阶跃源发出的快边沿信号注入到被测传输线上,如果传输线阻抗连续,这个快沿阶跃信号就沿着传输线向前传播。当传输线出现阻抗变化时,阶跃信号就有一部分反射回来,一部分继续

2020-12-18 10:28:00 4

4 天线测试技术发展到目前,其测量方法已经涉及到频域、时域、空域及数字域。但常用的测量方法仍然以频域为主,而频域测试的指标只是得到该指标对应于频率的综合响应,而无法分析和区分其他因素如接头,传输线,馈电

2020-08-20 18:50:00 0

0 Anritsu是世界领先的测试和测量设备、设备和系统制造商。Anritsu涉及的主要领域包括有线和无线通信系统、移动和知识产权网络、超高频和红外测试和测量设备、一般测试等。 Anritsu光时域反射

2020-08-18 09:50:22 650

650 网络分析仪即可以测量频域特性也可以测量器件的时域特征,测量的时候给被测器件输入一个正弦波激励信号,然后通过计算输入信号与传输信号(S21)或反射信号(S11)之间的矢量幅度比得到测量结果。在测量

2020-08-21 16:28:16 2608

2608 VNA 的低通时域模式是对传统 TDR 测量方式的模拟,并提供阶跃信号和冲击信号两种激励方式。

2020-08-21 16:10:01 4002

4002

TDR是英文Time Domain Reflectometry 的缩写,中文名叫时域反射计,是测量传输线特性阻抗的主要工具。TDR主要由三部分构成:快沿信号发生器,采样示波器和探头系统。

2020-09-10 09:28:42 11881

11881

TDR产生一个阶跃信号到待测器件中,会产生入射波,入射波经过时延TD之后在待测器件中遇到阻抗不连续的地方,又会产生发射波,反射波将会叠加在入射波上,再经过时延TD到达TDR的输出端。

2021-04-12 10:49:54 18700

18700

OTDR是Optical Time-domain Reflectometer光时域反射仪,是光纤测量中主要的仪器,用于精确排除光纤故障与诊断,是光缆施工、维护及监测中必不可少的工具,也被称为光通信

2020-11-05 12:13:15 6003

6003 光纤反射器的工作原理主要是利用光纤光栅将OTDR发来的测试光脉冲以接近100%的反射率反射回去,而正常的无源光网(PON)系统工作波长由于不满足光纤光栅布拉格条件则以很小的衰减通过反射器。这样

2020-11-04 16:42:31 9069

9069 网络,具有一定的风险和不稳定性,为了保证光纤通信的顺利运行和安全,需要开发一种能精确测量出光纤通信特性的工具或者是仪器。为适应光纤通信中对光纤诊断的要求,产生了以背向瑞利散射为测量信号的光时域反射计(Optical

2021-06-15 09:21:20 2479

2479

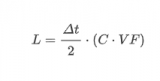

。 时域反射计的一个用处是可以用来测量电缆(双绞线、同轴电缆)的长度。 时域反射计大概长这样: 时域反射计 我们可以利用上一个实验 自制快速边沿脉冲发生器 中制作的脉冲发生器和一台示波器组成一套便宜的时域反射计设备,来测量导线的长度。 下面我们讲一下使用 TDR 测量导

2021-11-09 11:10:53 4793

4793

。 时域反射计的一个用处是可以用来测量电缆(双绞线、同轴电缆)的长度。 时域反射计大概长这样: 时域反射计 我们可以利用上一个实验 自制快速边沿脉冲发生器 中制作的脉冲发生器和一台示波器组成一套便宜的时域反射计设备,来测量导线的长度。 下面我们讲一下使用 TDR 测量导

2021-11-09 11:12:45 3083

3083

光时域反射仪(OTDR)是用于表征光纤性能的光电仪器。OTDR是电子时域反射仪的光学等效设备。

2022-09-30 09:31:06 1494

1494 耦合线的反射因子的大小在任何一点上都必须小于0.1。这包括反射测量和随后记录的FFT (时域函数,TDR)。

2022-10-11 11:28:35 2617

2617 用于测量信号路径质量的时域反射 (TDR) 技术

2022-11-15 19:49:54 6

6 2022-11-18 08:27:30 1

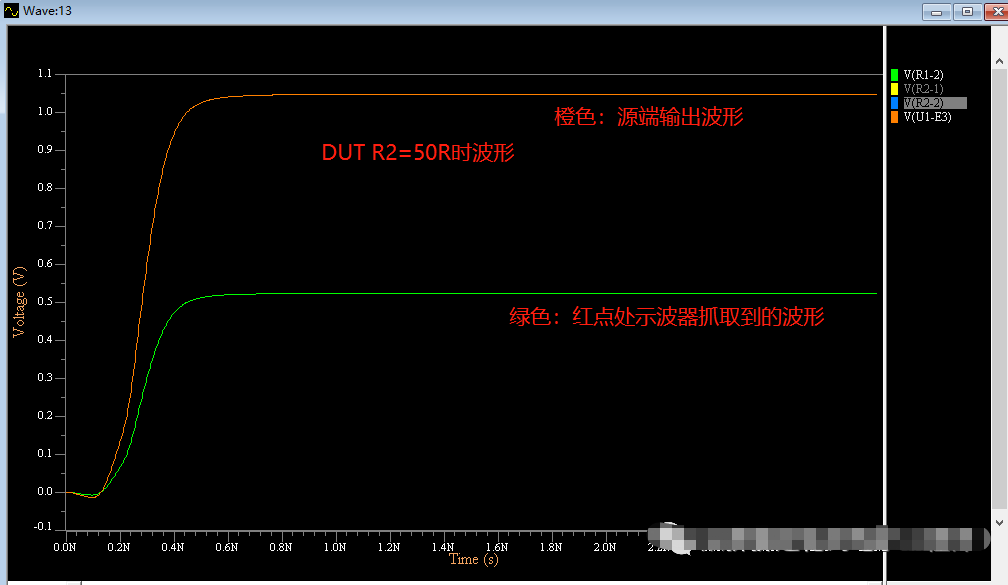

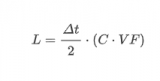

1 TDR称为时域反射计,可以用来测量本身没有电压源的无源互连线特性。下图是TDR的内部结构。源端输出一个35ps~150ps的快速上升沿信号。信号经过一个50R的校准电阻和一段很短的50R同轴电缆线,到达设备的前面板连接端子。此连接端子连接到DUT(待测无源传输线)。高速采样放大器测试红色点的电压值。

2023-04-15 16:03:44 602

602

不想错过我的推送,记得右上角-查看公众号-设为星标,摘下星星送给我 矢量网络分析仪是一种高精度的电子测量仪器,可以用于测量电路的传输特性。在测量TDR时域阻抗时,需要使用矢量网络分析仪和相应的测量

2023-04-18 10:03:47 2722

2722 TDR手持探头主要用于阻抗测试,可以测量信号线路上的阻抗变化和反射情况。通过分析测试结果,用户可以评估信号线路的质量和匹配情况。此外,TDR手持探头还可用于故障检测,例如开路、短路等问题的定位。

2023-06-15 14:29:38 269

269

TDR也就是时域反射(Time-domainreflectometer),它可以通过观察导线中反射回来的电信号波形对导线长度进行测量,或者对传输导线的阻抗特性进行分析评估。我们经常会碰到的TDR

2022-05-27 00:00:00 1056

1056

本方案通过高频采样示波器搭配高频差分探头进行高速差分阻抗测试,利用时域反射(TDR)的原理,向被测DUT注入一对差分脉冲信号,通过信号在线缆上的反射特性来检测线路中的故障或不匹配。当一个突变(例如

2023-08-05 08:35:31 523

523

时域反射计定位线缆故障METRACABLE TDR——诊断和精确定位铺设电缆和导线的缺陷和故障

2023-08-30 13:23:34 297

297

TDR是时域反射计,是基于时域的一种阻抗测量和仿真方法,通过测量电压来测量阻抗。

2023-09-18 10:18:33 617

617

光时域反射仪(OTDR)在检测光纤链路时,由于反射的影响,在一定距离(或时间)内不能检测或准确定位光纤链路中的事件点和故障点,这里的距离就是我们所说的盲区。

2023-11-24 09:49:38 439

439

电子发烧友App

电子发烧友App

评论