诺基亚近日宣布,他们和美国运营商U.S. Cellular共同测试了基于28GHz的5G信号技术,速率高达5Gbps(所用手持终端未知),延迟低于2ms,可以同步承载6路4K高清视频流媒。

2016-10-15 08:52:03 647

647 、电子对抗、图像处理、声纳等高速实时信号处理任务提供可靠的硬件保障。一、板卡特点1、板载4片C6678芯片和1片K7FPGA,为业内最大处理能力单板;2、成熟、稳定、灵活的驱动库、算法库,用户快速上手;3

2015-09-18 14:50:02

万物互联,占领先机,跻身潮头之上!大会设置以下三大技术板块,覆盖当前移动通讯和电子网络设备从仿真设计到调试测试的话题。涵盖的方向包括:5G、物联网、车联网、器件及模块设计测试、高速数字电路、光通讯等

2017-08-11 14:43:49

,“当然,2018年会有5G试运行网络提供高速移动通信服务,不过那时候能够买得起5G手机的人非常少。”虽然离5G真正实现尚有很长时间,但业界需要认真审视5G技术,以跟随发展到步伐。下面我们就从芯片、工艺、测试和封装等角度来详细分析一下5G技术现状。”

2019-06-19 08:14:33

5G射频测试技术白皮书详解

2021-01-13 06:33:58

5Gbps高速测试系统的基本技术有哪些?

2021-05-28 07:02:17

芯片测试需要掌握的技术,来源:基业常青经济研究院从IDM到垂直分工,IC产业专业化分工催生独立测试厂商出现。集成电路产业从上世纪60年代开始逐渐兴起,早期企业都是IDM运营模式(垂直整合),这种...

2021-07-28 08:06:50

100Gbps速率,成品的电气性能测试是必不可少的重要环节,包括时域和频域的一系列参数,以判断线材、PCB走线乃至制造工艺(如裁缆、分线、焊接等)是否符合要求。高速多通道DAC产品测试过程繁杂,人工

2017-04-18 15:47:04

测试精度。在未来的互连设计中,由于信号工作频率提升,工作重点将向芯片封装转移,相关的测试和建模技术将成为工作重点。 作者:张坤

2009-10-13 17:45:09

测试中,主要应考虑减小地线长度,以避免Pigtail耦合入噪声,降低测试精度。在未来的PCB互连设计中,由于信号工作频率提升,工作重点将向芯片封装转移,相关的测试和建模技术将成为工作重点。

2015-01-07 14:27:49

高速数据采集显示系统目前已在数字存储示波器、逻辑分析仪等测试仪器中得到广泛应用。它的关键技术是高速ADC技术、数据存储和实时显示技术。对高速数据采集系统存储子系统的性能要求:一是高速性,现在高速

2016-04-16 08:42:22

DS100RT410)。这不仅可帮助您直接从重定时器中读取眼状图,获得信号质量的实时影像,同时还有助于调节通道。另一个办法是,使用精心布局的技术移动小于5Gbps的较慢信号,然后在信号需要传输时,再进一步将其

2018-09-13 10:02:04

我有一个外围设备,使用CyPress CX3作为桥集成电路,我们正在进行EMC测试提交。我们需要知道在CX3中使用的最高时钟频率,因为它支持在5Gbps的UB3.1 GEN1,我假设它有一个时钟运行

2018-12-04 11:47:40

你好,我有一个小疑问:当通过项目部分时,FX3芯片与32位GPIF或16位GPIF工作在100 MHz的时钟速率和最大传输速度为5Gbps。在100 MHz的32位是3.2 Gbps。那么,5

2018-09-26 16:43:51

请问,我想用HMC311ST89对速率为:5Gbps码型为:“1000” 的归零信号进行放大,是否可行?

2023-11-23 06:57:41

沟道高速IGBT及场阻技术

2023-03-28 12:56:28

TIA和4个光电探测器,市场上一些模块还包括光复用/解复用器件。这进一步增加了成本并降低了可靠性。MACOM开发出可以在单波长上传输100Gbps的技术,这使100G模块内的器件数量大大减少。如上图可以

2017-11-30 11:18:44

随着SerDes芯片集成度,复杂度,传输速率的不断提高,传统的自动化测试系统已经无法满足SerDes测试速率需求。为解决该测试难题,通过Nautilus UDI方案的导入,成功得实现了32 Gbps

2021-05-10 06:58:55

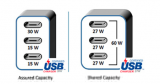

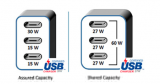

了USB3.0时代,,前面已经介绍,由于传输速率可达5Gbps,端口的工作电流高达900mA,热插拔带来的隐患急剧增大,若没有设计保护措施,极易烧毁主机板上处理高速数据存取的南桥芯片,因此在USB3.0的规范一节,专门提出,主机端一定要有可恢复过流保护的措施。

2017-07-20 10:01:44

来到了USB3.0时代,,前面已经介绍,由于传输速率可达5Gbps,端口的工作电流高达900mA,热插拔带来的隐患急剧增大,若没有设计保护措施,极易烧毁主机板上处理高速数据存取的南桥芯片,因此在USB3.0的规范一节,专门提出,主机端一定要有可恢复过流保护的措施。`

2017-08-02 10:28:49

的风险。 但是,时间来到了USB3.0时代,,前面已经介绍,由于传输速率可达5Gbps,端口的工作电流高达900mA,热插拔带来的隐患急剧增大,若没有设计保护措施,极易烧毁主机板上处理高速数据存取的南桥

2017-04-14 15:42:32

及眼图等10Gbps~28Gbps高速数字测试的时延匹配电缆新品。 Pasternack的新系列由三款具有1皮秒延迟匹配性能的超高柔性时延匹配电缆构成。这些电缆具有1.4:1的优异电压驻波比(VSWR

2018-07-04 14:03:04

(DSP/PowerPC内存-->FPGA).2. Serial RapidIO 1x,5Gbps/lane:DMA Write(FPGA-->DSP/PowerPC内存)的速度可达

2014-08-23 13:27:47

富士通微电子(上海)有限公司日前宣布推出业界领先的USB 3.0 - SATA (*1) 桥接(*2)芯片。该芯片支持超速USB和USB 3.0规范(*3),并能在外置存储器件(如磁盘驱动器HDD)和PC之间进行高达5Gbps的数据传输。

2019-08-26 08:28:21

多少倍了。我们最常见的当属USB2.0和USB3.0,这两个之间可以通用,但是也有区别:1.USB3.0的速率是5Gbps,而USB2.0的速率是480Mbps。2.从USB外观上来看,USB2.0通常

2021-08-06 08:43:14

VL813 (4-Port) USB 3.0, 5Gbps Smart Charging, 2.4A Low Power Integrated DC-DC Pin-2-Pin w/ VL812QFN

2022-05-14 11:14:09

配置和功能集成稳压器,新的低功耗设计和全面的USB充电支持。VL813支持SuperSpeed(5Gbps),高速(480Mbps),全速(12Mbps)和低速(1.5Mbps)设备的组合,集成USB

2021-12-14 15:35:25

5Gbps,总数据有效带宽为5Gbps x 2 x 80% = 8Gbps。图 6 案例功能框图图 7 PL端程序功能框图图 8 测试连接图图 9 边缘检测网页输出效果图 10 处理结果创龙科技基于TL6678ZH-EVM评估板提供CameraLink、SDI、HDMI、PAL的测试案例,客户仅需要专注上层应用开发。

2021-05-19 17:10:50

的56Gbps到对112Gbps的研发慢慢推进。在这一条高速的道路上,USB3.0对应的5Gbps已经不算很高速的协议了。不过从行业的细分来看,USB的产品依然占有重要的地位,高速先生团队见过的USB

2021-03-19 17:21:38

高速、超宽带信号采集技术在雷达、天文和气象等领域应用广泛。高采样率需要高速的模/数转换器(ADC)。目前市场上单片高速ADC的价格昂贵,分辨率较低,且采用单片超高速ADC实现的数据采集对FPGA的性能和PCB布局布线技术提出了严峻的挑战。

2019-11-08 06:34:52

带宽10.2G,长度:20m-300mDP传输系统(1.4版) :最高支持8K@60Hz,长度:15m-50mUSB3.0高速数据线:带宽5Gbps,长度: (不供电)10-100m,(供电)10m-50m `

2017-10-26 14:00:45

(Virtex-5)或19.2Gbps(Virtex-6)或22.4Gbps(Kintex-7)2. 高速LVDS数据发送:训练序列产生,数据成帧,8B/10B编码,数据并行转串行,随路时钟产生等3.

2014-03-01 18:47:47

一条物理链路的速度从600Mbps到10Gbps,高速I/O的测试和验证更成为传统专注于FPGA内部逻辑设计的设计人员所面临的巨大挑战。这些挑战使设计人员非常容易地将绝大部分设计时间放在调试和检验设计上。

2019-08-29 07:59:05

具有windows驱动。二、功能和技术指标: •8-Lane PCIe可实现5Gbps/lane*8=40Gbps的高速数据传输; •使用4个16bit DDR3 颗粒组成64bit DDR3

2015-01-28 15:48:55

嵌入式测试是什么?如何用FPGA技术去实现嵌入式设计?如何测试FPGA中的高速串行I/O?

2021-04-13 07:03:58

本文基于Virtex-5FPGA设计面向未来移动通信标准的Gbps无线通信基站系统,具有完全的可重配置性,可以完成MIMO、OFDM及LDPC等复杂信号处理算法,实现1Gbps速率的无线通信。

2021-06-07 06:48:08

情况下支持1Gbps的峰值速率,在高速移动情况下支持100Mbps;基站侧最多8根天线,终端侧最多4根天线;在移动性上最高支持500km/h的移动速度。随着技术研究与提案工作的进行,基站系统的研发也已经开始

2019-08-07 07:05:49

嗨,大家好,我在一个从FIFO场景中通过单个大容量端点读取PC的数据。我一直在高速读取数据(1帧)(~1,5GbPs),并且我需要最小化两个连续传输(2帧,不同缓冲区)之间的时间来实现这个速度。传输

2019-04-25 11:19:19

本文研究工作依托于国家“863”计划Gbps无线传输关键技术与试验系统研究开发项目,研制面向LTE-A、IMT-Advanced等未来移动通信标准,能够验证相关技术并达到标准技术指标的新型移动通信基站原型。

2021-04-15 06:47:27

嵌入式测试方案及高速测试技术,不看肯定后悔

2021-05-18 06:43:27

测试,从试验台转到生产流程中的自动测试设备(ATE)上都将面临很大的挑战,而将高速RF设备的测试转至生产环境中却完全是令人怯步的。为了便于甚高频RF接收器在生产环境中的测试,您可以使用一种将误码率

2019-06-06 08:21:46

新的13 Gbps / 13 GHz + 3.3V高速逻辑系列

2019-04-28 11:39:26

随着移动通信的迅猛发展,低频段频谱资源的开发已经非常成熟,剩余的低频段频谱资源已经不能满足5G时代10Gbps的峰值速率需求,因此未来5G系统需要在毫米波频段上寻找可用的频谱资源。作为5G关键技术

2021-01-08 07:49:38

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平输出28.5Gbps的信号要用什么电平?

2014-11-10 09:12:51

高速数字设计和测试综述高质量的信号生成电源完整性测试物联网技术中几种典型芯片NB-IOT的测试方法

2021-01-12 07:15:11

研究用于10 Gbps高等电信系统的Microvia技术

2019-09-17 09:01:16

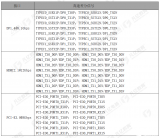

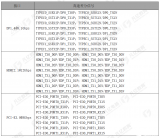

、5Gbps PCIe2.0、6Gbps SATA3.0、5Gbps USB3.0。灵活的功能扩展:5Gbps高速PCIe2.0扩展更灵活,可用于扩展千兆网卡、双频WIFI等高速外设。OK1028A-C平台模块

2020-09-24 16:42:54

请问,我想用HMC311ST89对速率为:5Gbps码型为:“1000” 的归零信号进行放大,是否可行?

2019-02-28 14:20:47

请问有人测试过国民技术的MCU芯片吗?,性能怎样,在行业水准如何呢?

2021-05-23 10:00:33

设计工程师对10Gbps收发器的抖动性能和电器特性的解释和测量方法不尽相同,迄今为止,对测试和测量10Gbps数字通讯收发器进行定量描述的工业标准尚未确定,短期内也难以见到这种技术规范。GTRAN

2014-12-09 14:36:58

作者:张水苹摘要VDMR8M32是珠海欧比特公司自主研发的一种高速、大容量的TTL同步静态存储器(MRAM),可利用其对大容量数据进行高速存取。本文首先介绍了该芯片的结构和原理,其次详细阐述了

2019-07-23 07:25:23

、5Gbps PCIe2.0、6Gbps SATA3.0、5Gbps USB3.0。灵活的功能扩展:5Gbps高速PCIe2.0扩展更灵活,可用于扩展千兆网卡、双频WIFI等高速外设。OK1028A-C平台模块

2020-09-19 22:00:46

一般大于5Gbps的高速差分信号对干扰和抖动等都很敏感,因此在设计高速差分信号线布线时,应尽量选用性能良好的微带线和带状线,在整个信号通路上保持一致的阻抗特性。对差分信号线进行布线之前,必须定义好层叠结构,以使走线能够保证严格的阻抗匹配。

2019-05-23 09:08:52

研究了5Gbps~40Gbps交换技术和IP软核的实现方法。采用多层结构、模块化的设计思想,使用Verilog硬件描述语言对40Gbps宽带交换电路进行编程,实现了一种通用的、容量可变的、可移植

2009-11-27 14:11:39 10

10 高速接口芯片测试技术爱德万测试北京分公司 李科童 爱德万测试上海分公司 刘旸在电子、微电子及通信领域,近年来一个突出的特点就是数据传输量的与日俱增,这也给

2009-12-23 15:47:43 36

36 2xType C, USB 3.2 10Gbps interface downward compatibility4xType A, USB 3.1 5Gbps interface downward

2023-10-25 15:09:30

芯片间的互连速率已经达到GHz量级,相比较于低速互连,高速互连的测试遇到了新的挑战。本文探讨了高速互连测试的难点,传统互连测试方法的不足,进而介绍了互连内建自测试(I

2010-07-31 17:00:16 15

15 科利登系统(Credence Systems)日前推出两款新的6.4Gbps高速芯片测试产品。在Sapphire S平台上,这一系列选件的任意组合能够灵活配置,为用户提供一个完整的

2006-03-13 13:00:28 517

517 高速PCB互连设计中的测试技术

互连设计技术包括测试、仿真以及各种相关标准,其中测试是验证各种仿真分析结果的方法和手段。优秀的测试方法和手段是保证互连设

2009-10-10 16:18:02 566

566

嵌入式测试方案及高速测试技术

前言

目前,在许多应用领域,例如处理器、移动电话、调制解调器等产品,SOC技术已经成为主要的研究方向。这类SOC芯片整

2009-11-17 17:20:07 306

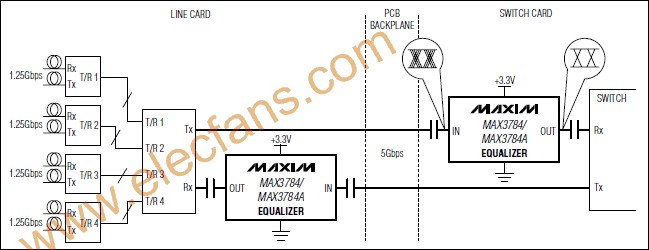

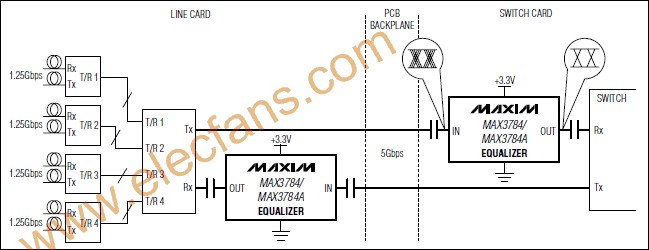

306 MAX3784, MAX3784A 5Gbps PCB均衡器

MAX3784/MAX3784A 5Gbps均衡器为距离达40英寸的FR-4提供传输媒介损耗补偿。它优化于短传输距离、平衡编码(如8b10b),适

2010-03-04 08:59:01 699

699

IDT公司日前宣布,推出全球首个支持苛刻的5Gbps超高速控制器应用要求的新器件系列,扩展了IDT在CrystalFree CMOS振荡器产品线的产品组合。

2011-09-08 09:18:35 771

771 随着信号速率的不断提升,只对高速信号的发送端物理层测试已经不能够完全反应系统的特性,因此接收机测试也已成为了高速信号的必测项目,尤其是对于信号速率高于5Gbps以上,规范

2012-12-17 18:56:56 30

30 Marvell® Alaska® 88E2010/40系列以太网收发器,这是业界首款针对Cat5e电缆,全面优化2.5Gbps和5Gbps数据传输速率的商用以太网收发器产品。

2016-04-28 14:58:42 1498

1498 高通X50基带支持800MHz频谱,分为8x100MHz,如此高的带宽使得X50基带速度非常可观,高通官方表示X50基带设计目标是支持5Gbps速率,不过高通官网中并没有公布X50基带现在到底能达到多少下行速度。

2016-10-19 18:33:35 9071

9071 高速信号完整性测试和验证技术

2017-01-14 02:53:59 23

23 Innovative Integration公司推出了基于新一代嵌入式计算机架构VPX的超高速数据采集产品。它符合OpenVPX(VITA65)标准。它采用PCIe2代的标准,每个Lane可以达到5Gbps。

2017-09-19 16:51:59 10

10 VDSR32M32是珠海欧比特公司自主研发的一种高速、大容量的静态随机器(SRAM)用其对大容量数据进行高速存取。本文首先介绍了该芯片的结构和原理,其次详细阐述了基于J750测试系统的测试技术

2018-04-27 15:27:00 3389

3389

USB3.0高速数据采集系统,以其5Gbps的带宽和即插即用等优越的性能,越来越受到人们的重视。目前常用的USB3.0通信芯片主要有来自美国赛普拉斯(CYPRESS)公司开发的EZ USB FX3系列芯片和日本NEC公司开发的uPD720200系列芯片。

2018-01-31 17:22:11 1764

1764

罗德与施瓦茨公司在华为最新发布的4.5G通信芯片巴龙765芯片平台上成功验证其下行传输速率达到LTE A-Pro 1.6Gbps。 罗德与施瓦茨公司(以下简称RS公司)和华为技术有限公司共同宣布

2018-02-27 16:30:01 205

205

最简单的USB Type-C接口,支援USB 2.0(表1中的D+与D-),将高速讯号对加入,支援USB 3.1 Gen1(5Gbps)或USB 3.1 Gen2(10Gbps)的传输速度(表1中的Tx+-与Rx+-)。

2018-03-03 16:08:02 11077

11077

随着SerDes芯片集成度、复杂度、传输速率的不断提高,传统的自动化测试系统已经无法满足SerDes测试速率需求。但通过Nautilus UDI方案的导入,成功实现了32 Gbps SerDes

2018-06-10 10:51:17 4433

4433

日本航空电子工业公司开发出了可满足车载用途的USB3.0连接器“MX62系列”。该连接器实现了USB3.0标准的5Gbps传输速度,并同时满足了车用连接器必备的机械性能和耐环境性能两方面的要求。

2018-07-25 08:43:00 2350

2350 为了绕开1Gbps的瓶颈并将速度提升至10Gbps,一般需要将网络线缆升级至超6类或7类线缆。按铺设一条线缆的成本为300美元计算的话,该线缆升级将是一项耗资巨大的工程,而且有时并不是一项可行方案(对于大型网络而言尤其如此——线缆升级过程中,可能导致损失巨大的网络延迟和连接中断)。

2019-10-12 16:36:52 9345

9345 5Gbps 至 10Gbps,具备双端口和单端口规格。装置提供可调式线性等化、输出振幅及平整增益,协助减少符码间干扰,进而使各种实体媒体的效能优化。此款装置为业界最小型的ReDriver,其使用的封装

2020-03-12 14:12:37 4302

4302 新的模数转换器(ADC)技术使首次实现单芯片100 Gbps相干接收器的设计成为可能。它使用65 nm CMOS技术,可以满足长距离光学系统的性能和功率要求。它为短途和更高速率的应用提供了未来,并提

2021-04-14 16:19:04 1451

1451 高的。 今天,高通联合澳洲电讯(Telstra)、爱立信共同宣布,成功实现了5G商用网络下,单用户下载速度高达5Gbps的新纪录。 这也是全球首次使用商用5G网络、采用智能手机形态移动测试终端实现的结果。 本次5G NR数据呼叫在澳大利亚黄金海岸5G创新中

2021-01-21 17:46:19 1963

1963 日益发展的技术对芯片电压测试的挑战 随着5G、车联网等技术的飞速发展,信号的传输速度越来越快,集成电路芯片的供电电压随之越来越小。早期芯片的供电通常是5V和3.3V,而现在高速IC的供电电压

2021-02-01 16:03:12 2610

2610

的固定性,除了影音、数码等产品之外,还可用于医疗器械。其主要特点如下:其外壳外壳采用不锈钢材质,延长了使用寿命,可达1500次,该产品塑胶采用UL防火等级94V-0,具有较强的自熄能力,另外,这款连接器实现了USB3.0标准的5Gbps传输速度。 主要性能参数如下:额定负荷: 3A MAX,使用温度: -

2021-06-13 10:16:00 1718

1718 迪赛康ISI(Inter-Symbol Interference) 损耗测试板支持从8Gpbs到16Gbps共16种损耗数值的测试。采用SMA高速可拆卸连接器与仪器连接,板卡机械尺寸为376*249mm。 4.产品

2021-11-19 10:26:37 1310

1310 该芯片用于超高速双向点对点数据传输系统。支持0.6Gbps至1.5Gbps的有效串行接口速度,提供高达1.2Gbps的有效数据带宽。

2023-05-09 09:47:23 302

302 随着集成电路技术的发展,高速信号的设计技术指标不断更新,系统中的数据传输速率已经提高到数十 Gbit/s 乃至数百 Gbit/s,这就给测试系统、测试硬件设计、测试信号传输质量等带来了新的挑战和更高

2023-06-02 13:43:05 1045

1045

会议名称: 是德 | ICisC高速芯片测试技术研讨会(南京专场) 会议时间: 2023年07月10日 下午1330 会议地点: 南京江北新区华富路一号 四号楼集成电路国家芯火平台 会议简介 本次

2023-06-28 07:55:02 343

343 8Gbps及以上高速信号PCB布线建议 —来源:瑞星微RK3588 PCB设计白皮书 如表1-1所示,RK3588芯片以下接口的信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求

2023-08-02 07:35:01 423

423

该芯片用于超高速双向点对点数据传输系统,支持 0.6Gbps 至 1.5Gbps 的有效串行接口速度,提供高达1.2Gbps 的有效数据带宽。

2023-08-29 10:29:27 726

726 电学测试是芯片测试的一个重要环节,用来描述和评估芯片的电性能、稳定性和可靠性。芯片电学测试包括直流参数测试、交流参数测试和高速数字信号性能测试等。

2023-10-26 15:34:14 629

629 高速信号眼图测试的基本原理 高速信号眼图测试是一种用于衡量和分析高速数字信号的测试方法。在电子通信领域,高速信号是指传输速率较快的数字信号,例如10 Gbps或更高的速率。 高速信号眼图测试

2024-02-01 16:19:49 142

142

电子发烧友App

电子发烧友App

评论