3 ASIC验证及性能分析

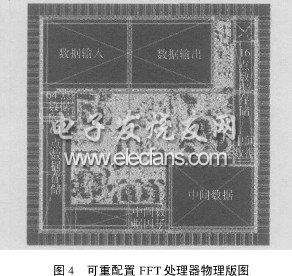

使用VHDL硬件编程语言在RTL级对可重配置FFT处理器进行了代码描述.基于SMIC 0.18μm标准单元工艺库,用Synopsys DesignCompiler综合工具进行逻辑综合,使用Astro 工具进行版图规则及布局布线;用仿真工具VCS进行逻辑动态仿真,用参数提取工具Star-RCXT提取寄生参数并使用静态时序分析工具PrimeTime对整个设计系统进行静态时序分析.处理器的ASIC版图如图4所示存储器按照图1所示数据流的方向排放,以便于逻辑单元布局布线.处理器版图采用了3层电源环结构.采用该结构一方面可增加管脚供电能力,另一方面也可有效减小芯片面积(处理器芯片面积为3.6mm×3.7mm).

表1为作者所提出的结构与Hason结构的性能比较.其中数据用36 bit表示(高18 bit为实部,低18 bit为虚部),指数用6bit表示,结果比较用kbit表示.由表1比较结果可知,作者所提出的可重配置FFT处理器结构不仅减小了45%的存储器资源,而且节省了52%的处理时间.该处理器芯片在连续工作100 MHz时钟频率时,处理第1组1 024点FFT序列需要24.8 μs,以后每10.24μs给出1组1 024点运算结果.表2为FFT处理器进行各种点数运算的功耗.可重配置结构采用复用器及相关的逻辑电路实现门控时钟电路,这样,在进行不同点数运算时可以启动不同的运算单元(屏蔽不需要的运算单元),以降低功耗.由表2可知,在启动64点FFT运算模块时,系统功耗较1 024点FFT运算量降低了约49%,而 4点运算量降低了约80%.

4 结论

提出一种可重配置FFT处理器的ASIC芯片设计与实现、该芯片采用子模块基-4单元级联流水线结构,使用双口RAM进行乒乓存储,不仅减少了硬件实现资源,而且提高了处理速度,具有连续计算4,16,64,256和1 024点复数输入FFT的运算功能.结构设计采用模块化设计,缩短了芯片设计开发周期.处理器芯片面积为3.6mm×3.7mm,适用于实时、高精度动态变换应用场合.

用户评论

共 0 条评论