向量(Pattern)发生器发生时钟时,其实现方法有示于图2的使用Variable Delay的方法和使用PLL来发生的2种模式。一般半导体测试系统采用的是VariableDelay方式,计测器等脉冲发生器等处于高速及低Jitter的要求,采用的是PLL方式。图3是由采用Variable Delay方式,利用T6683发生的500MHz信号的XOR方式合成的5Gbps数据的波形。各通道的输出Delay已经经过最适化的调整,但是还是可以看到XOR的输入Jitter没有任何改善显现在输出波形中,单纯这样的波形是不能适用于数GHz的高速信号传输。

因此我们采用的是如图4所示的低速时钟发生采用Variable Delay方式,高速部采用与低速部保持同步的PLL方式。另外,Jitter Reduce电路的嵌入也可以使得高速部的向量(Pattern)发生尽可能的不受到低速部的Jitter误差的影响。

从PE到被测芯片(DUT)的高速信号传送

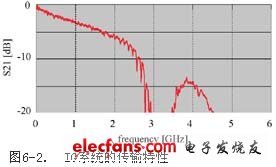

在实际测试中,从ATE的Driver端到被测芯片(DUT)的信号传送过程,会遇到如图6-1所示的Pin-Relay、传输线路(同轴线)、接线端子、印刷线路等各影响高频信号衰减的问题。图6-2是一般的1GHz信号用线路的传输特性,当用它来传输更高频率的信号时,我们可以看到在2.5GHz开始就会造成较大的衰减损失。这个衰减如果是超过10dB以上的话,是很难进行正确补偿的。因此为了减小在高频带的损失,我们对上述图6-1线路进行了以下4个项目的改进。

① Pin Relay & DC Relay

② 同轴线

③接线端子(Connecter)

④ 印刷线路

用户评论

共 0 条评论