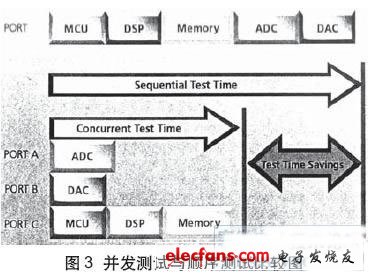

在大规模器件(如无线基带SoC处理器)中,有无数个模拟芯核,并行地测试这些芯核需要大量的模拟资源。若按4个测试点,全并行、并发测试式计算,需提供28个数字化仪,这在当前的ATE系统中还难以实现。

一种新型模块体系结构

测试当前消费品器件中使用的各种模拟芯核,需要高度并行,低开销的解决方案。若在每个模块中组合几个模块功能,能相应地减少每个模拟模块的占用空间,这样,就有更多的空间留给必需的数字模块。一个内置8个独立Arb或数字化仪单元的模块具有灵活地配置的优点:或只用作数字化仪单元,或是数字化义与Arb单元的组合。

降低消费类器件测试的COT不仅要解决ATE测试系统的并行测试方案,还要减少并行测试带来的ATE开销。多芯核是当前SoC消费类器件的主要特征,在对ATE硬件进行体系结构改进时同样要考虑上面两个因素,这样才能得到最佳的测试解决方案。

用户评论

共 0 条评论