PCI-SIG将PCIe的锁相回路(PLL)列为基本测试项目,目前有几种可用于执行该测试的手法。本文中将以PCIe 2.0的规格要求为例,概述几种较为常见的方法,并针对其优势与劣势进行简单比较。

为了在系统中控制抖动抑制效能,PCIe 2.0规定了板载PLL的操作回路回应特性,特别是最小和最大的PLL回路带宽和峰值。表1列出了规格中所述的这些PLL回应特性。

目前有几种量测PLL回路响应的方法,取决于所使用的测试仪器类型。正如预期,这些方法都会在测试准确度、测试速度(吞吐量)、易用性、易设定性及初始成本等方面有所取舍。此外,有些方法还具有不同的限制,造成其无法普遍用于所有的PLL类型。

虽然所有的方法均可测试对规格要求的兼容性,不过,有些方法可提供额外的实用数据,让频率设计人员能优化其设计。

为了维持一致性和可重复性,所有的方法均假定采用SIG提供的标准测试夹具,即兼容性基板(CBB) 2.0版。

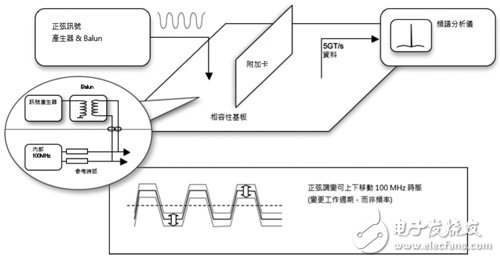

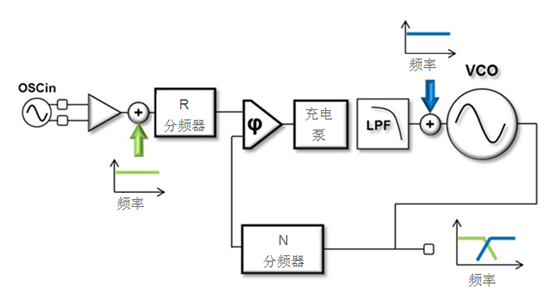

以频谱分析仪为基础的量测是分析PLL回路回应的传统方法(图1)。此方法将采用两部仪器;具有扫描功能的正弦讯号产生器,以及频谱分析仪。讯号产生器用于调变的参考频率工作周期,而发射频率输出则是在连接频谱分析仪的数据信道上进行量测。

图1 以频谱分析仪为基础的测试。

频谱分析仪测试法仅适用特定PLL拓扑型态

因为同步讯号产生器以追踪频谱分析仪的本地振荡器方法并不实际,量测作业是由绘制峰值振幅量测的封包使用大多数频谱分析仪中所提供的「峰值保持」功能来进行。振荡器会连续扫频,比频谱分析仪的扫描速度快得多。

输出频谱会显示峰值和数据速率基波和所有谐波,且侧频带斜率是PLL带宽的曲线图。因为分析仪的输出为绝对值,所以不会进行缩放。相反,相关的量测是使用配对的增量光标(若可用)或手动使用单一光标(记录绝对标称值和峰值,并从中减去测试极限)来进行。

调变参考频率的方法对此测试方法能否具备普遍适用性具有一定的影响力。在此测试方法中,CBB上的焊接式跳线配置为差动测试讯号与CBB上产生的100MHz振荡器的总和。外部的BALUN会放置于讯号产生器与主板上的求和点之间,以调变差动频率的两个部分。结果是振幅-调变频率讯号的交叉点基本上是由外部正弦来源从差动讯号的中心移动。

因为交叉点已改变,并非100MHz参考振荡器的频率,所以此方法实际上会调变PLL参考的工作周期。这对单边缘相位侦测器而言,将呈现为相位调变,因此在这个测试案例中是可行的。然而,若要在高达5GT/s的设计上减少抖动,许多设计人员将会选择采用PLL设计(在上升和下降边缘比较相位),以降低相乘比率。 这类PLL仅会追踪频率的总周期,不会响应工作周期变化。此时便无法便使用此参考调变方法来分析其特性。

由于PLL参考的相位调变是由振幅调变(AM)100MHz参考频率而产生,因此频谱分析仪上的侧频带包含调幅和调频(FM)成分。工程师在解译结果时,必须需格外谨慎,以确保量测所得的数据仅包含PLL带宽。

如同所有使用扫频外差频谱分析仪所进行的量测,带宽分辨率和扫描时间之间存在着直接的取舍问题。由于测试极限范围缩小至个位数MHz,即需要相对较低 的频率分辨率带宽(通常是30kHz)。 外差频谱分析仪中的侦测器仅会量测幅度,所以无法使用回路响应的相位数据。虽然对于基础规格的测试兼容性并不要求相位,不过,频率设计者仍可将其用于确定PLL相位余裕,这对评估设计而言是一个非常有力的工具。

以频谱分析仪为基础的方法提供了宽动态范围的振幅,可有效简化测试设定。振幅分辨率限制在约1dB或略佳的实用值,在峰值仅有1dB的情况下测试带宽时,此值将为余裕。

测试设定有些复杂,需要设定讯号产生器的操作参数及频谱分析仪的量测参数。在设定讯号产生器振幅时务必小心谨慎,以避免过度驱动CBB求和节点。预先储存的设定可以用来简化此程序;然而,所产生的曲线图仍需要进行一些解译和手动光标扫描,以读取参数值。

手动放置游标常常是在量测中误差和不可重复性的来源。在一些情况下,DUT具有与频率数据速率不相关的抖动频谱分量,如切换电源的谐波为例。这些峰值可能会发生在正在进行PLL响应量测的基线区域,造成用户无法在实际轨迹上放置量测光标,导致用户需猜测峰值是否在此位置。

示波器分辨率优于频谱分析仪 然亦受限于PLL拓扑

以示波器为基础的方法使用了数字示波器来代替频谱分析仪。最直接的方法是使用示波器的FFT能力来产生频域数据。相较于频谱分析仪,此方法提供了几项改善功能:频率分辨率是采样率和内存长度的函数,可针对量测的要求进行优化处理。讯号撷取和量测吞吐量的速度远优于频谱分析仪中的慢速扫描本地振荡器。

相较之下,动态范围小一个数量级,要求示波器在量测之前设定适当的比例因子,分辨率比频谱分析仪更好。但是,最佳示波器的动态频率响应准确为+/-1dB量级,将量测准确度限制至约1dB。垂直缩放功能在本质上为线性函数,需要参数数学运算以转换为dB。

与频谱分析仪不同的是,在示波器中的FFT计算可产生相位回应及大小。

以示波器为基础的方法使用与频谱分析仪方法相同的讯号产生器组态,因此这两种方法均需要额外的仪器,也同样无法与PLL搭配使用,进而需采用两部边缘相位侦测器。

误码率测试仪方法又快又精准

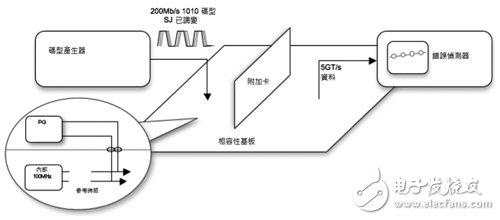

高效能误码率测试仪(BERT)可配置为直接量测PLL回路响应(图2)。BERT 同时具有刺激和量测能力,可让用户以单一仪器来执行此测试。针对PLL量测,BERT必须可利用正确的直流偏移,将「压力」(校准的抖动)注入码型产生器100MHz差动输出。

图2 使用BERT进行PLL量测。

以BERT为基础的量测使用与频谱分析仪和示波器方法不同的方法来刺激待测PLL。BERT并不是将失真的讯号总结入兼容性基板上所产生的100MHz参考振荡器,而是透过对码型产生器进行程序设计来提供参考讯号,以200Mbit/s的速率输出1010码型(频率)。这相当于100MHz的差动频率。应力产生器设定为将正弦抖动注入至码型输出,可针对波形的周期进行相位调变。此组态要求CBB上的电阻器/跳线需设为外部参考频率输入。

在待测PLL输出中的直通抖动是由BERT误码仪量测而得。透过步进调整正弦抖动应力的频率,即可产生抖动转移函数曲线图。额外的数学处理功能则可产生PLL回路响应曲线图。

如同以示波器为基础的方法,使用者可手动执行此量测。然而,已录制好的软件选项将会自动执行任务,尽可能地减少了潜在的使用者错误;同时还可加快量测速度,并提供直接的通过/失败测试。

相较于频谱分析仪或示波器可提供的功能,以BERT为基础的量测提供了更高的准确度和可重复性。透过自动化软件,用户只需要几秒钟就可得到准确结果。

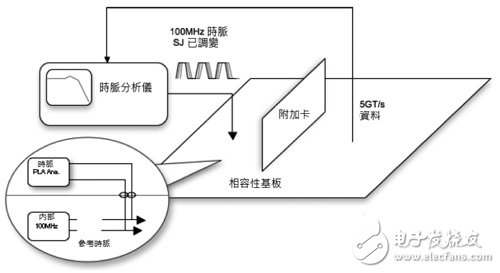

频率资料回复仪适用各类PLL拓扑

高效能频率数据回复仪器可用于量测PLL回路回应(图3)。相较于前述其他方法,此方法提供了几项优势。这些仪器在本质上属于「仪器等级」的频率数据回复单元,使用复杂的PLL设计,可在广泛频率频率上操作,并具有校准和使用者可程序设计的回路响应。为了利于进行自我校准,这些仪器包含直接数字合成器(DDS)以生产各种讯号。

图3 频率数据回复仪器量测方法。

DDS的输出可在PLL测试组态中由外部提供,以作为参考频率。如同以BERT为基础的测试方法,频率数据回复仪器方法仅需单一仪器即可产生刺激并量测输出。

然而,DDS来源频率数据回复仪器为基础的方法确实与频谱分析仪及示波器方法不同,其参考讯号会经过程序设计以维持完美的 50%工作周期。这可让使用者进行所有的PLL拓扑通用测试,包括具有双边缘相位侦波器。可在调变参考相位时维持50%工作周期的功能是以BERT或频率数据回复为基础的测试方法的独特内建功能。

来自兼容性基板上用户选定信道的输出讯号会路由至频率数据回复仪器的数据输入接头。在此处,频率会透过仪器的精密PLL进行回复。相位误差侦测器的输出会进行数字化并处理,以确定相对相位误差。来自数字化波形的正弦和余弦数据会用来计算通过待测PLL的相位调变的相位和幅度(相对于频率)。因为相位误差量测会同步至参考频率的调变,所以可针对量测建立关联,以有效将动态范围提高到75dB以上。

相较于其他方法,除了在调变测试讯号的相位时维持50%的工作因子,以频率数据回复为基础的方法还提供了几项优势。在维持由频谱分析仪提供的动态范围之外,还可能具备0.01dB的振幅分辨率,这提供了最高的准确度和量测可重复性。

同时,这种方法也具有高频率分辨率,且在不到10秒的时间内即可产生一个完整的量测。量测方法本身即会产生相位图及大小。虽然在验证兼容性时仅需要在-3dB点的频率和峰值位准,不过,额外的相位图可让使用者用于判定其PLL设计的相位余裕;这是一个非常强大的设计评估工具。最后,此方法也能产生PLL 增益(亦称为抖动传递函数,JTF)图。

量测PCIe锁相回路 BERT/频率资料回复最理想

本文中所介绍的四种方法均可执行PCIe 2.0基本规格要求的PLL回路响应量测;然而,仅有由频率数据回复所共享的相位调变方法和以BERT为基础的方法可与所有PLL设计搭配使用。这些方法在设定及结果解释的复杂性、分辨率和准确度、可重复性和初始成本等方面有显著不同。

以频率数据回复为基础的方法是单一仪器解决方案,能以最简单的设定和最低的成本提供高准确度、高分辨率和可重复性;亦具有提供额外数据的优点,可让PLL设计人员更充分地了解其设计的效能。

电子发烧友App

电子发烧友App

评论