本文主要详解PCI总线与PXI总线有什么区别,首先介绍了PCI 总线结构图、特点及PCI总线性能,其次阐述了PXI总线的特性,最后介绍了PCI总线与PXI总线的区别。

2018-05-24 09:15:23 13958

13958

静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期

2020-11-25 11:03:09 8918

8918

看了郭天祥的I2C总线这一节,发现他在编写向AT24C的E2PROM时时序有问题。原始部分程序为:typedef unsigned char uchar;uchar read_byte

2016-08-25 21:35:07

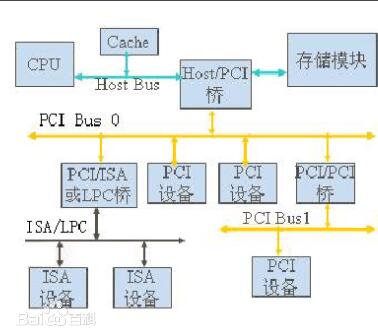

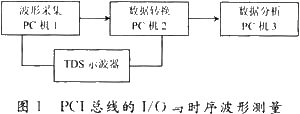

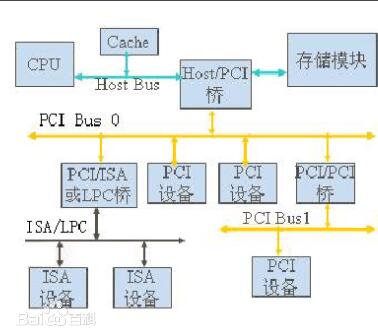

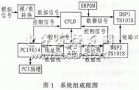

概述。PC 的演进历史上世纪90 年代初,PCI 总线一经推出,即统一了当时并存的多种I/O 总线,诸如VESA 局域总线,EISA,ISA 和微通道等等,如图1所示。它首先被用于实现芯片与芯片间互连并

2019-05-10 07:00:07

解设备产生中断的条件和使用中断的数量。 (5) 数据传输机制 最常见的数据传输机制是通过I/O端口(port),也就是通过CPU进行数据读写。PC的另一种重要的传输机制是DMA,但PCI规范不包括从属

2020-09-06 12:43:10

以实现ISA总线到PCI总线的无缝连接,这为目前仍存在的ISA插件移植到PCI提供了极大的方便。利用PCI9052的ISA模式进行PCI的开发可以简化设备开发过程,但难度还是较大。设计者不仅要理解掌握

2018-12-17 11:23:00

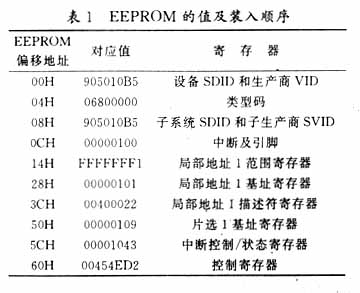

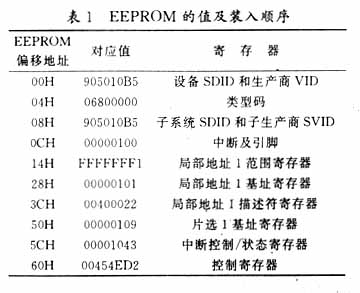

9050支持突发存储器映射和I/O映射方式在PCI总线和局部总线存取数据。双向FIFO可以用于零等待状态突发操作。PCI总线总是工作在突发方式,局部总线可以设置成突发方式或者连续单周期方式。 (2)产生中

2018-11-29 14:52:52

公司的PCI9054接口芯片。二、 概述PCI9054是由美国PLX公司生产的先进的PCI I/O加速器,采用了先进的PLX数据流水线结构技术,是32位、33MHz的PCI总线主I/O加速器;符合PCI

2008-10-09 11:23:38

概述 PCI9054是由美国PLX公司生产的先进的PCI I/O加速器,采用了先进的PLX数据流水线结构技术,是32位、33MHz的PCI总线主I/O加速器;符合PCI本地总线规范2.2版,突发传输

2018-12-05 10:12:42

速率高 最大数据传输率为132MB/s,当数据宽度升级到64位,数据传输率可达264MB/s。这是其他总线难以比拟的。它大大缓解了数据I/O瓶颈,使高性能CPU的功能得以充分发挥,适应高速设备数据传输

2012-04-06 14:37:24

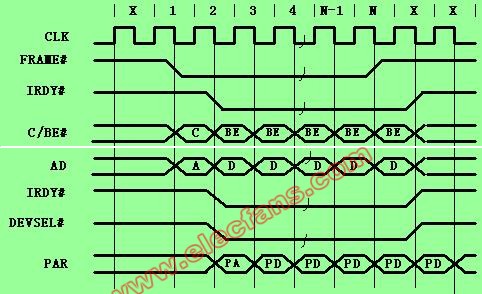

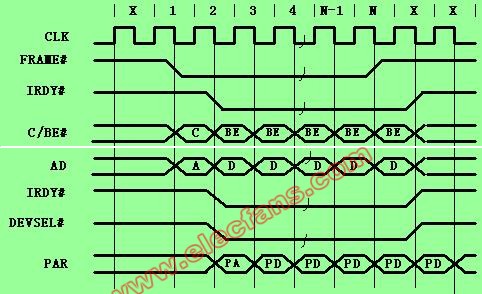

不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。在做数据传输时,由一个PCI设备做发起者(主控

2019-10-16 09:02:10

,还有FRAME、IRDY、TRDY等重要的信号线。让单片机有限的I/O端口来直接控制如此众多的信号线是不可能的。一种可行的方案就是利用CPLD作为沟通单片机与PCI设备间的桥梁,充分利用CPLD中I

2019-04-24 07:00:09

pci总线的含义是什么90年代,随着图形处理技术和多媒体技术的广泛应用,在以Windows为代表的图形用户接口(GUI)进入PC机之后,要求有高速的图形描绘能力和I/O处理能力。这不仅要求图形适配卡

2008-12-09 13:46:13

逻辑电路分为组合逻辑电路和时序逻辑电路。第四章已经学习了组合逻辑电路的分析与设计的方法,这一章我们来学习时序电路的分析与设计的方法。在学习时序逻辑电路时应注意的重点是常用时序部件的分析与设计这一

2018-08-23 10:28:59

测量I/O里面没有Data Acquision子选板,这是为什么?请大神指导!

2013-07-04 15:02:57

跪求大神,,,我的问题是关于数据采集方面的,,在测量I/O里缺少一个Digital I/O,我已经在NI的官网里面下载了max并且都安装好了,并且对max也进行了重置,可是什么方法都试过了,最后也没有装载出这个VI,请问大神是需要下载什么还是软件哪里没有安装好?

2021-11-02 19:36:07

Incremental Compilation。这是造成上述两种方法容易混淆的原因。5. 核心频率约束+时序例外约束+I/O约束+寄存器布局约束 寄存器布局约束是精确到寄存器或LE一级的细粒度布局约束。设计者

2017-12-27 09:15:17

的时序约束。FPGA作为PCB上的一个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing

2016-06-02 15:54:04

FPGA中的I_O时序优化设计在数字系统的同步接口设计中, 可编程逻辑器件的输入输出往往需要和周围新片对接,此时IPO接口的时序问题显得尤为重要。介绍了几种FPGA中的IPO时序优化设计的方案, 切实有效的解决了IPO接口中的时序同步问题。

2012-08-12 11:57:59

,不能与更高速的总线(如PCI)配合使用。(2)两个8237 DMAC一起只提供了8个DMA通道,这也成为了限制系统I/O吞吐率提升的瓶颈。 鉴于上述两个原因,PCI总线体系结构设计一种成为“第一

2019-07-01 08:10:07

各位大神最近安装了Labview2012和研华的采集卡PCI1716L驱动,同时安装DAQNavi SDK 3.1版本。但是在函数面板-测量I/O里面没找到研华的信息,这是什么问题??谢谢

2017-08-10 18:36:40

。PCI9052与PCI9050一样,可提供用于适配卡的小型高性能PCI总线目标(从属)接口,以使ISA适配器可以迅速、低成本地转换到PCI总线上。采用PCI9052可使适配卡上的I/O数据传送速度从

2012-01-05 10:47:37

4 FPGA接口程序的设计FPGA中的VME总线接口程序主要由2大模块组成,一个模块是VME主机对双口RAM访问的普通I/O模块,该模块主要实现标准VME总线访问时序到双口RAM访问时序的逻辑转换

2019-04-12 07:00:09

个器件,是整个PCB系统时序收敛的一部分。FPGA作为PCB设计的一部分,是需要PCB设计工程师像对待所有COTS器件一样,阅读并分析其I/O Timing Diagram的。FPGA不同于COTS

2017-10-20 13:26:35

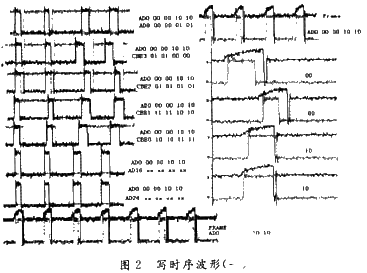

控制信号完全符合PCI时序的要求。实现了将ASI信号通过PCI总线与PC进行实时数据传输的目的。图中32位ad信号的高位没有得到充分利用,如果需要,可以很方便地利用它们将电路升级为两路或4路的多路

2012-11-28 15:38:05

。 例如,一个激励-响应系统可能需要输出通道与输入通道共享相同的采样时钟和触发信号,从而使 I/O 信号具有相关性可以更好地分析结果。 不同总线上的 DAQ 设备提供不同的方式来实现同步。多个设备同步测量

2018-03-21 11:18:43

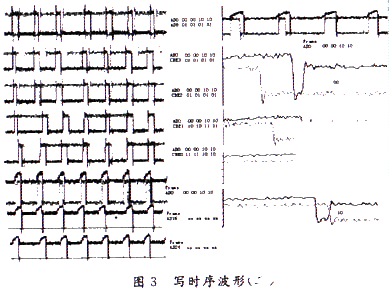

的方式,将DSP的HPI口作为PC104总线的8位I/O设备。PC104总线的I/O访问时序如图2和图3所示。 根据PC104总线的I/O访问时序,只需使用以下的总线信号,即可完成8位总线的通信

2019-05-07 07:00:09

摘要:介绍了PCI总线控制芯片PCI2040的功能及内部结构,分析了基于PCI总线的双DSP通信的硬件结构及实现方法,并描述了利用Windows2000 DDK开发WDM设备驱动程序的方法及PCI双

2019-09-24 22:18:02

不同的参数配置。 2 FPGA 模块设计 为了实现对图像传感器的正确配置,必须严格按照MT9P031 的配置时序完成设计,本设计中I2C 总线配置模块主要由三个小模块构成,它们分别

2018-11-12 10:52:08

器件。采用可编程逻辑器件实现PCI 接口比较灵活, 可以利用的器件也比较多, 但由于PCI 总线协议的复杂性, 其接口的实现比ISA等总线要困难得多, 这种方法难度较大, 设计周期较长。采用专用接口器件不仅

2010-09-22 08:51:09

编制设备驱动程序才能实现对PCI总线设备的完全访问。 应用程序对设备I/O进行Win32调用,这个调用由I/O系统服务接收。I/O管理器从这个请求构造一个合适的I/O请求包(IRP)。在最简单

2009-04-20 10:51:10

,主设备插入等待周期,同时用户设备也有效Ready和Term请求终止传输,在第5个数据也是最后一个数据传输完成后,总线交易结束。这两个时序图属于传输最后一个数据并断开连接情形的两种不同情况。仿真波形的分析

2019-05-29 05:00:02

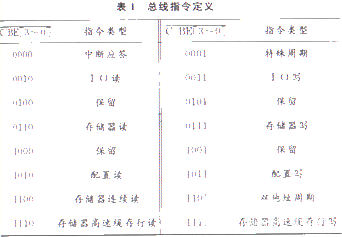

。HPI寄存器的选择由HCNTL[1:0]脚在PCI总线地址有效期实现,说明如表1所示:在主机访问DSP片内RAM过程中,主机首先根据访问类型对HPIC寄存器进行初始化操作,然后再对HPIA寄存器进行操作

2018-12-17 11:29:06

来源: 作者:分类:0 引言PCIE(PCI express)是用来互联诸如计算机和通信平台应用中外围设备的第三代高性能I/0总线。PCIE体系结构继承了第二代总线体系结构最有用的特点,采用与PCI

2019-05-21 05:00:02

Bus的猝发存储器映射空间的传送和I/O访问。读和写FIFO允许在PCI和局部总线之间的高性能猝发。PCI总线被允许猝发,这样Local Bus能被设置成猝发或持续单周期。(4)4个局部片选

2018-12-12 10:27:45

系列FPGA的I/O口电压只支持3.3V,因此需要在FPGA和PCI连接器间加入电平转换电路。实现电平转换的原理是在总线间加入NMOS总线开关,实现方式如图5所示。 其中总线开关选用IDT公司

2018-12-04 10:35:21

,此时应设置产生用于VERIBEST进行功能验证的VHDL网表文件。布局布线后,进行时间参数分析。我们的设计结果PCI时钟为30MHz,CPU时钟为57MHz。 3. 设计验证 设计验证包括静态时序分析

2019-04-17 07:00:06

,此时应设置产生用于VERIBEST进行功能验证的VHDL网表文件。布局布线后,进行时间参数分析。我们的设计结果PCI时钟为30MHz,CPU时钟为57MHz。 3. 设计验证 设计验证包括静态时序分析

2019-04-12 07:00:11

的数字I/O通道写出,故在各个数字输出通道产生脉冲波形。然而时序脉冲信号的周期性通过For Loop循环实现,一次循环产生一个脉冲波形,即实现一次控制过程,如果需要进行多次控制,只要设定循环次数即可

2019-04-09 09:40:04

时序时,单总线需要被拉低至少60μs,保证DS18B20能够在15μs~45μs能够正确地采样I/O总线上的"0"电平;DS18B20写1时序时,单总线被拉低,并在15μs内释放

2008-09-24 16:28:15

工控机显示、存储并处理,从而实现一个闭环反馈的自动测量系统. 它扩展了现有仪器的功能,使测量工作变得快捷、简便、精确和高效.c. I/ O 接口卡采用NI 公司生产的PCI26503 数字I/ O卡,该

2019-04-11 09:40:05

如何实现单片机与PCI总线接口的并行通信?

2021-04-29 07:14:26

写单片机程序有段时间了,遇到很多产品可靠性的问题,于是就想如何在时序上保证通信端口的正确。 下面的截图是我在STC15上实验的SPI接口功能,测量的端口波形。 引脚并没有接任何负载,单纯的引脚引出

2019-01-10 10:55:05

如何利用双端口RAM去实现PCI总线接口?

2021-05-06 06:30:53

如何去采用PCI9030芯片实现从ISA总线到PCI总线的转接卡的设计?有哪些方法?其过程是怎样的?

2021-07-01 08:00:36

本文提出了一种新的包括PCI9054单周期读、写和存储器映射传输的设计,并讨论了通用PCI总线高速数据采集卡的实现方案。

2021-06-08 06:28:30

怎么实现基于IP内核的PCI总线接口设计?

2021-05-27 06:34:05

总线的电气规范大部份跟PCI相同,只是增加了一些仪器特性。基于以上考虑,我们决定通过设计一个PCI接口卡来系统地了解利用接口芯片PCI 9030开发PXI模块的过程和方法。2、硬件设计目前实现 PCI

2019-05-05 09:29:33

PCI总线特点及开发现状PCI接口配置空间的实现求一款在PCI总线上利用FPGA技术设计PCI总线接口的设计方案

2021-04-15 06:17:20

丢失;4,可实现对I2C协议进行自定义解析,该功能可以很方便的分析I2C总线上的数据;软件下载及使用教程:http://www.u***xyz.com/archives/166硬件:https

2015-12-17 09:46:50

正确,有无过冲信号等。然后使用逻辑分析仪抓取总线上的逻辑波形,排查时序是否存在问题。下图是I2C 信号时序,测量时序准确性时可以添加测量标尺辅助测量,精确定位时序问题。 I2C接口逻辑波形 2、协议

2017-10-19 09:11:23

的下降沿诱发数据传输,而在上升沿指明只有一个数据或只剩下一个数据;(6)读操作比写操作多一个中间准备过程。 3 基于CPLD的状态机设计3.1 状态机的构造根据对上述时序图的分析,完成一个简易PCI总线

2019-06-17 05:00:11

对1553B总线和PCI总线协议的分析,结合航天地面测试实际要求提出了一种1553B-PCI总线接口卡的实现方法,给出了硬件结构框图,部分原理图和接口控制的FPGA实现。经过测试,实现了计算机通过PCI总线与远程终端设备的信息交互,满足了实际要求,并在XXX型号地面测试中应用。

2019-05-21 05:00:22

复杂度。北桥和南桥是传统个人计算机架构中的两个核心器件。南桥处理系统的I/O功能,而北桥则负责系统处理器、图像子系统、内存和PCI夹层总线之间的高速通信。与早期的器件不同,像北桥这样的精密IC具有完全

2009-10-13 17:25:13

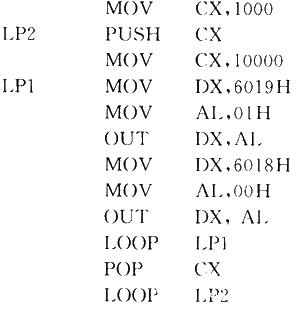

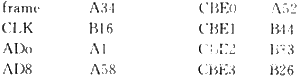

PCI总线是什么?PCI总线的功能有哪些?怎样去测量PCI总线的I/O写时序波形?如何去测量夏华状元一族主板PCI写周期的时序波形?

2021-04-15 06:22:17

软件I/O模拟I2C总线时序和直接连接CPU固有的I2C接口,在使用上有什么区别,直接用固有的接口,还需要模拟时序吗?[/mw_shl_code]

2020-06-02 04:35:08

。并将FIFO缓存后输出的数据用DMA传输方式通过PCI总线实现对PC内存的存取,同时利用FIFO的标志信号控制DMA传输过程。下面对FPGA控制电路的各模块进行介绍。 PCI_MT32功能模块 本文

2019-05-05 09:29:32

很好地发挥PCI总线的性能。针对这些不足,在分析了流水线技术特点的基础上,论述了采用流水线技术设计基于PCI总线高速数据采集系统的方法。按该方法设计的数据采集系统,可以达到很高的数据采集速度和数

2009-10-30 15:09:49

;计算机对结果数据进行分析处理、按一定的标准进行判别,将测试结果进行显示、控制分选机对被测器件进行分选。1 PCI总线及其接口的实现自动化集成电路测试系统(ATE)的结构图如图1所示。本设计的接口总线选用

2019-05-30 05:00:02

的PCI总线速度更快(数据传输率为133 Mb/s)、实时性更好、可控性更佳,更易于实现高速实时的I/O口控制卡、通信接口卡、数据采集卡等。但PCI总线也因其32位地址与数据复用、控制总线及时序较复杂

2019-04-29 07:00:09

进行功能验证的VHDL网表文件。布局布线后,进行时间参数分析。我们的设计结果PCI时钟为30MHz,CPU时钟为57MHz。 3. 设计验证设计验证包括静态时序分析,功能验证及板级验证。静态时序分析

2019-05-08 07:00:46

硬件实现的应用包括了灵活的编码输入,PWM 信号I/O,PID 控制,定制计数器实现,数字协议仿真,离散控制和定制测量等等。[hide] [/hide]

2009-07-23 08:15:57

介绍 PCI 总线的特点,对现有的 PCI 总线的接口设计方法进行分析;介绍 PCI 接口芯片CY7C09449PV的结构及其与数字信号处理器TMS320C32之间接口电路的设计,提出一种基于PCI和 C32的数据

2009-04-08 09:53:42 26

26 针对某C3I 系统2FSK 调制信号的检测,应用PCI 总线技术构建了基于C++ Builder 5 编程平台的2FSK 调制信号自动检测系统,重点介绍了其软件实现方法和技术。关键词:PCI 总线 C3I 系统 2

2009-06-13 11:56:47 17

17 基于PCI总线的高速数据采集卡系统设计与实现:本文介绍一种基于PCI总线的高速数据采集卡系统的设计方法,讨论了设计高速数据采集系统的关键技术,给出了系统整体设计方案和P

2009-06-22 19:04:54 44

44 基于FPGA的PCI总线接口设计::PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接

2009-06-25 08:17:18 48

48 本文在结合嵌入式实时操作系统VxWorks 和PCI总线的特点的基础上,介绍了PCI总线驱动设计的过程,并从充分应用VxWorks 卓越的实时性和PCI总线灵活的扩展性的角度出发,给出了有一定

2009-08-10 09:02:36 24

24 本文简要介绍了PCI 总线的仲裁机制, 完成了PCI 总线仲裁器核心的设计、实现。通过ModelSim 进行了软件仿真,最后在XILINX 公司的FPGA 上加以了验证。

2009-09-03 08:18:29 27

27 针对数据加密算法的硬件设计,主要讨论了一个基于PCI 总线的数据加密系统的设计与实现过程。首先对系统体系结构以及在FPGA 芯片内部对PCI 接口模块的实现进行了分析,然

2009-09-17 12:00:31 29

29 针对数据加密算法的硬件设计,主要讨论了一个基于PCI 总线的数据加密系统的设计与实现过程。首先对系统体系结构以及在FPGA 芯片内部对PCI 接口模块的实现进行了分析,

2009-12-25 15:51:52 14

14 本文重点分析了PCI 总线设备控制器的设计方案。以PCI 总线协议的分析和理解为基础,对PCI 总线设备控制器进行了功能分析和结构划分,对PCI 总线从设备控制器的设计思路和各个

2010-01-13 16:57:37 49

49 PCI总线协议的FPGA实现及驱动设计

摘要! 采用FPGA技术! 在公司的flex6000系列芯片上实现了从设备模式pci总线的简化协议!并给出了WIndowsx 系统下的虚拟设备驱动程序

2010-03-12 14:30:27 36

36 摘 要: 本文采用Altera的CPLD实现了PCI总线至UTOPIA接口的逻辑转换控制,为低成本实现ATM终端奠定了基础。

2006-03-11 13:16:50 864

864

PCI总线原理

PCI总线的特点:数据总线32位,可扩充到64位。可进行突发(burst)式传输。总线操作与处

2008-12-09 11:30:05 13510

13510

PCI9052是PLX公司开发的服从PCI协议的从模式接口芯片,它能够实现ISA总线到PCI总线的平滑转换。主要阐述了PCI9052在ISA模式下的应用开发过程和方法,并给出了一个实例,说明了如何

2009-05-09 12:02:57 1124

1124

摘 要 :PCI是一种高性能的局部总线规范,可实现各种功能标准的PCI总线卡。本文简要介绍了PCI总线的特点、信号与命令,提出了一种利用高速FPGA实现PCI总线接口的

2009-06-20 13:13:28 936

936

摘 要: 以自行研制开发的PCI高速总线背板为背景,系统地论述了PCI总线的仲裁机制、总线的缺省占用、仲裁信号协定及优先级仲裁算法,给出了采用EPLD实现仲裁器功能的编程设计

2009-06-20 13:32:20 961

961

基于PCI总线的CAN卡的设计与实现

现场总线CAN(Controller Area Network控制器局域网络)以其高性能、高可靠性及独特的设计,越来越受到人们的重视和青睐,

2009-10-25 10:54:58 816

816

ARINC429 总线是一种重要的航空数据总线标准,是飞机航电系统数字信息传递的主要途径之一。本文给出一种PCI 总线ARINC429 通信卡的实现方法,利用FPGA 实现了ARINC429 协议的编解码,测试表明

2011-05-18 18:08:33 37

37 本文介绍的DSP与PCI总线的接 接方案灵活简单,减小了布板的复杂度,简化了PCI总线要求的时序,缩短了开发周期。采用该方案设计的数据处理系统工作稳定,已应用在低频信号检测领域

2011-08-19 16:11:06 1660

1660

ARINC429 总线是一种重要的航空数据总线标准,是飞机航电系统数字信息传递的主要途径之一。本文给出一种PCI 总线ARINC429 通信卡的实现方法,利用FPGA 实现了ARINC429 协议的编解码,测试表明

2011-09-30 16:28:37 43

43 文中介绍了PCI9656的内部结构和功能,讨论了其WDM驱动开发过程,分析了其局部总线在进行DMA传输时的配置时序,提出了一些设计中需要注意的问题。实际应用结果表明,该总线接口性能稳定

2011-10-19 14:56:51 31

31 在pcb layout中我们可以从下面的几点来分析一下PCI,PCI总线的布线有什么殊要求,如何做好PCI总线的布线,首先,PCI系统是一个同步时序的体统,而且是Common clock方式进行的。

2011-11-09 15:48:37 7914

7914 出了一种PCI总线从设备的CPLD实现方法。该方法遵从PCI规范2.2版,实现了资源自动配置并且支持数据突发传输。试验证明该方法的有效性,其突发传输速率可达20 MBs -1 。

2011-11-30 17:06:11 60

60 通过对刀片服务器基本概念、主要组成以及内部架构的分析和研究,针对刀片与主板之间的高速通信需求,采用PCI总线作为系统的数据通信协议,给出了PCI局部总线的详细分析和设计流

2012-02-01 13:42:57 22

22 本文给出了用可编程逻辑器件GAL配合ISA总线模拟I2C总线时序来对FI1256 MK2进行控制的方法。该方法与PCI总线进行模拟的方法相类似。

2012-03-27 11:33:15 2687

2687

PCI总线是目前最为流行的一种局部性总线 通过对PCI总线一些典型功能的分析以及时序的阐述,利用VetilogHDL设计了一个将非PCI功能设备转接到PC1总线上的IP Core 同时,通过在ModeISim SE PLU

2012-04-01 15:06:44 40

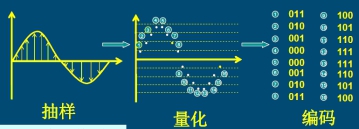

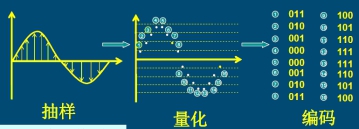

40 在使用电子测量仪器的时候,波形查看是最常用到的功能,那么波形的采集和重构一般是怎样实现呢?在采集方法上比较典型的两种仪器就是示波器和功率分析仪,今天小编就简单介绍一下瞬态、稳态测量仪器常见的波形采集方法。

2017-07-28 15:23:55 1598

1598

并行总线波形捕获与分析。

2018-06-25 15:44:00 3560

3560 时序分析是以分析时间序列的发展过程、方向和趋势,预测将来时域可能达到的目标的方法。此方法运用概率统计中时间序列分析原理和技术,利用时序系统的数据相关性,建立相应的数学模型,描述系统的时序状态,以预测未来。

2019-11-15 07:02:00 2570

2570

PCI总线的信号定义 PCI总线是一条共享总线,在一条PCI总线上可以挂接多个PCI设备。这些PCI设备通过一系列信号与PCI总线相连,这些信号由地址/数据信号、控制信号、仲裁信号、中断信号等多种

2021-07-18 09:55:32 1981

1981

电子发烧友App

电子发烧友App

评论