我在知乎看到了多bit信号跨时钟的问题,于是整理了一下自己对于跨时钟域信号的处理方法。

2022-10-09 10:44:57 4598

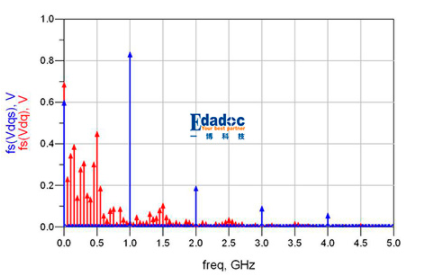

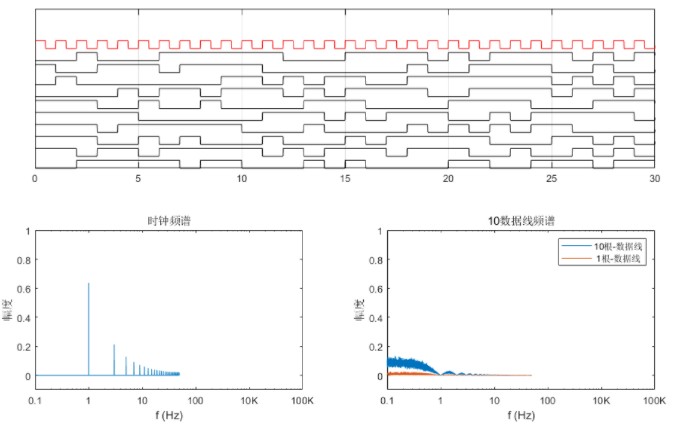

4598 时钟抖动技术适合于各种周期性的脉冲信号,典型的是电力电子设备中的PWM电压和数字电路中的时钟信号。

2023-09-11 10:55:34 503

503

时钟信号具有什么样的基本特征呢?如何区分时钟和数据呢?

2021-10-29 07:00:05

描述ITS1A 时钟板这是老式 ITS1A 闸流管的时钟。我不认为我的第一个六管时钟会是 ITS1A 时钟,但在我拿到一些管子并花了一点时间让它们点亮(然后能够控制显示的内容)之后,它似乎是一个构建

2022-09-07 07:06:18

AD9272的帧时钟FCO和数据时钟DCO会随着采样频率的变化而变化吗?

2023-12-14 07:09:44

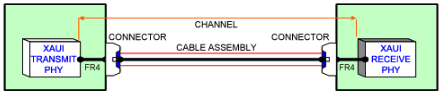

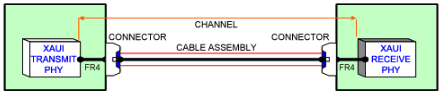

信号。时钟和数据走线对设计用于100欧姆差分阻抗。对于实验室评估,标准的50欧姆脉冲/数据发生器可以向输入提供信号,50欧姆端接的高带宽示波器采样头可用于终止输出

2019-11-04 09:02:29

M37046G-16时钟和数据恢复产品介绍M37046G-16报价M37046G-16代理M37046G-16现货,深圳市首质诚科技有限公司, M37046G-16是一个四通道25.78 Gbps

2018-11-29 16:28:12

SATA电源线和数据线接口定义SATA是Serial ATA的缩写,即串行ATA。2001年,由Intel、APT、Dell、IBM、希捷、迈拓这几大厂商组成的Serial ATA委员会正式确立

2021-10-29 07:25:46

SI5010 时钟和数据恢复(CDR) 计时 评估板

2024-03-14 22:30:31

SI5013 时钟和数据恢复(CDR) 计时 评估板

2024-03-14 22:30:31

SI5020 时钟和数据恢复(CDR) 计时 评估板

2024-03-14 22:30:31

串口通信协议,通过示波器查看信号线和数据线的波形如图所示,数据线是双向传输,请问如何分析数据?如何将双向传输的信号拆分出来?

2016-02-24 15:13:41

这是测试SHT1X温度传感器的程序,但为什么没有定义时钟引脚和数据引脚是输入还是输出?哪位大神知道的,可以解答一下吗?

2017-03-28 10:24:06

在SPI双机通信中,时钟信号由主机提供,那么从机向主机发送数据时需要时钟信号吗?从机是怎样通知主机产生时钟信号的?

2024-03-14 06:49:32

亲爱的大家,我对时钟信号和数据信号进行采样,想要馈送到IDDR2,但它需要两个时钟。所以我的采样时钟信号无法直接馈入IDDR2,需要反向采样时钟信号,如何反转它使反转信号没有任何偏斜&与采样

2019-06-11 06:11:26

如果没有硬件和热电偶,如何用MAX虚拟创建信号源和数据采集卡实现数据采集的温度任务?谢谢

2015-05-27 16:30:56

EVALZ-ADN2915,ADN2915用于ADN2915 6.5至11300 MHz时钟和数据恢复的评估板设置和应用。 ADN2915提供量化,信号电平检测和时钟/数据恢复的接收器功能,可实现

2019-02-21 09:47:49

用飞线连接debugger的时钟线和数据线就可以发射未调制的单载波的原理吗?

2016-02-22 14:42:56

你们好,

我们正在使用AD9779A进行设计,有如下疑问:

(1) 使用AD9779A的数据时钟信号(DATACLK)作为FPGA内部PLL的参考时钟,再用FPGA PLL产生的时钟信号把数据

2023-12-20 07:12:27

了TensorFlow2.0Beta版本,同pytorch一样支持动态执行(TensorFlow2.0默认eager模式,无需启动会话执行计算图),同时删除了杂乱低阶API,使用高阶API简单地构建复杂神经网络模型,本文主要分享用高阶API构建模型和数据集使用。

2020-11-04 07:49:09

检索光信号中的时钟和数据灵敏度

2022-10-09 15:54:47

高速信号、时钟及数据捕捉:数据转换系统背后的运作原理— 作者:Ian King 美国国家半导体公司应用技术工程师随着仿真/数字转换器的数据转换取样率提高至每秒千兆个取

2009-09-25 10:42:19 0

0 ADN2817/ADN2818可提供下列接收器功能:量化、信号电平检测、时钟和数据恢复,适用于从10 Mbps到2.7 Gbps的连续数据速率。二者均可自动锁定至所有数据速率,而无需外部参考时钟或

2023-02-14 10:05:22

高速信号,时钟及数据捕捉:数据转换系统背后的运作原理:隨著模擬/數字轉換器的數據轉換取樣率提高至每秒千兆個取樣 (GSPS) 以上的水平,數據轉換系統必須作出相應的配合

2010-01-16 16:38:43 28

28 介绍了时钟和数据恢复器件ADN2814的主要性能、内部结构和引脚功能,给出了ADN2814在信号传输中的应用电路,同时介绍了系统中时钟和数据恢复器件的选择方法及应用分析。

2010-12-14 10:21:28 23

23 MAX9489/MAX9471多输出时钟发生器构建集成时钟源

摘要:与典型的“本地”时钟方案相比,集成的多输出时钟发生器有许多优势。本文探讨了集中时钟发生器(如

2008-10-04 20:43:25 922

922

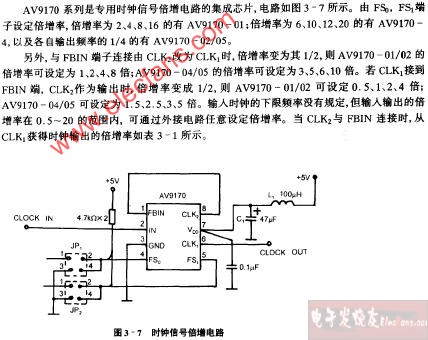

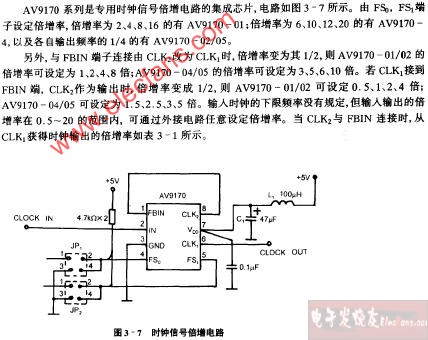

时钟信号倍增电路图

2009-07-14 17:18:36 741

741

安森美时钟管理产品系列增加新的时钟和数据驱动IC

应用于绿色电子产品的首要高性能、高能效硅方案供应商安森美半导体(宣布扩充公司的时钟驱动器系列,推出NB7L

2010-02-01 13:42:09 866

866 安森美推出新的时钟和数据多工器产品 安森美半导体(ON Semiconductor,美国纳斯达克上市代号:ONNN)进一步扩充多工器产品阵容,新推出NB6VQ572M、NB6LQ572、N

2010-04-27 10:27:23 661

661 本文解释了在时钟和数据信号从一个时钟域跨越到另一个时钟域所发生的许多类型的同步问题。在任何情况下,本文所包含的问题都涉及到相互异步的时钟域。随着每一个问题的提出,

2011-04-06 17:39:49 51

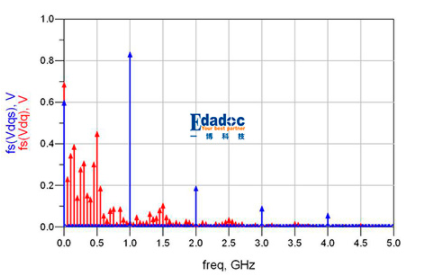

51 本文简要介绍了SSC扩频时钟的基本概念以及如何使用力科示波器进行信号的扩频时钟的测试。

2011-05-17 11:23:34 4648

4648

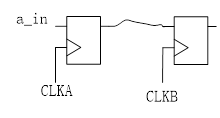

信号在不同时钟域之间的转换是复杂数字电路设计中不可缺少的一部分,直接锁存法和锁存反馈法可处理控制信号的同步,异步FIFO在跨时钟的数据交换方面具有高效的优势,本文设计的

2011-08-22 12:07:12 5848

5848

跨时钟域信号的同步方法应根据源时钟与目标时钟的相位关系、该信号的时间宽度和多个跨时钟域信号之间的时序关系来选择。如果两时钟有确定的相位关系,可由目标时钟直接采集跨

2012-05-09 15:21:18 63

63 基于LabVIEW的虚拟信号发生和数据采集系统。

2016-01-20 16:07:48 122

122 在FPGA的源同步的系统设计中,常常我们会碰到把随路时钟和数据一同输出的情形,如同下面的系统: 在这样的系统中,要求输出时钟o_clk和o_dat要由严格的相位对齐关系,一般是边沿对齐或者中心对齐。 那么如何才能保证上述相位对齐关系呢? (1) 第一种做法(这样用的人不少)。

2019-10-12 17:59:00 11092

11092

锁相环是电路功能中最通用的。它们用于时钟处理器(相当良性的情况),以及在固定和调谐频率发射机和接收机建立调谐。

2017-05-16 10:42:41 8

8 本文介绍了混合信号示波器探测模拟和数字信号的方法。

2017-10-15 11:46:53 11

11 由于现在的模数转换器的数据转换采样率正在移动到千兆采样每秒(GSPS)的范围内,系统需要能够具有如此高的转换率,并且支持模拟组件必须产生和放大高频信号。除了模拟信号路径之外,设计者应该充分理解的电路区域是采样时钟和以高比特率捕获数字数据,信号路径设计器的这个问题将为这两个关键领域提供建议的解决方案。

2018-05-14 15:50:19 10

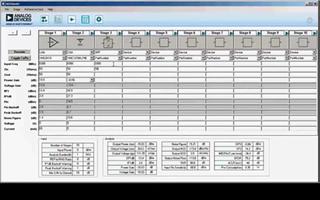

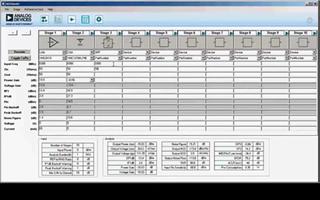

10 本视频中,我们将带您了解构建、配置和保存信号链的步骤。我们将说明如何从数据库中加载器件,如何使用器件选型向导以及如何输入自定义器件的数据。

2018-06-01 10:47:00 3297

3297

由于今天的模数转换器的数据转换采样率正在移动到千兆采样每秒(GSPS)的范围内,系统需要能够具有如此高的转换率,并且支持模拟组件必须产生和放大高频信号。

2018-05-23 10:06:48 11

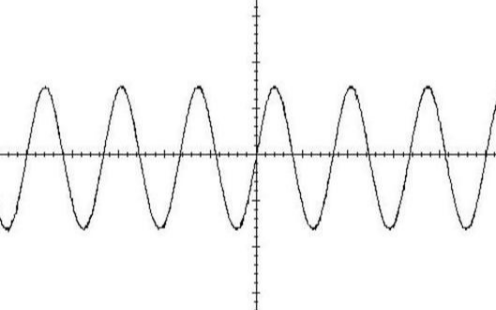

11 首先,我们看一下时钟信号中最常见到的波形 - 矩形波(尤其是方波更常用)。在较低时钟频率的系统中我们看到的基本上都是以矩形波为主的时钟信号,因为电路基本上都是靠时钟的边沿(上升沿或下降沿)进行

2018-12-06 11:53:10 59987

59987

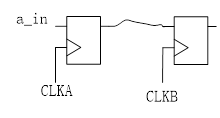

想象一下,如果频率较高的时钟域A中的信号D1 要传到频率较低的时钟域B,但是D1只有一个时钟脉冲宽度(1T),clkb 就有几率采不到D1了,如图1。

2019-02-04 15:52:00 10841

10841

你知道模拟信号和数字信号之间的区别吗?之前我们知道,我们必须知道什么是模拟信号和数字信号是什么。

2019-06-13 17:43:58 3854

3854 模拟信号、数字信号如何得到兼容呢?模拟信号和数字信号兼容问题也不是什么难度;因为模拟信号和数字信号本身都是A/D、D/A的相互设备转换。

2019-06-19 17:41:47 2879

2879 你知道模拟信号和数字信号之间的区别吗?之前我们知道,我们必须知道什么是模拟信号和数字信号是什么。

2020-01-09 15:12:49 11702

11702

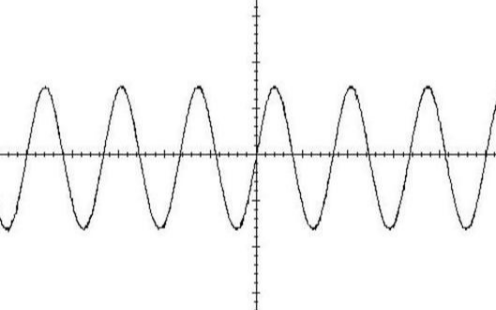

时钟信号是一个脉冲信号,而数据信号是伪随机码。在较长的时间轴上他们表现出来的形态是这样子的。

2021-04-19 13:52:35 6164

6164

在本文中,将详细研究这两类隔离-调制器的输出数据信号完整性。并通过简单的电磁干扰(EMI)测试设置、对由这两类-调制器的高频时钟信号产生的EMI进行比较。 对输出数据信号完整性和时钟信号电磁干扰

2020-11-18 14:59:50 995

995 本文档的主要内容详细介绍的是汇编四位机写的语音和数码管时钟程序免费下载。

2020-12-23 08:00:00 3

3 ADN2807:155/622 Mb/s时钟和数据恢复IC,带集成限幅放大器数据表

2021-04-17 16:50:34 2

2 AD808:带量化器和时钟恢复和数据重定时数据表的光纤接收器

2021-04-28 17:09:08 2

2 ADN2806:622 Mbps时钟和数据恢复IC数据表

2021-05-08 11:26:35 8

8 ADN2819:多速率至2.7 Gb/s时钟和数据恢复IC,带集成限幅放大器数据表

2021-05-08 14:22:27 13

13 ADN2811:OC-48/OC-48 FEC时钟和数据恢复数据表

2021-05-08 16:53:57 27

27 ADN2815:连续速率10 Mb/s至1.25 Gb/s时钟和数据恢复IC数据表

2021-05-09 14:39:25 6

6 ADN2804:带集成限幅放大器的622 Mbps时钟和数据恢复IC产品说明书

2021-05-09 16:46:25 1

1 ADN2813:连续速率10 Mb/s至1.25 Gb/s时钟和数据恢复IC,带集成限幅放大器数据表

2021-05-09 18:05:48 1

1 AD800/AD802:时钟恢复和数据重定时锁相环数据表

2021-05-18 14:11:56 9

9 AD807:带量化器和时钟恢复和数据重定时数据表的光纤接收器

2021-05-19 08:29:38 12

12 ADN2816:连续速率10 Mb/s至675 Mb/s时钟和数据恢复IC数据表

2021-05-25 09:45:45 2

2 ADN2805:1.25 Gbps时钟和数据恢复IC数据表

2021-05-25 10:58:12 3

3 ADN2817/ADN2818:连续速率10 Mbps至2.7 Gbps时钟和数据恢复IC数据表

2021-05-25 20:08:35 7

7 如果用单独的时钟信号板,一般采用什么样的接口,来保证时钟信号的传输受到的影响小?

2022-09-16 08:58:49 1918

1918

电子发烧友网站提供《最小零件OLED字时钟构建.zip》资料免费下载

2023-02-03 11:43:36 6

6 在第2部分中,我们了解到耦合到时钟信号上的噪声看起来是正弦的,并且与输入信号的频率相同。有了这种理解,当数字数据信号到数据转换器时钟发生串扰时,频域中会发生什么就变得更加清晰。如第1部分所述,来自

2023-02-25 10:58:00 561

561

高速串行链路的表征取决于SI工程师发现、理解和解决严重抖动问题的能力。在本讨论中,我们假设 PHY(物理层)或 SerDes(串行器-解串器)设备的时钟和数据恢复 (CDR) 模块符合适用于该设备

2023-04-03 11:27:21 995

995

基于8位数码管显示0-F和数字时钟的设计

2023-04-11 16:56:02 1

1 单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single

2023-04-13 09:11:37 912

912 FIFO是实现多位宽数据的异步跨时钟域操作的常用方法,相比于握手方式,FIFO一方面允许发送端在每个时钟周期都发送数据,另一方面还可以对数据进行缓存。需要注意的是对FIFO控制信号的管理,以避免发生

2023-05-11 14:01:27 1641

1641

电子发烧友网站提供《如何控制IoT ONE数码时钟-背光和数码管.zip》资料免费下载

2023-06-14 14:58:06 0

0 电子发烧友网站提供《如何控制IoT ONE 数码时钟-背光和数码管.zip》资料免费下载

2023-06-14 14:32:33 0

0 跨时钟域是如何产生的呢?现在的芯片(比如SOC,片上系统)集成度和复杂度越来越高,通常一颗芯片上会有许多不同的信号工作在不同的时钟频率下。

2023-06-27 11:39:41 897

897

电子发烧友网站提供《复古游戏时钟开源构建.zip》资料免费下载

2023-07-05 10:55:46 0

0 电子发烧友网站提供《Arduino构建乐高时钟.zip》资料免费下载

2023-07-06 15:02:17 0

0 电子发烧友网站提供《世界上最准确的7时区时钟构建.zip》资料免费下载

2023-07-13 11:31:20 0

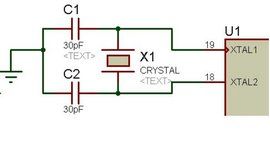

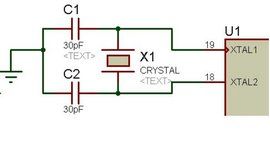

0 时钟电路用于产生稳定的时钟信号,常见于数字系统、微处理器、微控制器、通信设备等。时钟信号用于同步各个电子元件的操作和数据传输,确保系统的正常运行。

2023-08-03 14:46:04 1242

1242 单位宽(Single bit)信号即该信号的位宽为1,通常控制信号居多。对于此类信号,如需跨时钟域可直接使用xpm_cdc_single,如下图代码所示。参数DEST_SYNC_FF决定了级联触发器

2023-08-16 09:53:23 462

462

电子发烧友网站提供《如何构建更好的云:利用统一的虚拟化存储和数据中心交换矩阵.pdf》资料免费下载

2023-08-28 10:19:52 0

0 芯片为什么要时钟信号 芯片是现代电子设备的核心组成部分,广泛应用于计算机、手机、电视等各个领域。芯片内部有着复杂的电子元件和电路结构,这些元件和电路结构需要进行同步操作,以实现正确的工作。因此,芯片

2023-09-01 15:38:11 1376

1376 电子发烧友网站提供《基于反序列化过采样数据的时钟和数据恢复单元.pdf》资料免费下载

2023-09-13 10:41:34 0

0 件、计算机、数字电路和通讯协议等设备的信号。它的主要作用是进行时序控制,使数据传输和处理的时序保持一致。时钟信号一般由计时器产生,其具有一定的周期性、稳定性和精度。 时钟信号的主要信号参数包括周期、频率、精度和占空比等,

2023-09-15 16:28:12 1765

1765 芯片为什么需要时钟信号? 在我们日常生活中,我们所使用的各种电子设备都需要一个时钟信号来进行计时和同步,例如:手机、电脑、电视、汽车、机器人、智能家居等设备都需要时钟信号。对于各种这些电子设备

2023-09-15 16:28:14 1368

1368 时钟信号怎么产生的 时钟信号是一种重要的信号,它在电子设备中广泛应用。时钟信号的产生与传输是现代电子设备中不可或缺的基础技术之一。时钟信号的精确性和准确性是现代电子设备能够实现高速计算等复杂操作

2023-09-15 16:28:22 1495

1495 是数据信号(SDA)。SCL信号是在IIC通信中非常重要的一个信号,它确定了数据的传输速率以及同步时序。 IIC时钟信号的产生需要硬件支持,一般通过外部晶振或者内部时钟源产生。在IIC总线使用过程中,时钟信号的频率很重要,必须要与所有设备的时钟频率保持一致。一般来说,为了保证

2023-09-19 17:16:02 735

735 电子发烧友网站提供《基于ASP和数据库技术构建的网络教学平台.pdf》资料免费下载

2023-10-08 11:40:57 0

0 时钟信号的同步 在数字电路里怎样让两个不同步的时钟信号同步? 在数字电路中,时钟信号的同步是非常重要的问题。因为在信号处理过程中,如果不同步,就会出现信号的混淆和错误。因此,在数字电路中需要采取一些

2023-10-18 15:23:48 771

771 LVDS中的时钟脉冲信号是干什么的? LVDS(Low Voltage Differential Signaling)中的时钟脉冲信号(Clock)是用于同步数据传输的,是整个LVDS接口的重要

2023-10-18 15:38:20 661

661 双路LVDS信号和单路的时钟频率有什么关系?是一个时钟内传输两个像素的数据吗? 双路LVDS信号是一种在高速数据传输上应用广泛的接口,它利用微小的电压摆动来传输数据。在双路LVDS信号中,数据被分成

2023-10-18 15:38:22 972

972 什么器件可以产生时钟信号?时钟信号是用来做什么用的?时钟信号起什么作用? 时钟信号是一个精确的电信号,它可以通过电子器件来产生,并且具有一定的频率和周期。时钟信号在电子系统中具有非常重要的作用,因为

2023-10-25 15:07:45 636

636 时钟电路是指用于产生稳定、精确的时间基准信号的电路。这种电路通常采用晶体振荡器或者其他稳定的振荡器作为时钟源,产生固定频率的信号。时钟信号被广泛应用于数字系统、通信系统、计算机系统等各种电子设备中,用于同步和控制各种操作和数据传输。

2023-11-17 09:50:08 769

769 信号、系统和数字信号处理知识整理

2023-12-08 10:47:12 184

184

什么是时钟信号?数字电路的时钟信号是怎么产生呢? 时钟信号,也称为时钟脉冲,是用于同步数字电路中所有操作的基本信号。它提供了一个参考频率,使得所有电路元件都能按照同样的节奏进行工作。时钟信号

2024-01-25 15:40:52 908

908 基准,使得整个芯片能够以协调一致的方式进行工作。 时钟信号的重要性主要表现在以下几个方面: 1. 同步功能:芯片内部的各个模块需要以同步的方式进行操作,以确保数据的准确传输和处理。时钟信号为芯片内部提供了一个统一的时

2024-01-29 18:11:31 625

625

电子发烧友App

电子发烧友App

评论