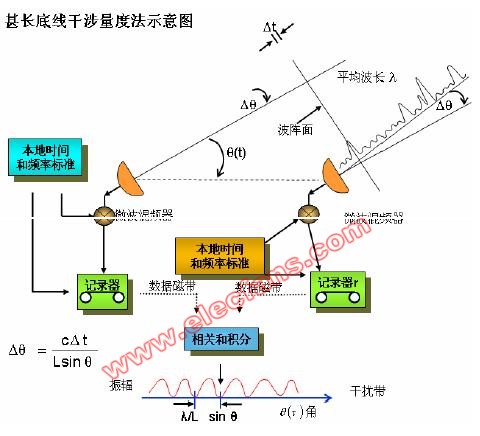

本文介时钟频率概念及其对系统性能的影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动的有效方法。

2012-03-10 09:55:23 4544

4544

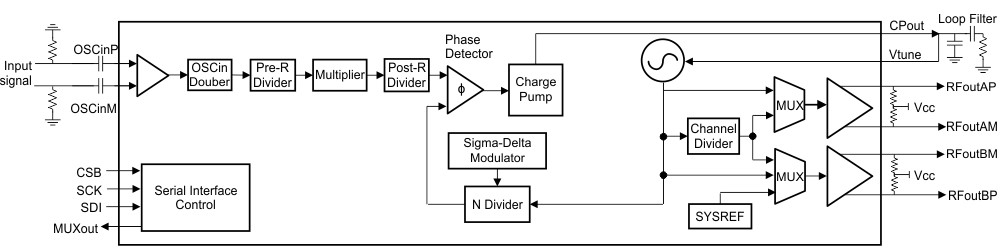

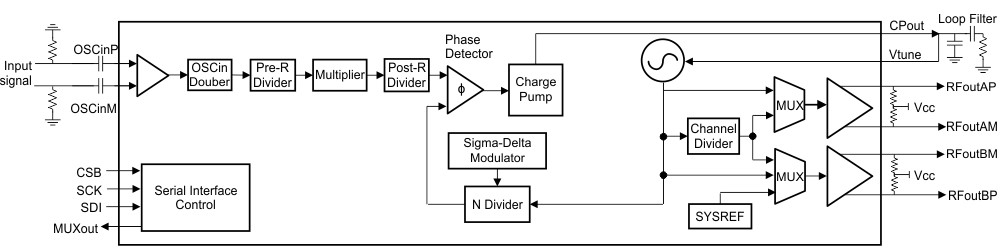

Analog Devices, Inc.(ADI),最近发布了一款提供领先相位噪声性能的PLL频率合成器ADF4153A。

2012-11-01 09:09:20 1497

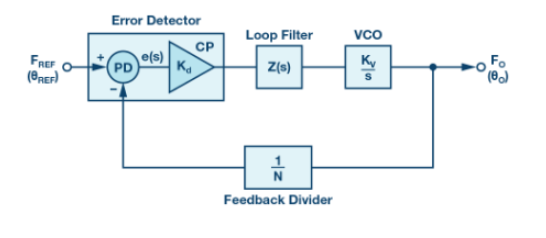

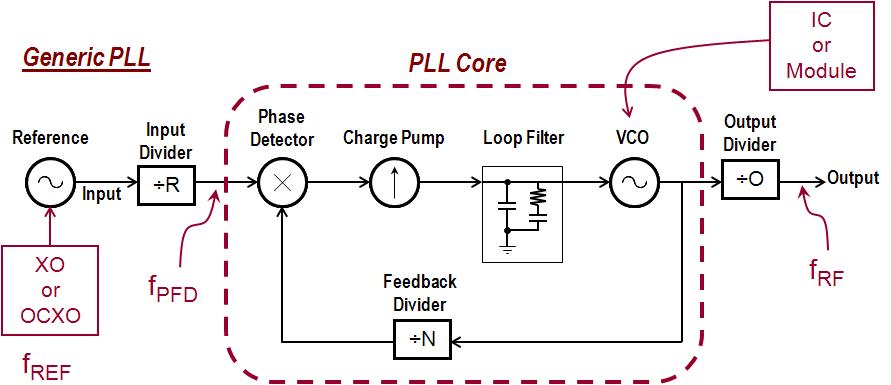

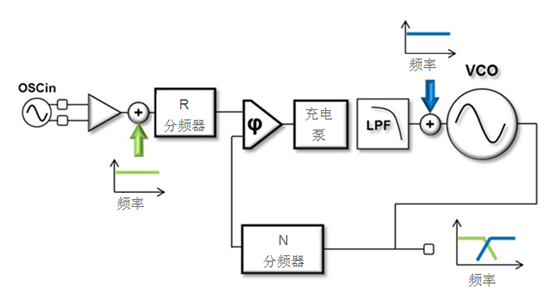

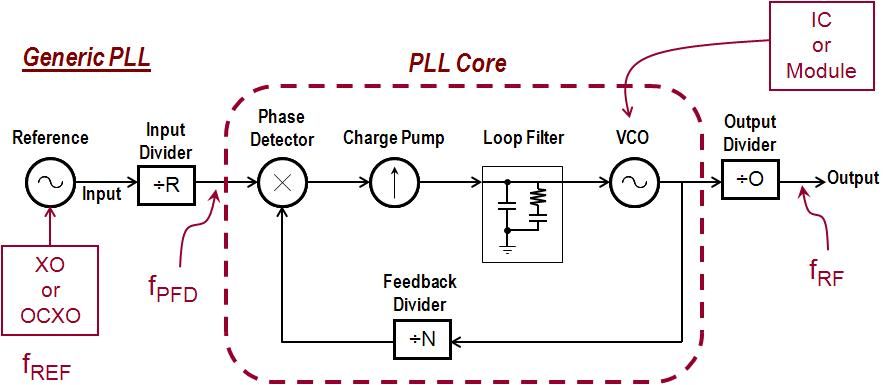

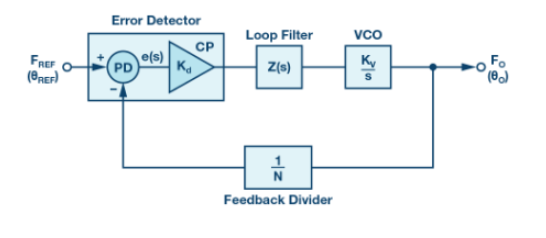

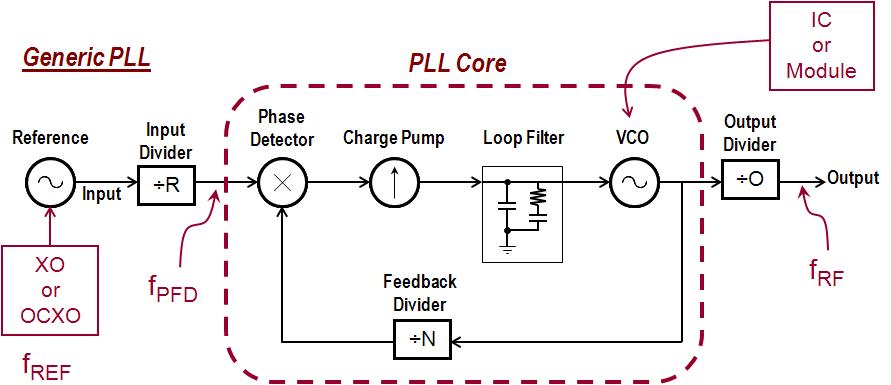

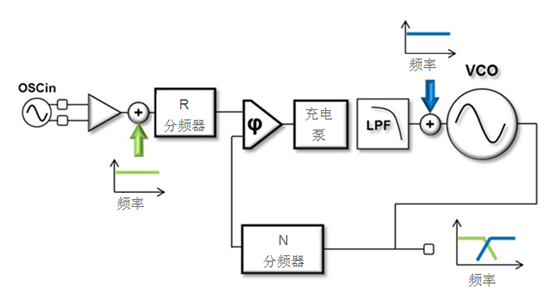

1497 。当比较结果处于稳态,即输出频率和相位与误差检测器的输入频率和相位匹配时,我们说PLL被锁定。就本文而言,我们仅考虑ADI ADF4xxx系列PLL所实现的经典数字PLL架构。 该电路的第一个基本元件是鉴频鉴相器(PFD)。PFD将输入到REFIN的频率和相位与反馈到RFIN的频率和相位进

2021-03-02 16:34:02 3806

3806

已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性能架构的实现。

2022-10-14 10:30:36 2025

2025 本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率合成器为例,详细介绍了设计过程和步骤。从规格选择、电路配置

2023-10-26 15:30:51 483

483

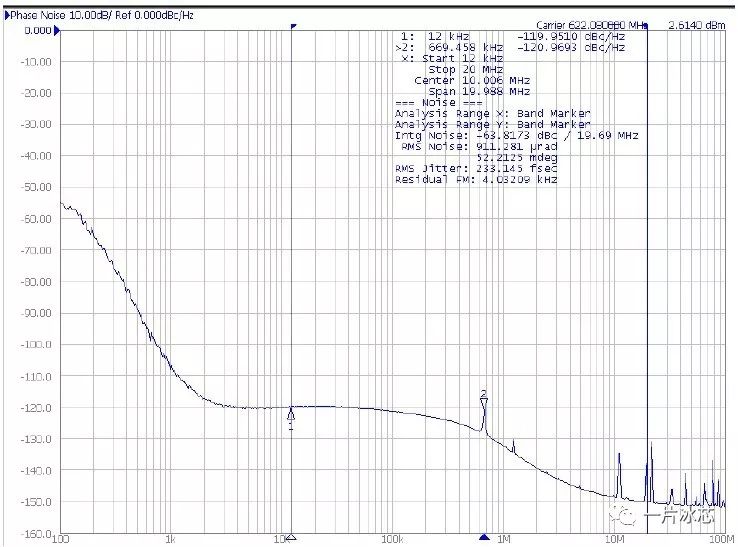

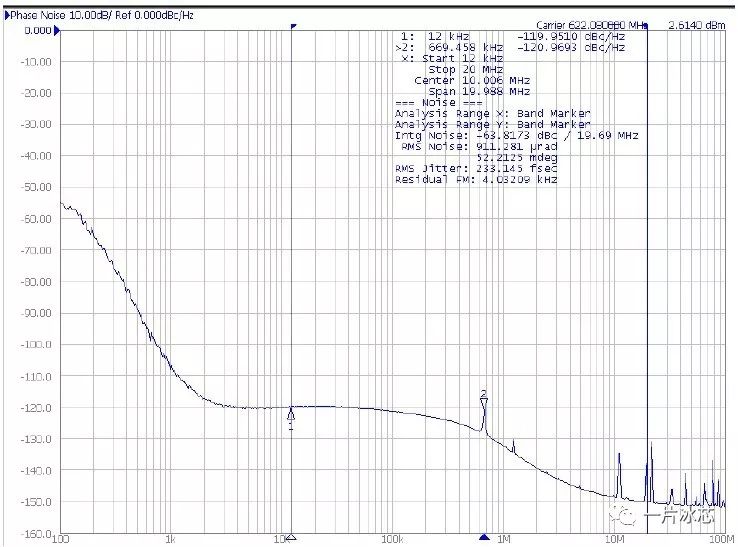

相位噪声转换到抖动的基本思想就是对相位噪声曲线进行积分。

2023-10-30 16:06:01 1025

1025

)如何影响PLL相位噪声的示例。例如,文献中对ADP3334和ADP150 LDO为ADF4350供电时的性能进行了比较。ADP3334调节器的集成均方根噪声为27 μV(40多年来,从10 Hz至100

2018-12-21 09:05:27

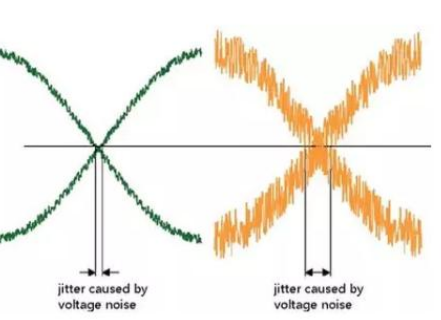

测量抖动性能的设备内,这种机理也表现得很明显。 时钟性能测量 工程师常常会评估无意义的实验室结果;而时钟性能测量的问题尤其严重。例如,你可使用示波器和相位噪声分析仪(PNA)测量随机抖动。不过,结果

2018-09-19 11:47:50

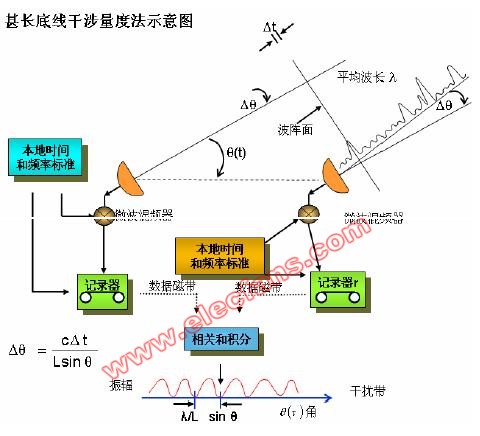

、相位噪声的意义 频率源的相位噪声是一项非常重要的性能指标,它对电子设备和电子系统的性能影响 很大,从频域看它分布在载波信号两旁按幂律谱分布。用这种信号不论做发射激励信 号,还是接收机本振信号以及各种频率

2017-10-09 10:44:20

我正在使用E5052B信号源分析仪来获取相位噪声数据,载波频率为20.460802MHz,频率范围为1Hz至5MHz。我试图将导出为.csv文件的相位噪声数据转换为RMS抖动(弧度),但是我在整个

2018-10-10 17:50:29

新兴的PLL + VCO (集成电压控制振荡器的锁相环)技术能够针对蜂窝/4G、微波无线电防务等应用快速开发低相位噪声频率合成器,ADI集成频综产品的频率覆盖为25 MHz到13.6 GHz。

2019-08-01 07:23:09

~156.25MHz范围的低抖动时钟源。在理想的供电条件下,小数分频PLL可在1 0kHz~20MHz频段内提供低于lps RMS的抖动性能。相反,在有电源噪声的环境中,振荡器很难满足其数据手册中标明的相位抖动参数

2018-09-26 14:33:58

`这些高性能系统中的系统设计人员将选择超低相位噪声振荡器,并且从噪声角度来讲,信号链的目标就是使振荡器相位噪声曲线的恶化最小。这就要求对信号链上的各种元器件做残余或加性的相位噪声测量。 最近发布

2019-03-19 22:09:54

和高相位检测器频率可实现非常低的带内噪声和集成抖动。高速 N 分频器没有预分频器,从而显著减少了杂散的振幅和数量。还有一个可减轻整数边界杂散的可编程输入乘法器。LMX2594 允许用户同步多个器件

2021-03-24 15:59:47

”架构,其输出频率是鉴相器频率的整数倍。为提供较小的频率步进,整数倍增因子必须非常大。大量本振相位噪声源于参考路径,并被PLL频率倍增因子所放大,这将导致PLL输出端产生很高的带内噪声。小数N分频

2018-08-21 09:21:18

,REFIN的高相位噪声(图6)由低通滤波器滤除。由PLL的参考和PFD电路贡献的所有带内噪声都被低通滤波器滤除,只在环路带宽外(图8)留下低得多的VCXO噪声(图7)。当输出频率等于输入频率时,PLL配置最简单。这种PLL称为时钟净化PLL。对于此类时钟净化应用,建议使用窄带宽(

2019-10-02 08:30:00

。图2中有一个在频域中工作的负反馈控制环路。当比较结果处于稳态,即输出频率和相位与误差检测器的输入频率和相位匹配时,我们说PLL被锁定。就本文而言,我们仅考虑ADI公司ADF4xxx系列PLL所实现

2019-01-28 16:02:54

特征•单个3.3V电源•高性能时钟发生器,包括集成频率合成器的晶体振荡器电路•低输出抖动,低至380 fs(rms集成在10 kHz–20 MHz之间)•高频下的低相位噪声;在708 MHz时,在

2020-09-10 17:45:08

一、什么是相位噪声? 相位噪声表示在波形的频域中,由相位(频率)的快速,短期,随机波动组成。这是由时域不稳定性(抖动)引起的。 确保不要将相位噪声与抖动混淆。抖动 是一种描述晶振在时域

2021-03-15 14:13:57

ADIsimPLL中建模。从所示的ADIsimPLL曲线中可以看出,REFIN的高相位噪声(图6)由低通滤波器滤除。由PLL的参考和PFD电路贡献的所有带内噪声都被低通滤波器滤除,只在环路带宽外(图8)留下

2018-10-25 10:25:31

。相位噪声通常定义为一个振荡器在某一偏移频率fm处1Hz宽带内的单边信号功率和信号的总功率比值,单位是dBc/Hz.通常表示为dBc/Hz@fm。相位噪声的形成因素主要三方面:· A区主要是晶体Q值来

2020-06-10 17:38:08

变化的敏感; A型我电荷泵的PLL频率合成器是在这项工作中提出。闭环系统的稳定是实现使用一个离散时间环路滤波器。 I型系统架构导致开关速度快。离散时间环路滤波器的相位/频率检测器和VCO调谐节点之间的隔离。因此性能可以达到一个良好的刺激。PLL博士论文_全集成频率综合器[hide][/hide]

2011-12-15 11:17:56

十分重要。

相位噪声

相位噪声(Phase Noise)是抖动在测量仪器上的表现,通常定义为一个振荡器在某一偏移频率fm处1Hz宽带内的单边信号功率和信号总功率比值,单位是dBc/Hz,通常表示为

2023-12-14 09:19:08

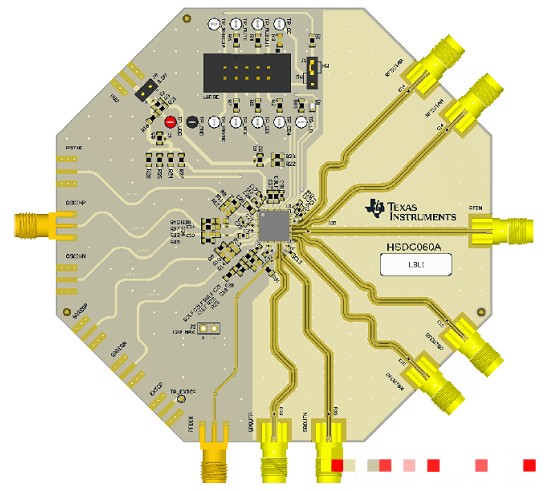

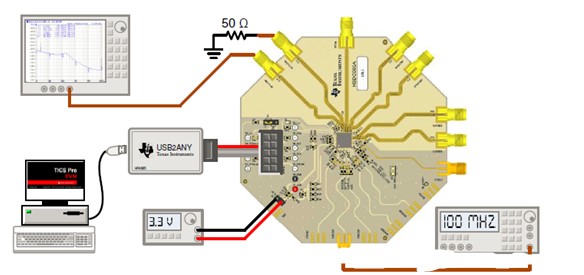

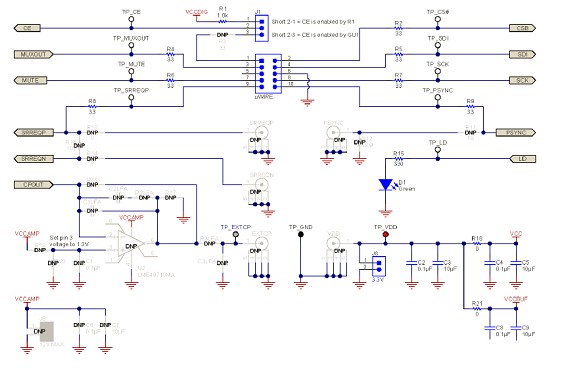

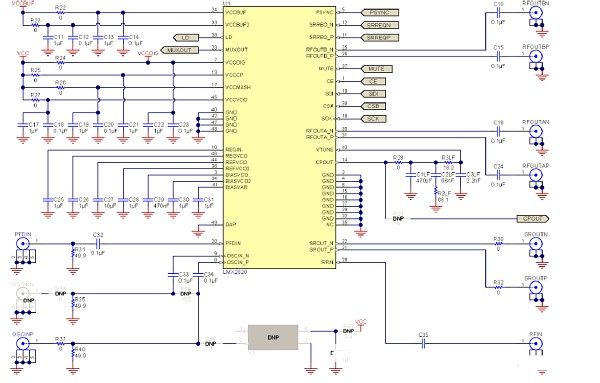

DC1795A,用于LTC6950的演示板,具有时钟分配的1.4GHz低相位噪声,低抖动PLL。演示电路1795A采用具有时钟分配的LTC6950,1.4 GHz低相位噪声,低抖动PLL。为了便于

2019-02-25 09:55:24

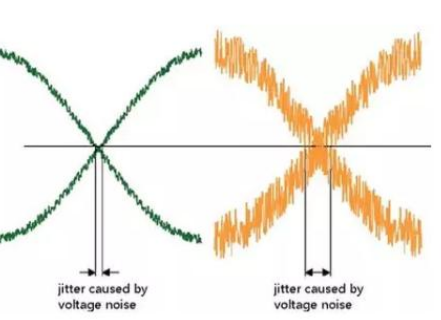

时钟频率的不断提高使相位噪声和抖动在系统时序上占据日益重要的位置。本文介其概念及其对系统性能的影响,并在电路板级、芯片级和单元模块级分别提供了减小相位噪声和抖动的有效方法。

2019-06-05 07:13:30

随着数据转换器的速度和分辨率不断提升,对具有更低相位噪 声的更高频率采样时钟源的需求也在不断增长。时钟输入面临 的积分相位噪声(抖动)是设计师在设计蜂窝基站、军用雷达 系统和要求高速和高性能时钟信号

2019-10-31 08:00:00

于相位噪声、锁定时间或杂散却并非如此。表1给出了环路带宽对这些性能指标的影响的大致参考。 性能指标最优带宽备注抖动BWJIT最优值一般为BWJIT。在低集成限制更高的一些情况下,有时较窄的环路带宽实际上效果更好。锁定时间无限VCO锁定时间随着环路带宽的增加而提高,但有时会受到VCO校准时间…

2022-11-16 07:56:45

本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLatinum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

2019-07-05 07:47:46

的时钟源。随着集成电路加工中功能器件的尺寸缩小,器件电源电压也呈下降趋势,包括PLL和其它混合信号功能所用的电源。然而,PLL的关键元件——“压控振荡器”(VCO)的实用技术要求并未随之大幅降低。许多高性能

2019-06-26 06:39:37

概述:LTC6945是一款高性能、低噪声、6GHz 锁相环 (PLL),包括一个基准分频器、具锁相指示器的相位-频率检测器 (PFD)、充电泵、整数反馈分频器和 VCO 输出分频器。

2021-04-09 06:34:49

什么是抖动和相位噪声?如何区分抖动和相位噪声?

2021-03-11 07:03:13

的方法。请注意环路带宽上方总相位噪声与VCO的跟踪调谐以及环路带宽下方总相位噪声与PLL的跟踪调谐。

图2:LMX2592预估相位噪声曲线图(带100-MHz相位检测器频率的6-GHz输出),借助

2018-08-31 09:46:39

频率为250MHz时,压控增益线性区频率覆盖范围是60~480MHz,在偏离中心频率600 kHz处的相位噪声为-108 dBc/Hz,较文献中传统的反相器延迟单元的环形VCO性能有明显的改善。说明

2021-02-25 07:39:43

、相位噪声、抖动、锁定时间和其他表示频率合成电路总体性能的特性。转换环路是基于PLL概念的另一类频率合成器,但采用不同的方法实现。如图1b所示,其反馈环路中使用的是集成下变频混频级,而不是N分频器,环路

2022-03-14 16:17:39

非常有用。VPOS_PLL 具有最差电源抑制性能,因此,是最灵敏的电源节点。该电源引脚驱动PLL 电路,包括参考输入频率、相位频率检测器和电荷泵。这些灵敏的功能模块决定着LO 信号的精度和相位性能,因此

2019-10-17 09:06:34

高信噪比=低ADC孔径抖动吗?在设计中,为了避免降低ADC的性能,工程师一般会采用抖动极低的采样时钟。然而,用于产生采样时钟的振荡器常常用相位噪声而非时间抖动来描述特性。那么,有木有方法将振荡器相位噪声转换为时间抖动呢?

2019-08-13 06:27:54

MHz这个频带范围内,某振荡器的相位噪声情况。图中,L(f)以功率谱密度函数的形式给出了边带噪声的分布,单位为dBc。中心频率的功率并不重要,因为抖动只反映了相位噪声(即调制)与“纯”中心频率处

2009-10-13 17:23:19

在本文中,我们将讨论抖动传递及其性能,以及相位噪声测量技术的局限性。 时钟抖动和边沿速率 图1显示了由一个通用公式表述的三种波形。该公式包括相位噪声项“φ(t)”和幅度噪声项“λ(t)。对评估的三个

2022-11-23 07:59:49

系统设计师通常侧重于为应用选择最合适的数据转换器,在向数据转换器提供输入的时钟发生器件的选择上往往少有考虑。然而,如果不慎重考虑时钟发生器的相位噪声和抖动性能,数据转换器动态范围和线性度性能可能受到严重的影响。

2019-07-30 07:57:42

易失性存储器并控制 PLL。因此,通过板载 MCU-IC 组合可以实现系统时钟频率的动态更新。开发人员可以使用可编程微控制器,为高性能时钟 IC 提供控制逻辑。这可以减少对板载 IC 和走线数量的需求

2018-08-27 09:46:58

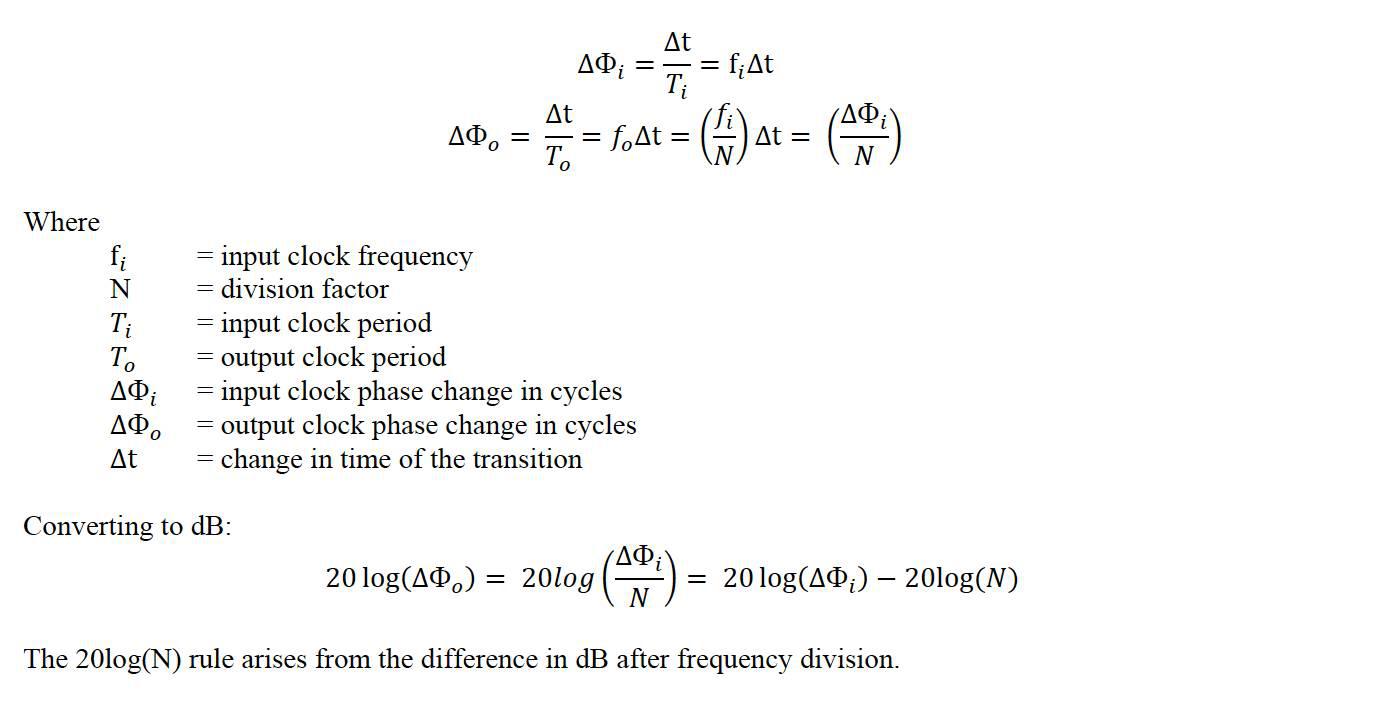

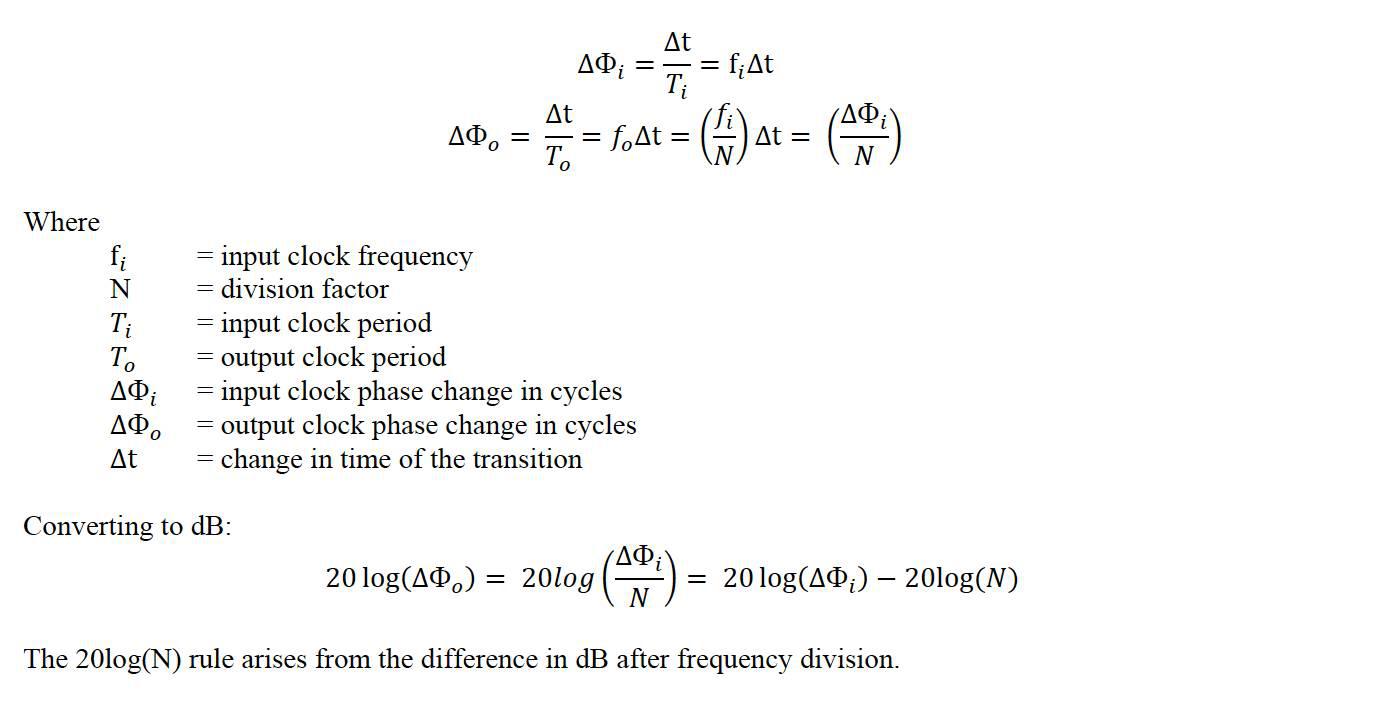

本期我将讨论在测量较低时钟频率的相位噪声和相位抖动时出现的一个非常常见的问题。在所有条件相同的情况下,我们通常期望分频的低频时钟产生比高频时钟更低的相位噪声。在数量上,你可能会记得这是20log(N

2021-06-24 07:30:00

高性能SiGe PLL与低相位噪声GaAs VCO配对,用于微波无线电

2019-09-26 11:03:44

PLL,5 kHz偏移的带内噪声(根据ADIsimPLL计算)为-95 dBc / Hz。RFMD VCO 915-191U检测适合应用的VCO,5 kHz偏移时的开环VCO相位噪声为-101 dBc

2018-10-26 11:48:38

详细介绍了具有外部VCO的完整12GHz,超低相位噪声分数N锁相环(PLL)的设计。它由高性能小数N分频PLL(MAX2880),基于运算放大器的有源环路滤波器(MAX9632)和12GHz VCO

2018-12-10 09:50:52

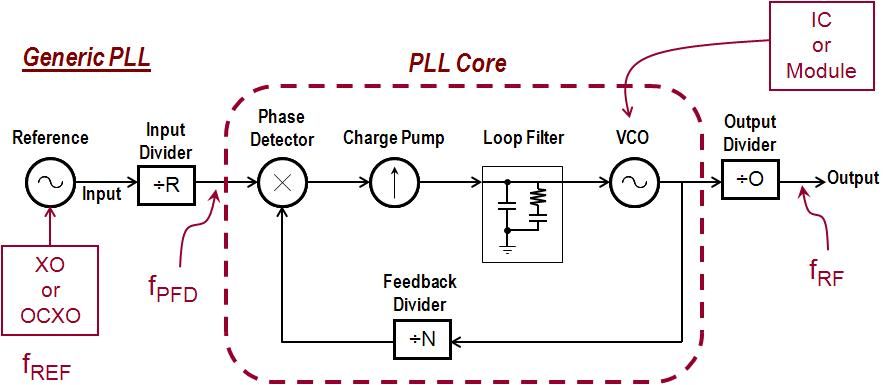

)可以极大地促进高性能架构的实现。大部分高频系统都使用传统的基于整数分频器的设计(图1)或基于分数N分频器的设计。不管是使用哪种设计,联合使用单个通用频率合成器IC和一个外部压控振荡器(VCO)通常都可以

2019-07-08 06:10:06

的范围在100fs至300fs之间。这个12kHz-20MHz的标准相位噪声集成范围包括锁相环 (PLL) 频带内和频带外 (VCO) 噪声的影响。基准时钟发生器的相位噪声性能需要在PLL环路带宽内

2018-09-05 16:07:30

而言是最优的,但对于相位噪声、锁定时间或杂散却并非如此。表1给出了环路带宽对这些性能指标的影响的大致参考。 性能指标最优带宽备注抖动BWJIT最优值一般为BWJIT。在低集成限制更高的一些情况下,有时

2018-08-29 16:02:55

概述:LTC6946是一款全集成型 VCO 的高性能、低噪声、6.39GHz 锁相环 (PLL),它包括一个基准分频器、具锁相指示器的相位-频率检测器 (PFD)、超低噪声充电泵、整数反馈分频器和 VCO 输出...

2021-04-13 06:31:10

频率检测器 (PFD) 频率的优点,可实现超低带内噪声和集成的抖动。ADF4377 的基本 VCO 和输出分频器可产生 800 MHz 至 12.8 GHz 的频率

2023-02-10 14:18:47

摘要:本文提出了一种对销相环频率合成器(PLL-FS)行为级建模后仿真,进行噪声和抖动性能分析的方法。新方法借鉴了最新的理论成果,结合工程实践,处于Top-Down 设计流

2009-12-14 11:32:35 9

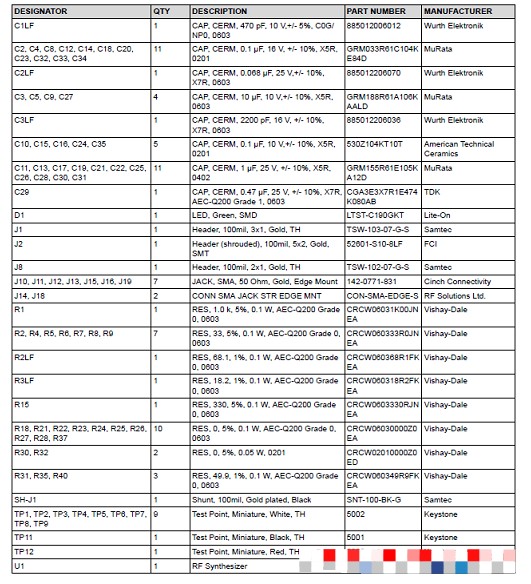

9 PLL频率合成器的噪声基底测量

在无线应用中,相位噪声是频率合成器的关键性能参数。像PHS、GSM和IS-54等相位调制蜂窝系统的RF系统设计均需要低噪声本地振荡(L

2010-04-07 15:25:21 22

22 (MxFE)时钟 应用。高性能PLL具有−239 dBc/Hz:归一化 带内相位噪声本底,超低1/f噪声,高 可实现超低的相位/频率检测器(PFD)频率 带内噪声和集成抖

2024-01-04 19:31:37

1/f噪声和高相位频率检测器(PFD)频率,可以实现超低的带内噪声和集成抖动。ADF4377的基本VCO和输出分频器产生的频率从800 MHz到12.8 GHz。

2024-02-26 09:29:37

锁相环(PLL)和相移键控(PSK)系统的相位噪声振荡器的相位噪声有可能导致相位变换的错误检测,即在用相位键控法进行数字调制时产生误码。例如,

2008-11-24 12:40:59 1796

1796

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16:50 3736

3736

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术方案。推导出的关系式提

2009-09-18 08:46:32 1461

1461

相位噪声和抖动的概念及其估算方法

时钟频率的不断提高使相位噪声和抖动在系统时序上占据日益重要的位置。本文介其概念及其对系统性能的影

2009-12-27 13:30:21 2173

2173

模数和数模转换器采样时钟内的抖动会对可实现的最大信噪比造成限制(参见参考文献部分van de Plassche著《集成模数和数模转换器》)。本应用笔记阐述了相位噪声和抖动的定义,绘制

2011-11-24 14:31:55 75

75 ADF4350/1系列是什么? ADF4350和ADF4351由一系列产品组成,这些产品将高性能整数N分频或小数N分频PLL与超低相位噪声VCO集成在一个小型LFCSP封装中。 ADF4350/1均为频率合成器(PLL+VCO),集领先

2012-06-08 18:06:49 185

185 采样时钟抖动可对高性能ADCs信噪比性能的灾难。虽然信噪比和抖动之间的关系是众所周知的,但是大多数振荡器都是根据相位噪声来指定的。

2017-08-03 10:57:33 13

13 该应用报告提出了在TI仪器上的CDCE72010抖动清理器和同步器PLL器件上获取的相位噪声数据。CDCE72010的相位噪声性能取决于基准时钟、VCXO时钟和CDCE72010本身的相位噪声。该应用报告显示了几个最流行的CDMA频率的相位噪声性能。此数据有助于用户为特定应用选择正确的时钟解决方案。

2018-05-15 10:58:53 7

7 合成器,整合了 PLL 内核与一个业界领先的低相位噪声 VCO。此外,PLLWizard 设计工具还可简化合成器的设计、准确地对其性能进行仿真、并使系统迅速启动和运行。

LTC6945 和 LTC6946 频率合成

2018-06-05 13:45:00 3207

3207

如果一个时钟的载波频率下降了N倍,那么我们预计相位噪声会减少20log(N)。例如,每个除以因子2的除法应该导致相位噪声减少20log(2)或大约6dB。这里的主要假设是无噪声的传统数字分频器。

2018-09-28 08:14:00 10038

10038

在产生高频,高线性度信号源时,低相位噪声至关重要。相位噪声是信号的不期望的变化或相位变化的量度。它在频域中测量并且等于时域中的抖动。使用PLL合成器时,总相位噪声由各种电路模块和元件的汇编组成,每个

2019-04-16 08:40:00 3411

3411

如果在给定的偏移频率下有一个相位噪声规范,那么应该将VCO和参考相位噪声信息提供给工具,例如ADIsimCLK,并使用它来优化闭环带宽实现预期目标。该过程实质上是调整闭环带宽以折衷参考和VCO相位噪声。

2019-04-10 10:32:46 6537

6537

本视频对ADI公司的高性能RF PLL和PLL VCO进行了简要介绍,展示我们在频率范围、带宽、低相位噪音和低功率杂散方面的技术进步,涵盖所有市场和应用领域。

2019-08-02 06:18:00 4763

4763 通过演示简要介绍锁相环(PLL)中可实现的领先相位噪声和杂散性能。

2019-05-21 06:23:00 5321

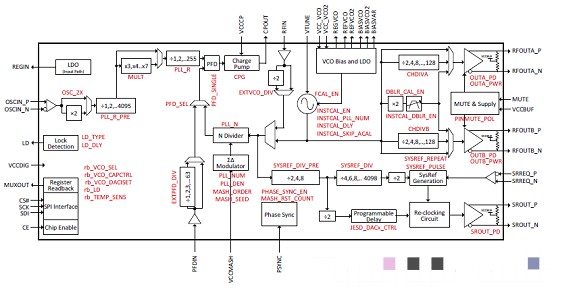

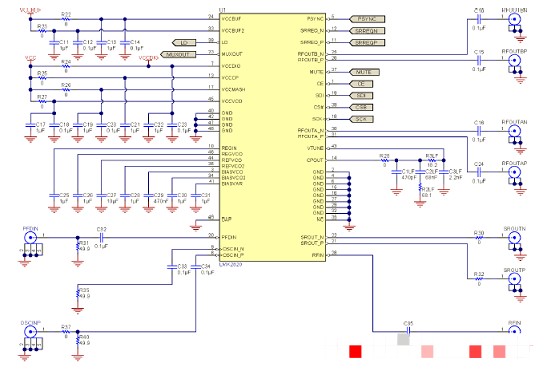

5321 LMX2594是一款高性能宽带合成器,可在不使用内部加倍器的情况下生成 10MHz 至 15GHz 范围内的任何频率,因而无需使用分谐波滤波器。品质因数为 -236dBc/Hz 的高性能 PLL 和高相位检测器频率可实现非常低的带内噪声和集成抖动。

2019-05-10 16:05:59 14029

14029

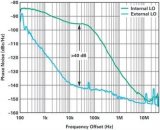

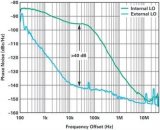

通过分析ADRV9009收发器的测量结果,其噪声性能结果却决于所选架构,不同架构结果差异较大。使用内部LO功能时,相位噪声由IC内部的锁相环(PLL)和压控振荡器(VCO)决定。内部LO

2021-01-04 16:23:37 3607

3607

ADF4196:低相位噪声、快速建立、6 GHz PLL频率合成器数据表

2021-04-23 17:13:01 1

1 ADF4193:低相位噪声、快速建立PLL频率合成器数据表

2021-04-27 21:07:31 3

3 (LO)或高速时钟时,相位噪声性能对满足系统要求起到了重要作用。最初从数据表中推断出该规格时似乎就像一个独立的项目。下面我来讲解一下如何通过读取PLL的相位噪声规格来对您的无线电或高速应用可达到的性能

2021-11-24 15:40:06 2266

2266

每当介绍相位噪声测试方案时,都会提到时间抖动,经常提到二者都是表征信号短期频率稳定度的参数,而且是频域和时域相对应的参数。正如题目所示,相位噪声与时间抖动有着一定的关系,那么相噪是与哪种类型的抖动相对应,彼此之间又有着怎样的数学关系,这些疑问都将在文中找到答案。

2022-04-19 15:27:05 2450

2450 时钟抖动使随机抖动和相位噪声不再神秘

2022-11-07 08:07:29 4

4 在产生高频、高线性度信号源时,低相位噪声至关重要。相位噪声是信号相位不希望的变化或变化的量度。它是在频域中测量的,相当于时域中的抖动。使用PLL频率合成器时,总相位噪声由各种电路模块和组件的汇编

2023-01-09 16:23:38 3613

3613

采用PLL的时钟发生器广泛用于网络设备中,用于生成高精度和低抖动参考时钟或保持同步网络操作。大多数时钟振荡器使用理想、干净的电源给出其抖动或相位噪声规格。然而,在实际的系统环境中,电源可能会因板载开关电源或嘈杂的数字ASIC而受到干扰。为了在系统设计中实现最佳性能,了解这种干扰的影响非常重要。

2023-03-08 15:33:00 896

896

相位噪声与时间抖动貌似毫不相干,但却是形影不离的,都是描述信号频率稳定性的参数,只是切入的角度不同。

2023-04-12 09:19:36 859

859 相噪是与哪种类型的抖动相对应?如何理解相位噪声与时间抖动的关系? 相位噪声与时间抖动是两个在信号处理领域中经常涉及的概念。在讨论相位噪声时,我们常常听到相位噪声和时间抖动的联系。因此,本文将探讨相位

2023-10-20 15:08:11 561

561 本应用笔记详细介绍了具有外部VCO的完整12GHz、超低相位噪声小数N分频锁相环(PLL)的设计。它由高性能小数N分频PLL (MAX2880)、基于运算放大器的有源环路滤波器(MAX9632

2023-10-28 14:45:41 6895

6895 为何测出的相位噪声性能低于ADIsimPLL仿真预期值? 相位锁定环(PLL)是一种重要的电路,可用于在不同领域中应用,如无线通信、数据传输、数字信号处理等。PLL将信号同步到参考时钟的频率和相位

2023-10-30 10:51:13 168

168 相位噪声和抖动是对时钟频谱纯度的两种表述形式,一个是频域一个是时域,从原理上来说,它们是等效的。

2023-10-30 16:02:46 687

687

、电源管理等领域得到广泛应用。PLL可以实现锁定输入信号的相位或频率,同时可以将输出信号的频率分频或倍频实现同步。但是,PLL的性能与相位噪声直接相关,因此通过读取PLL的相位噪声规格可以对其性能进行初步评估。 相位噪声指的是输出信号相位随时间变化的不稳

2023-10-31 10:33:23 217

217 如何评估分布式PLL系统的相位噪声? 要评估分布式PLL系统的相位噪声,我们需要先了解什么是PLL系统和相位噪声。PLL(Phase Locked Loop)是一种电子电路,可以将输入信号的相位锁定

2023-11-06 10:26:29 218

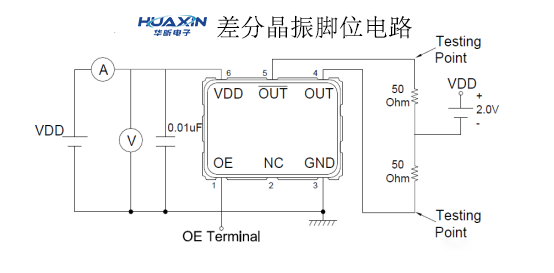

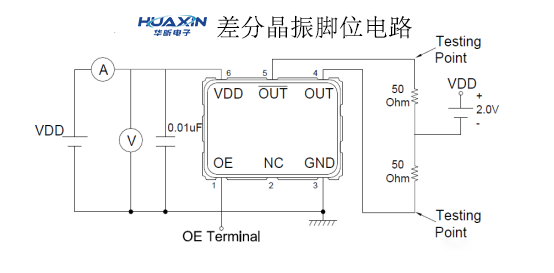

218 华昕 H-YF6 系列差分晶振是一款为满足高性能时钟信号需求而设计的产品。其低相位早上和低抖动使其成为通讯信息、测量和GPS定位等领域的理想选择

2023-11-15 16:41:49 297

297

,包括电路稳定性不良、时钟补偿误差、温度变化、电磁干扰等。相位噪声对信号有着广泛的影响,包括降低信号的频谱纯度、引起功率泄露、产生频率副瓣、导致系统误码率的提高等。 抖动是指信号的周期性变化,通常表现为时间轴上信号

2024-01-29 13:54:34 230

230 。本文将详细介绍相位噪声和时间抖动的定义、关系和测试方法。 首先,我们来了解相位噪声的概念。相位噪声是指信号的相位随时间变化的不稳定性或扰动性。在理想情况下,一个信号的频率应该是恒定的,但由于外部干扰或系统本

2024-01-31 09:29:00 138

138 。LDO的设计和特性直接影响到PLL的性能,尤其是相位噪声。在本文中,我们将深入探讨LDO如何影响PLL的相位噪声。 首先,我们需要了解PLL的基本结构和工作原理。PLL由振荡器、分频器、锁相环过滤器以及参考频率源组成。其工作原理是通过反馈控制机制来将输入信号

2024-01-31 16:43:11 172

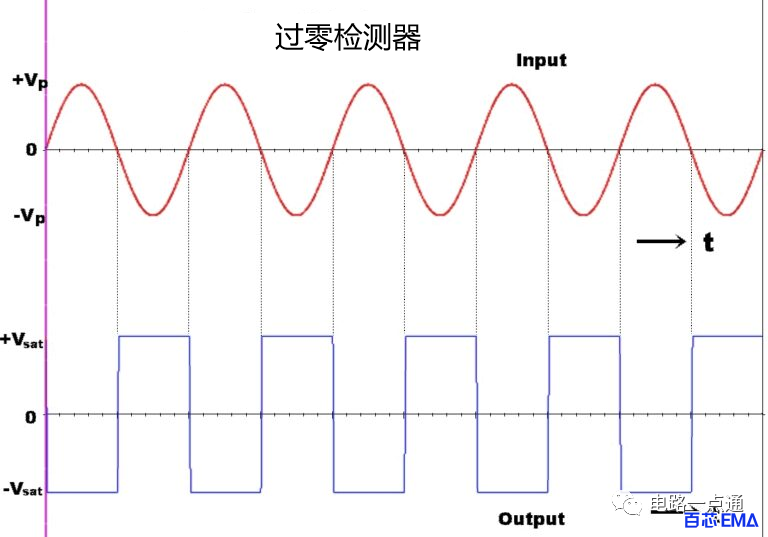

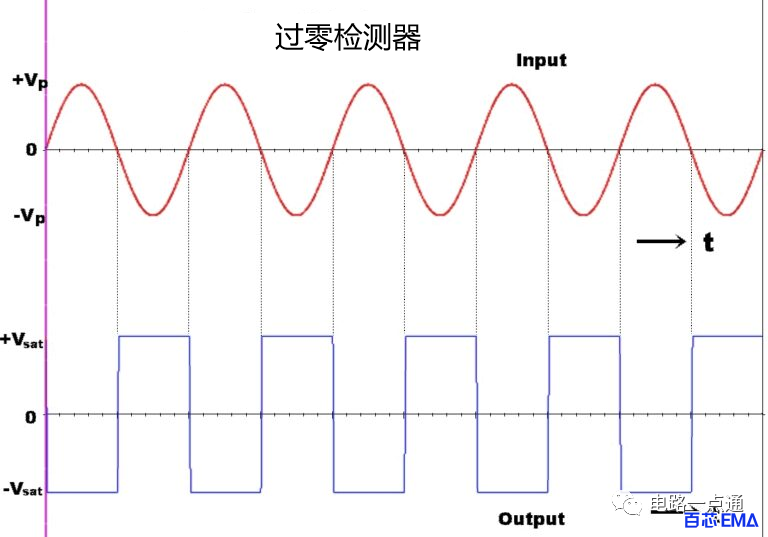

172 过零检测器(Zero Crossing Detector,ZCD)是一种用于检测信号波形过零点的电子设备。在许多应用中,如同步、相位锁定环路(PLL)和频率检测等,过零检测器都发

2024-02-01 14:12:06 295

295

电子发烧友App

电子发烧友App

评论