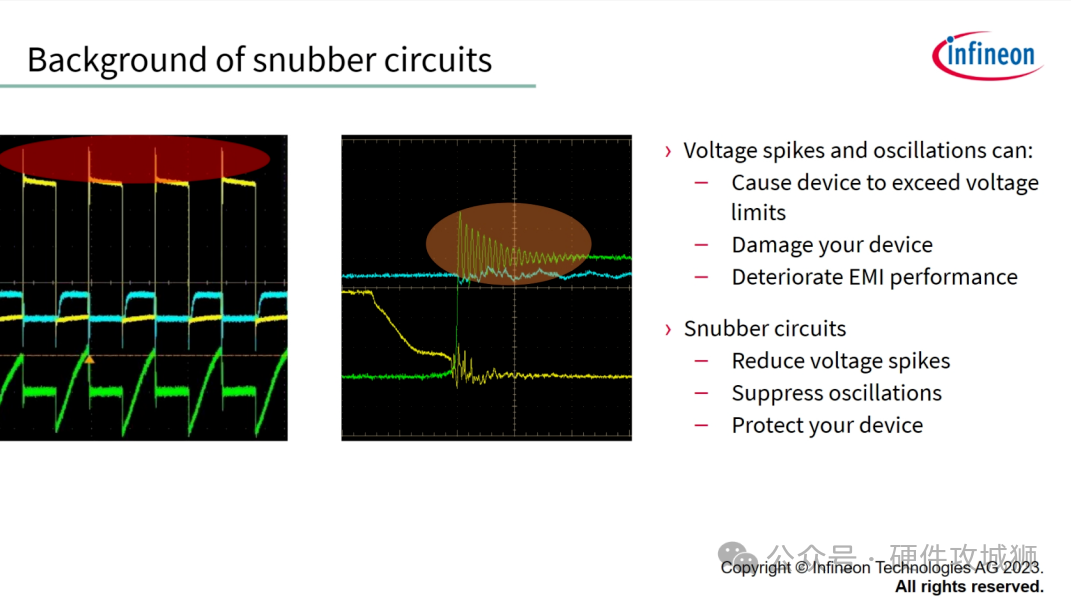

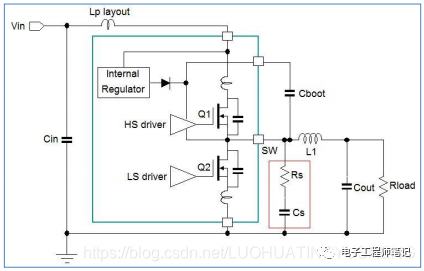

在实际的SMPS测试中,总会看到电压尖峰和振荡波形,电压尖峰和振荡波形有哪些潜在危害呢?电压尖峰会导致器件超出电压限制,进而受损,同时,会导致电路EMI性能下降。

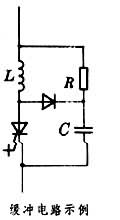

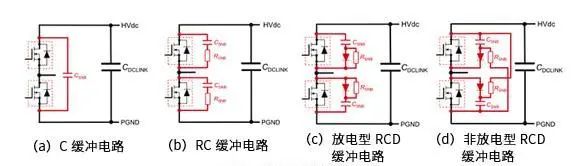

缓冲电路可降低电压尖峰,抑制振荡,保护器件。

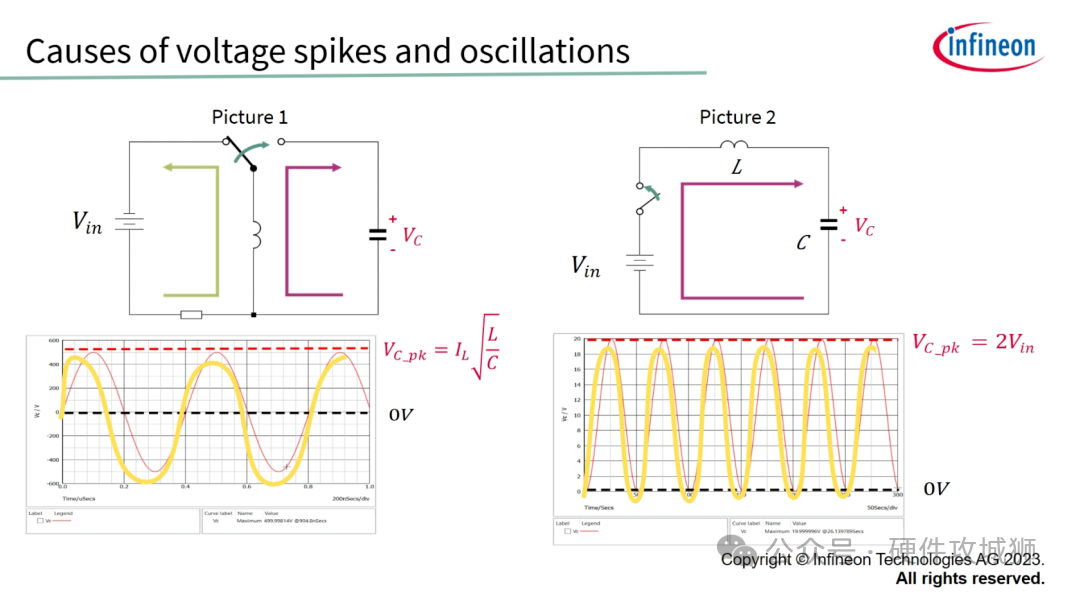

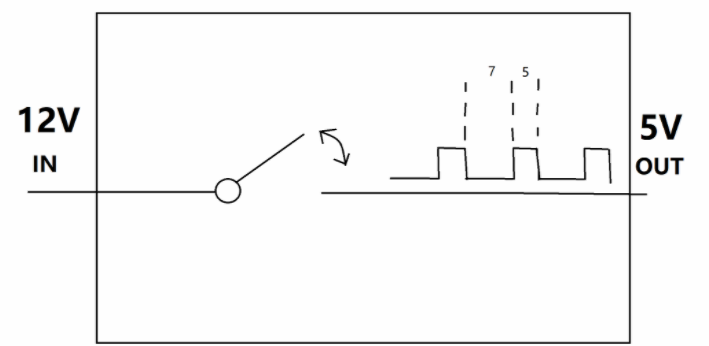

电压尖峰和振荡是怎么来的?感性器件和容性器件共存于一个电路中,事实上,寄生电感和寄生电容是不可避免的,当阻尼系数小于1时,则电路的电阻组件无法有效抑制电感和电容之间的能量交换,当出现激发事件时,就相当于图中所示的开关状态转变。

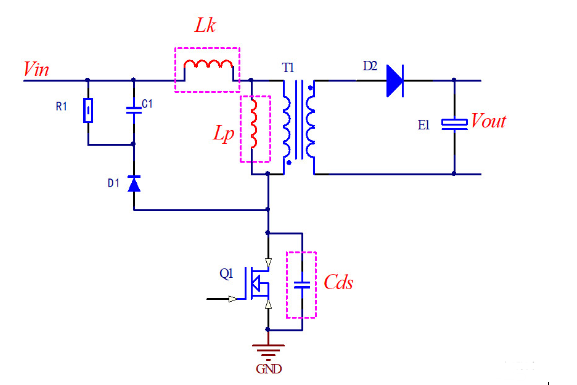

在图1中,当开关状态变化后,电容电压变到这个等级。在图2中,当开关状态变化后,电容电压变到这个等级,当电容器达到第一个峰值电压,就会开始将能量返回电感器和电压源。随后,电能在电感器(电压源)和电容器之间传输,振荡由此而来。

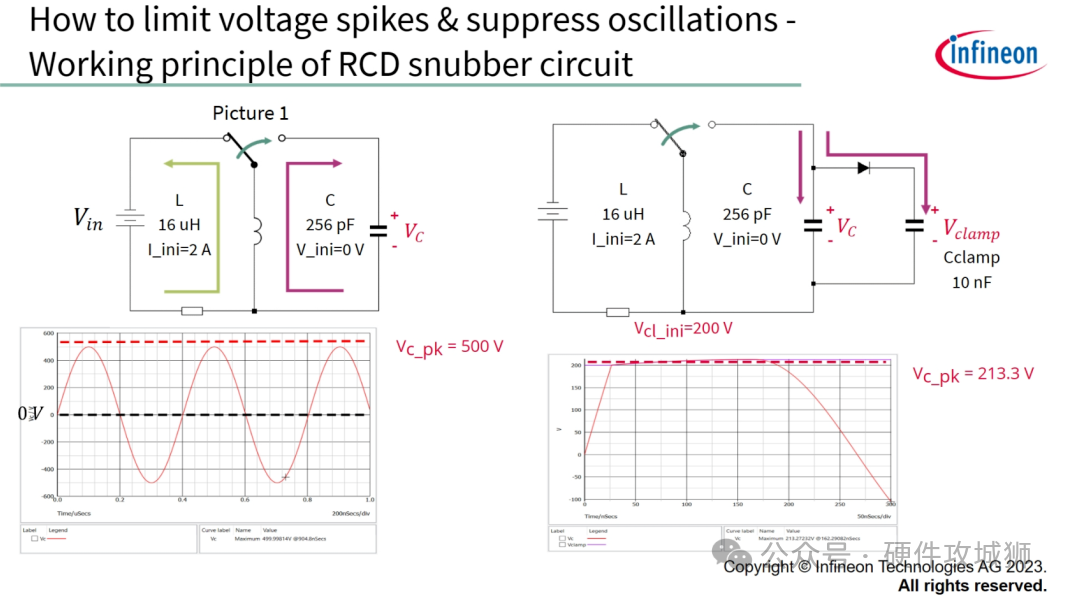

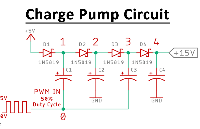

如何限制图1中的峰值电压,抑制振荡呢?通过较大的电容器续流电感器中的电流,可降低电感器峰值电压,例如,用16uH的电感器和2A的初始电流,给256pF的电容器供电,则峰值电压为500V,在右图,增加了一个二极管和较大的10nF电容器,在200V初始电压下,峰值电压可降至213.3V,这就是RCD缓冲电路的工作原理。

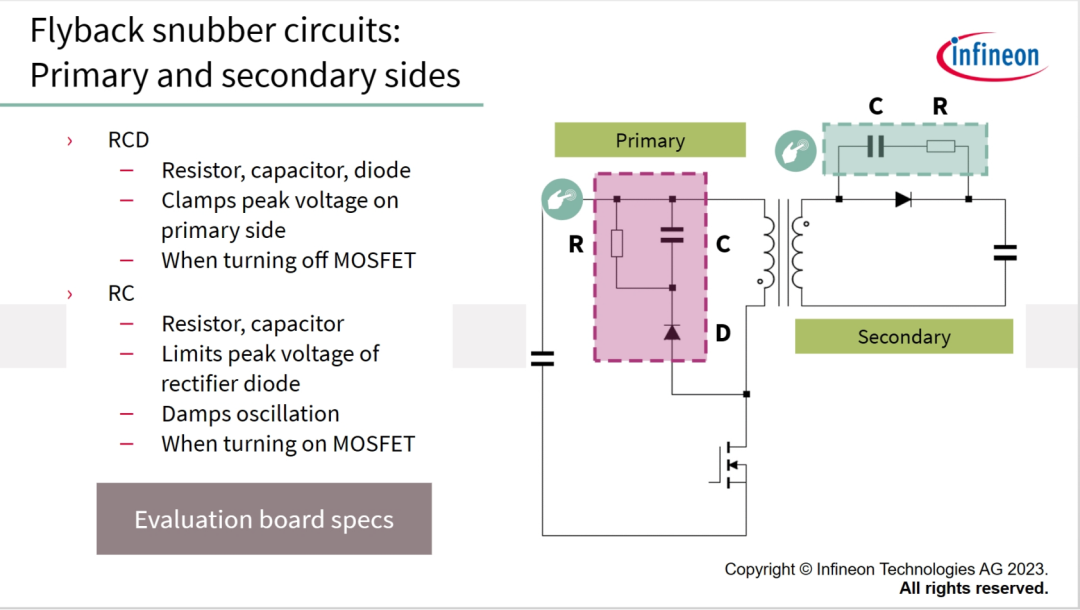

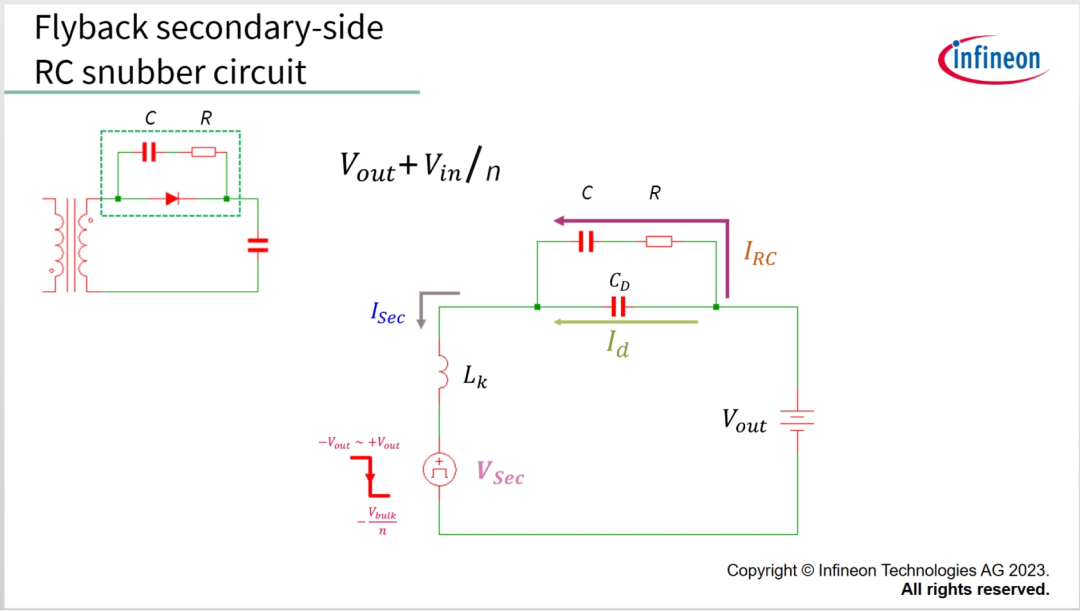

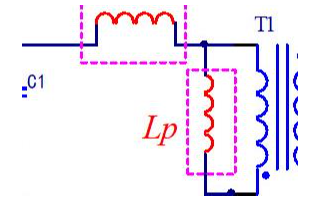

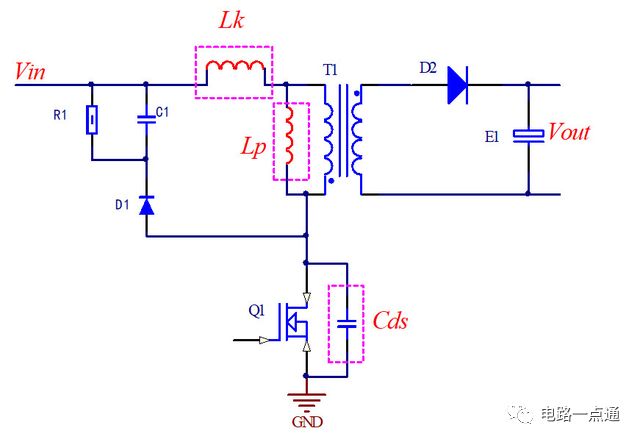

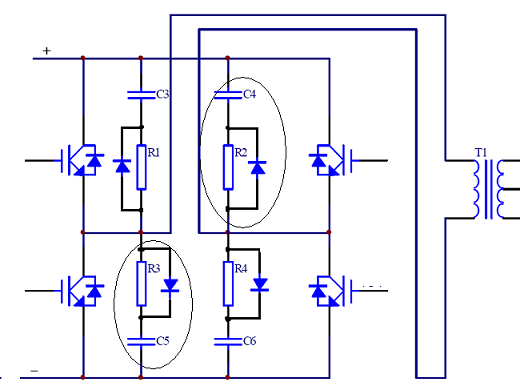

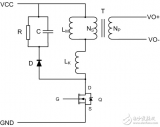

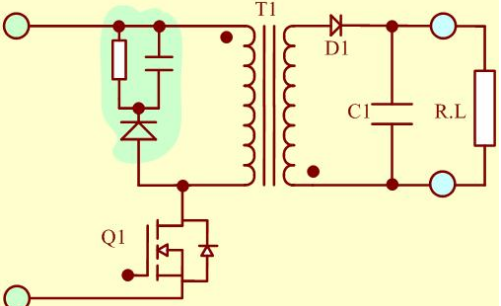

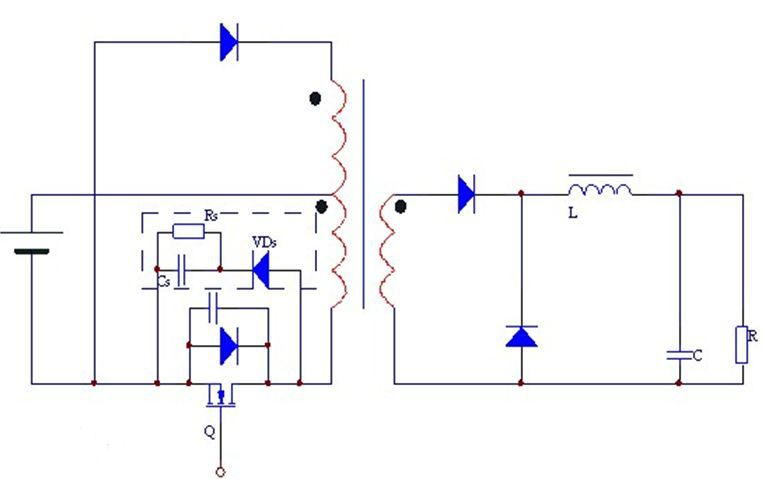

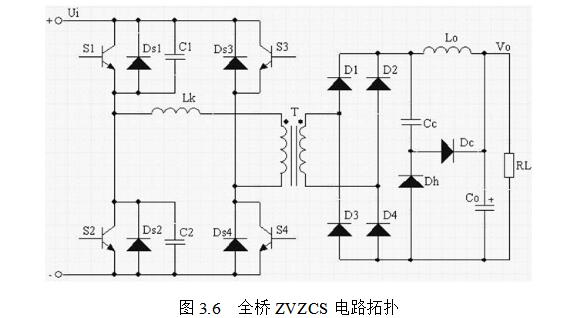

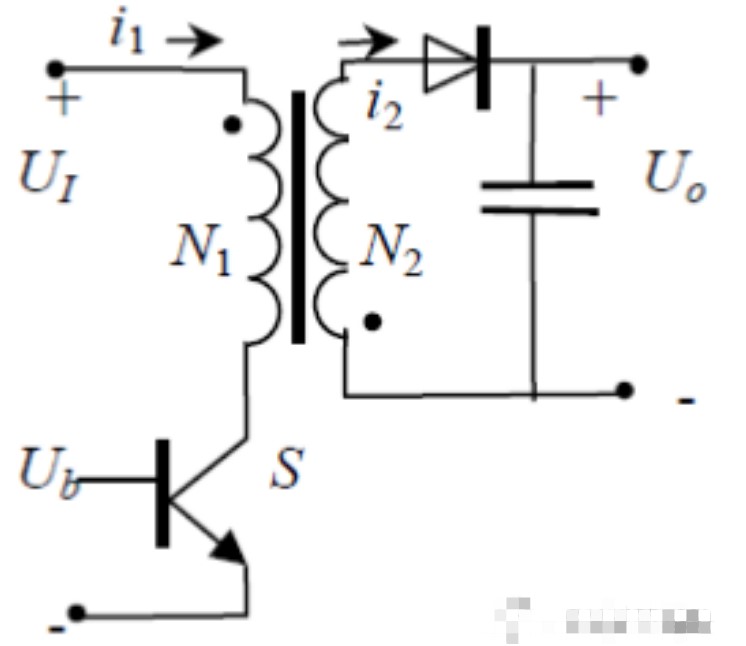

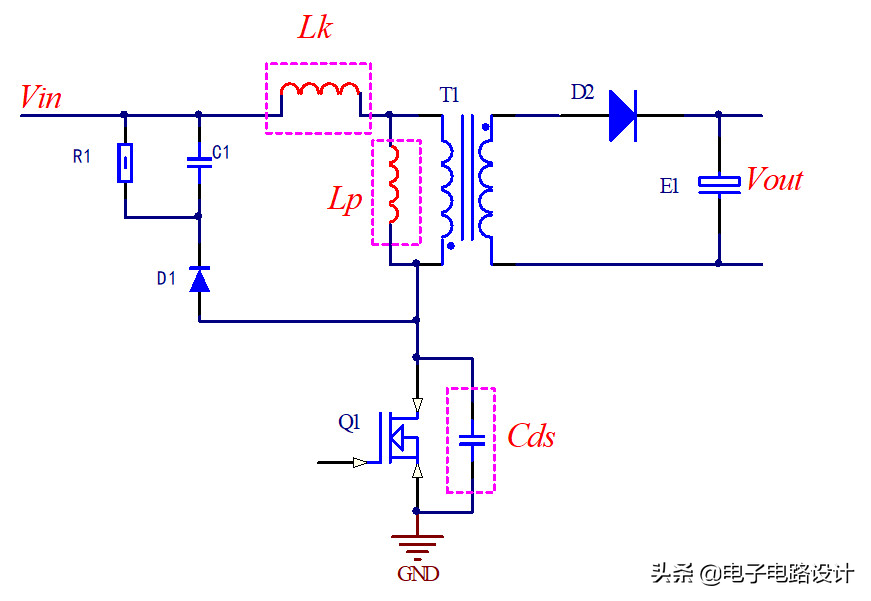

一般,反激开关中有两种缓冲电路,一个是RCD缓冲电路,用于在MOSFET关断时,钳位反激初级侧MOSFET的峰值电压,另一个是RC缓冲电路,用于在MOSFET开通时,限制整流二极管的峰值电压,降低震荡幅度。

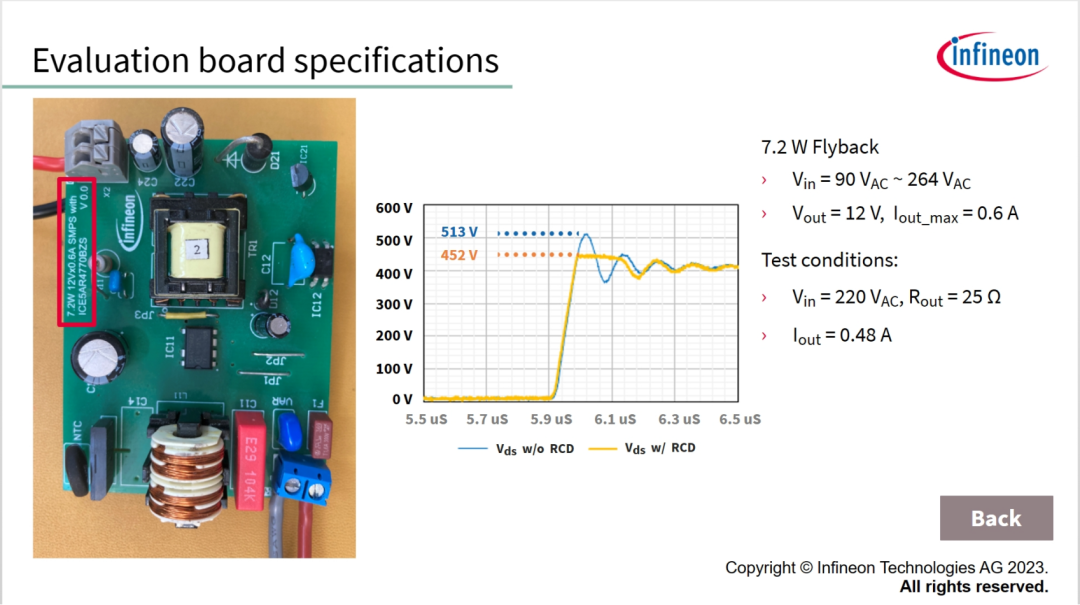

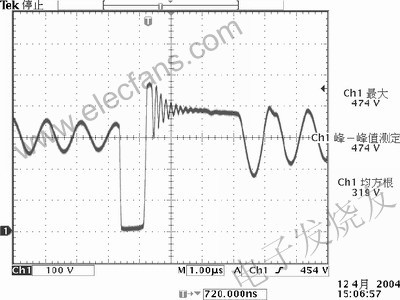

在下面案例中,缓冲电路测试数据基于具有下列参数的评估板。7.2W反激变换器,输入为90~264Vac,输出电压为12V,最大电流为0.6A,测试峰值漏源电压(Vds)波形时,所用输入为220Vac,输出电阻为25R,输出电流为0.48A。采用RCD缓冲电路时,峰值漏源电压为452V,去掉RCD后,Vds为513V,表明RCD电路可将电压尖峰降低61V。

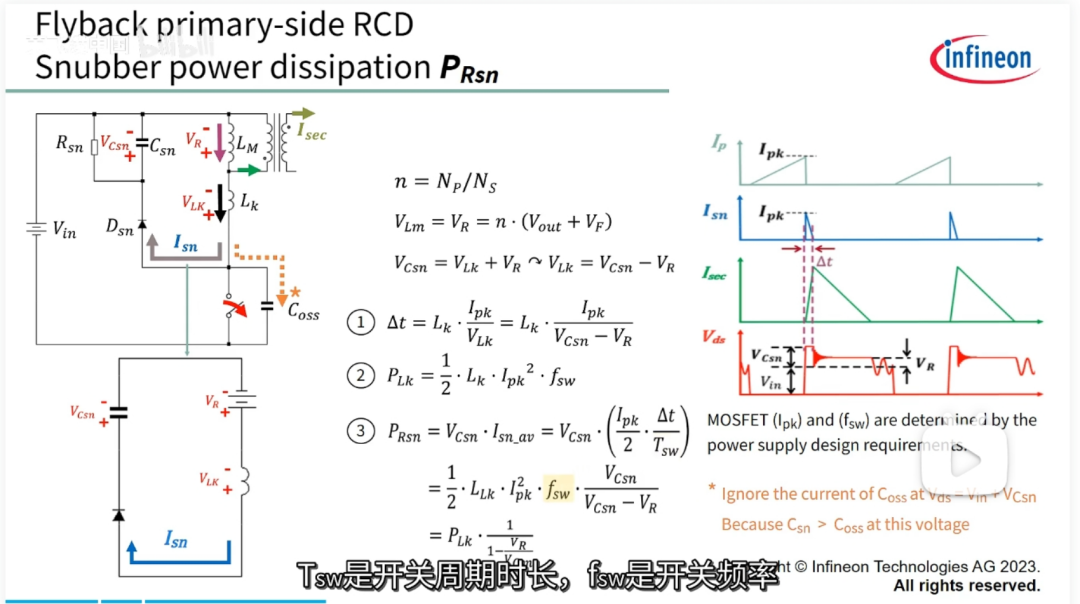

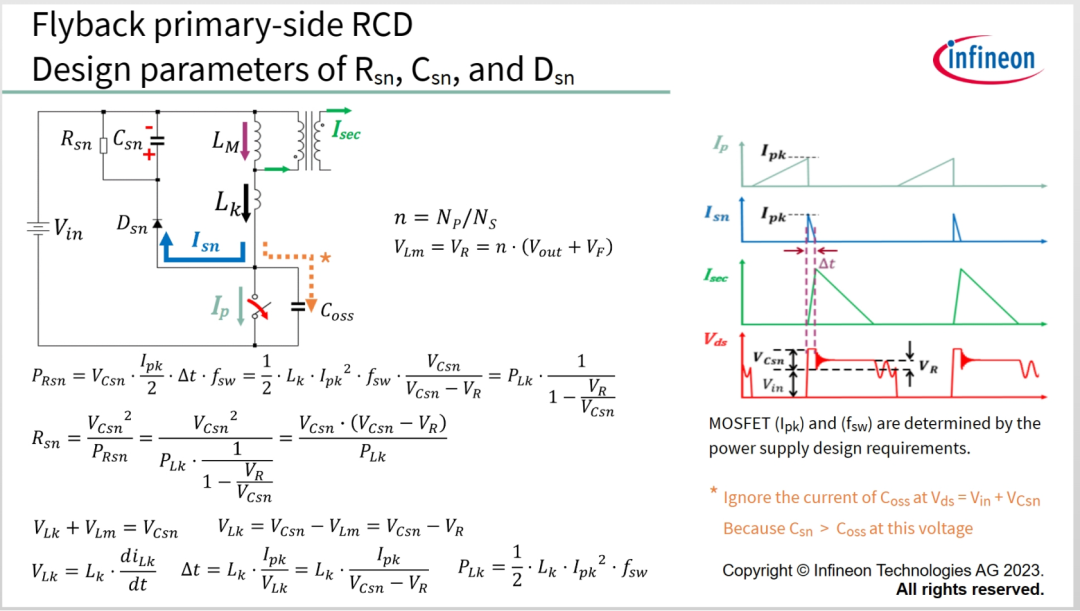

如何确定Rsn,Csn和Dsn的设计参数呢?

RCD缓冲电路实际是将漏感内存储的电能传输到缓冲电容器(Csn),并通过Rsn耗散电能。

MOSFET峰值电流(Ipk)和开关频率根据电源设计要求确定。

设计RCD缓冲电路时,预先设定缓冲电容器电压(Vcsn)和反射电压(VR),VR时次级输出绕组通过变压器匝比的反射电压.

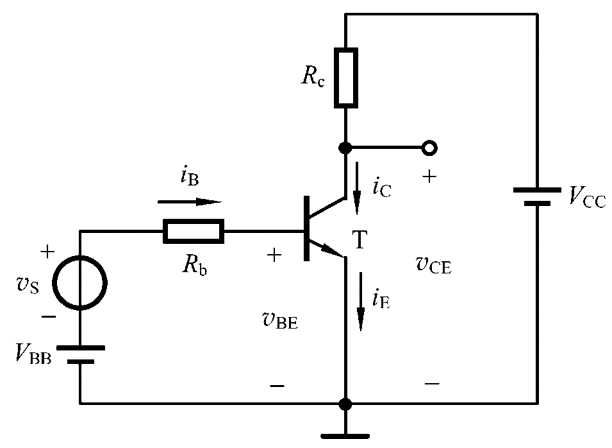

当MOSFET关断时,Lk电流保持初始方向,忽略流向Coss的电流,假设全部电流流向Csn,相当于电感器与电压源串联,为电容器充电,故可从公式1计算出漏感的放电时间。从公式2算出Lk对Csn的充电功率,进入电容器的电能要被电阻Rsn消耗,可用公式3计算。

Tsw是开关周期时长,fsw是开关频率。

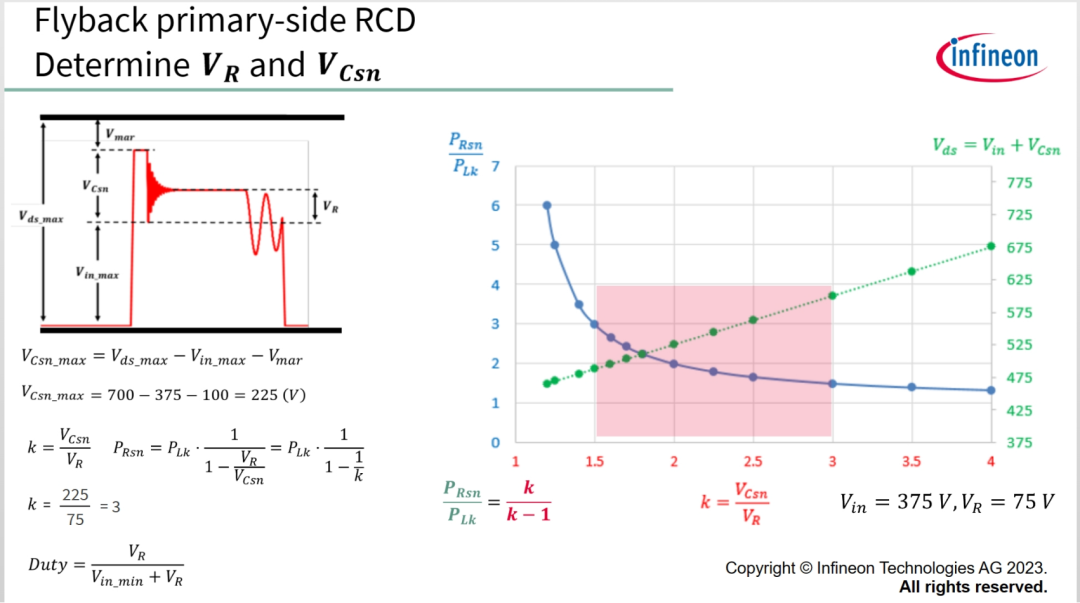

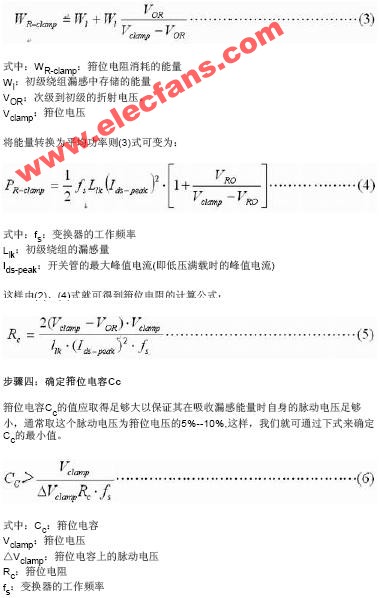

在反激中,临界占空比如下,一般来说,最大占空比在70%左右,对于80~375V的常见DC输入电压范围,反射电压的范围是60~120V,计算Vcsn时,用下面的公式设置K和Prsn.

右图是Psn/Plk与K以及Vds与K的关系。K越大,Rsn的损耗越小,Vds越高,Vcs_max取决于最大输入电压,MOSFET耐压和MOSFET的电压裕量。

例如Vin_max=375V,使用700V MOSFET,Vmar=100V,则VCsn_max为225V,同时考虑VCsn和Prs,一般建议K值比介于1.5~3n,利用k的公式,VCsn为225,Vr=75V,为该设计选择k为3,以达到较高的效率。

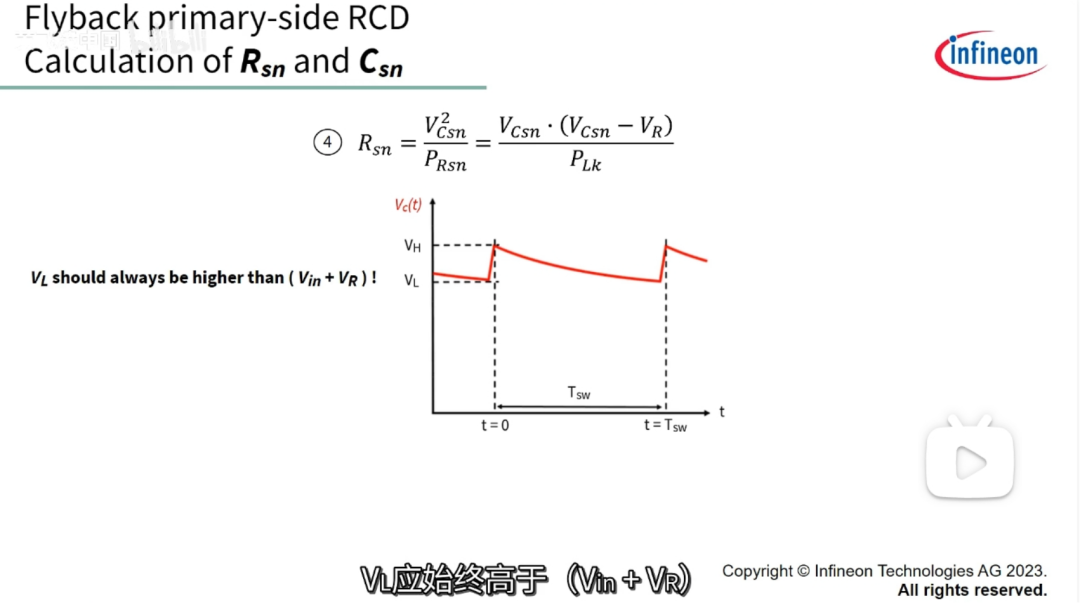

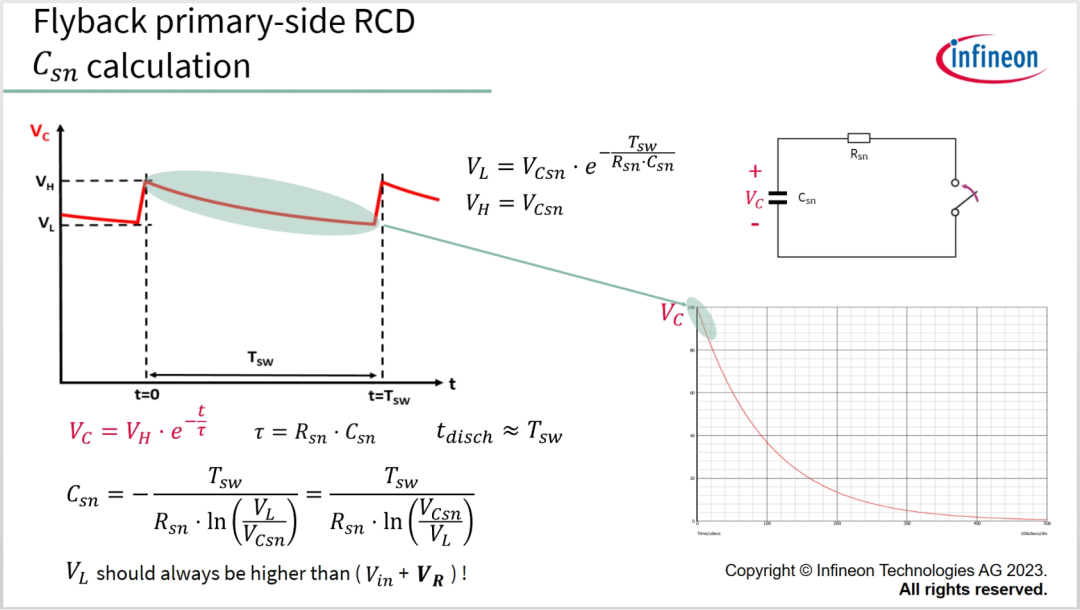

确定VCsn和Vr后,通过公式4计算Rsn的值,选择一个开关周期放电后的最小可接受Csn(Vl)值。VL应始终高于(Vin+Vr),VH为Vcsn的初始值.

放电时间大约等于开关时间(Tsw).Vc上升曲线时整体RC放电曲线的一小部分。这就是Csn曲线计算公式的推导。

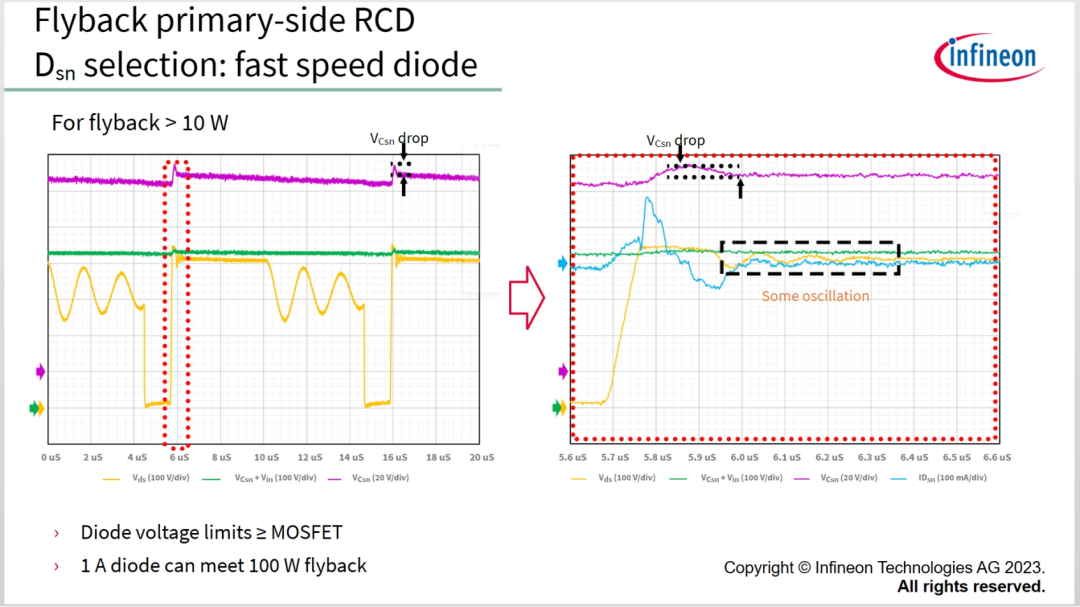

Dsn选用快速二极管,注意二极管的耐压要大于等于MOSFET的耐压,1A的二极管可至少满足100W的反激。因为Dsn的正向导通时间非常短,仅有几百纳秒,左侧高亮区域放大后如右图,Dsn的反向恢复特性对Vds峰值电压和振荡有明显的影响,正如实测波形所示,电感器对Csn充电后,Vcsn出现压降,这源于Dsn的反向恢复,在Dsn恢复时间内,Csn会释放部分电能,这之后Vds小于(Vin+Vcsn),Lk和Coss将会共振一小段时间,正常情况下, Trr为500nS的Dsn可满足数十瓦的反激功率。如果开关频率高,且散热条件差,应当使用超快速二极管,Trr要小于100nS。

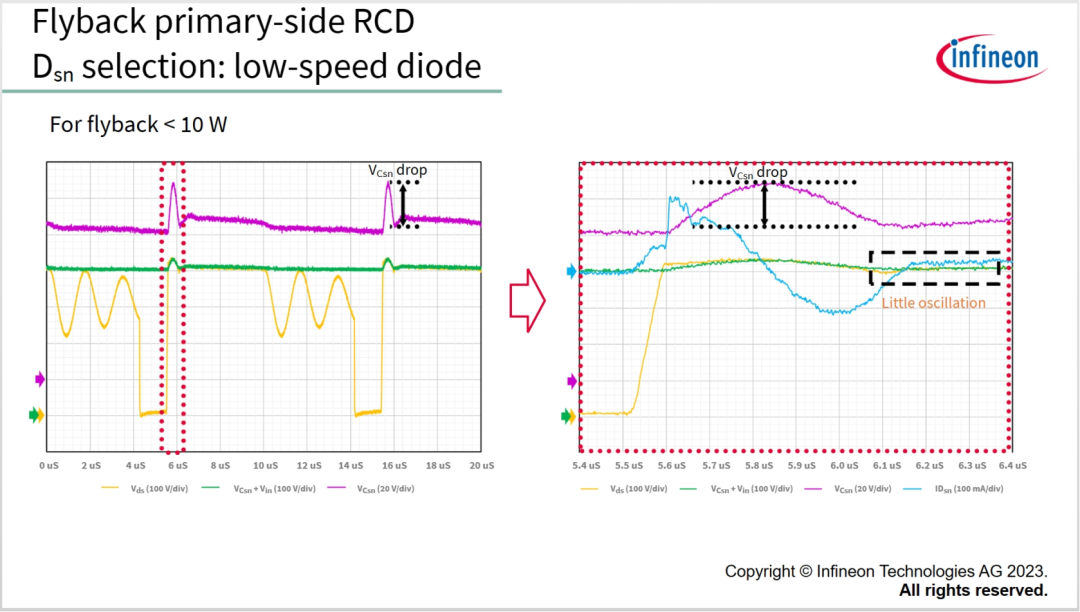

对于Dsn选用慢管,注意左侧高亮区域放大后,如右图。若选用慢管,Trr约为1.5uS,Csn将会传输更多电能至次级侧,因此,Vcsn下降才比快速二极管大了很多。低速二极管的反向电流很软,因而随后的振荡也很小。但慢管只适用于小功率,建议小于10W。因为慢管将承受更多的功耗,Dsn内温度会较高。

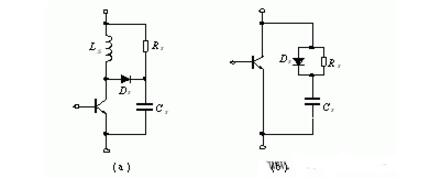

反激次级侧,MOSFET开启时,次级电压Vsec的初始值介于(-Vout)和(+Vout)之间,这里以初始次级i电压Vsec_ini等于+Vout 作为最糟糕情况进行分析。在MOSFET开启器件,C的电压将会达到(Vout+Vin/n),在这一过程中其降幅作用,可降低二极管的电压尖峰,

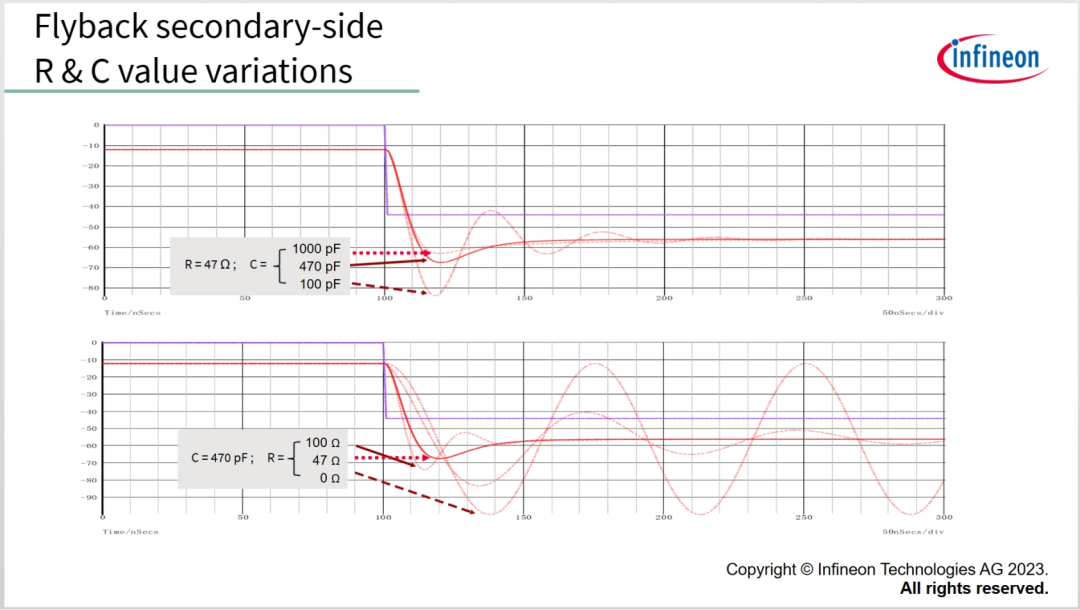

首先先看提高或降低电容和电阻值分别对瞬态有何影响。当R不变,电容越高,电压下冲越小,越平缓地过度至稳定状态,但电容越高,功耗越大。当C保持不变,电阻值最优,可实现最小的下冲电压。高于或低于最优电阻都会提高下冲电压。

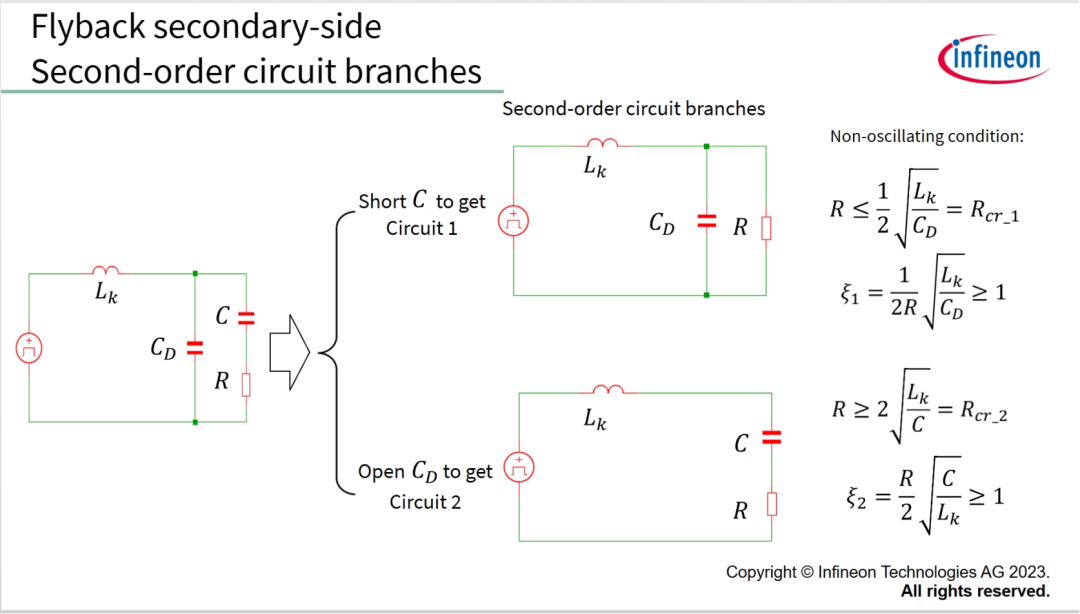

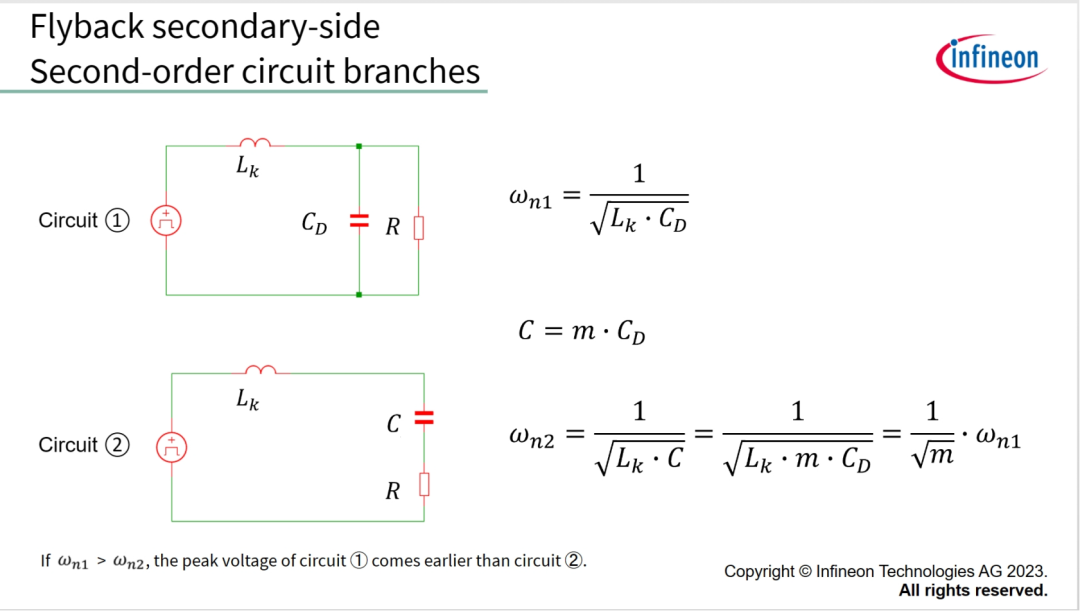

为简化计算,我们把带有RC缓冲的电路分解成2个二阶电路,分别加以分析,将C短路,得到电路1,该电路的无振荡条件如右图。断开Cd,得到电路2,该电路的无振荡条件也如右图。

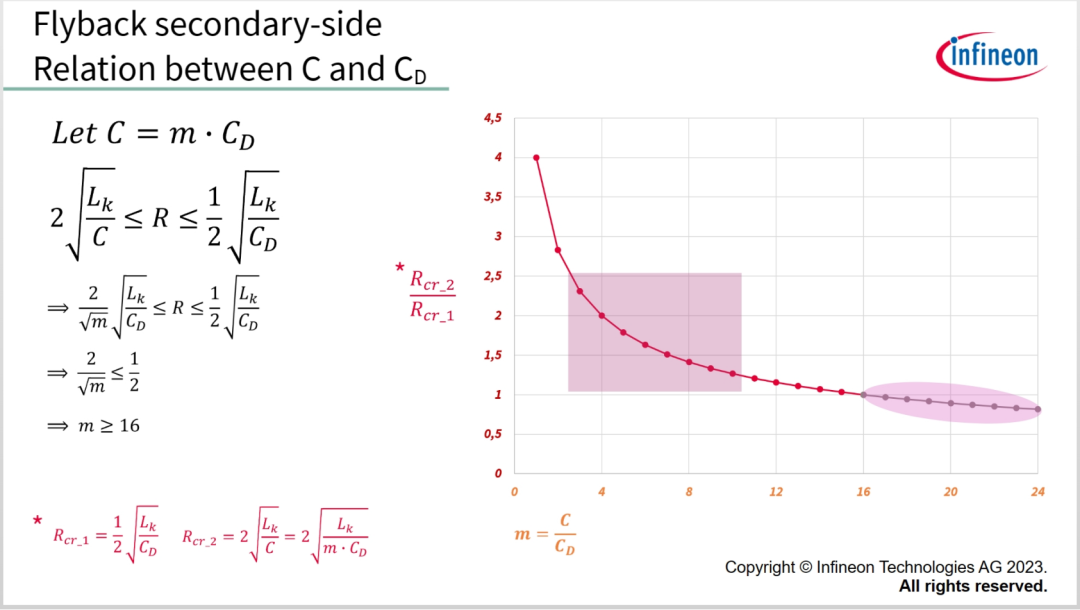

进一步了解C和Cd的关系对2个二阶电路的影响。使C等于m*Cd,若R能满足下面的不等式,则两个电路能同时满足无振荡条件。也可以通过图来表示,横轴为m,纵轴时Rcr_2和Rcr_1的比值。Y轴≤1时,m≥16.2个电路均满足无振荡条件,但在实际应用中,当C是Cd的16倍时,会引起较高损耗。在满足效率的同时,需要全面考虑降低下冲或者振荡的极限。一般来说,m在2.5~10之间时可接受的。

在实际应用中,C=m*Cd,m通常为2.5~10,因此,如果电路1的频率用这一公式计算,则两个电路的固有频率右如下关系。如果Wn1>Wn2,则电路1的峰值电压比电路2来得早。由于功耗,m无法达到16,因此我们需要判断哪个电路是导致峰值电压得主要原因。为此,我们做一个实际的反激案例来确定RC。

通过以下6个步骤确定RC:

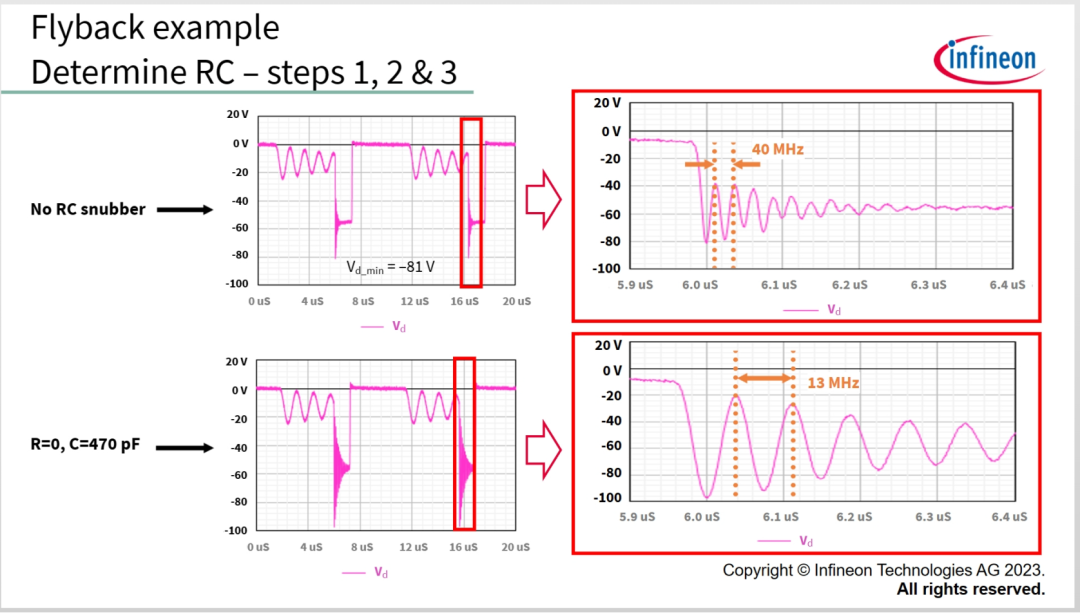

测量MOSFET开启时无RC电路的Vcd振荡频率。如波形所示,该频率为40MHz;

使R=0,选择合适得电容,将频率降低大约一半,如波形所示,选择C=470pF,频率约为13MHz;

计算Cd和Lk的值。Cd=64p,Lk=266nH.(这个因为频率是讲大概的,所以要按实际测试去算,仅参考)

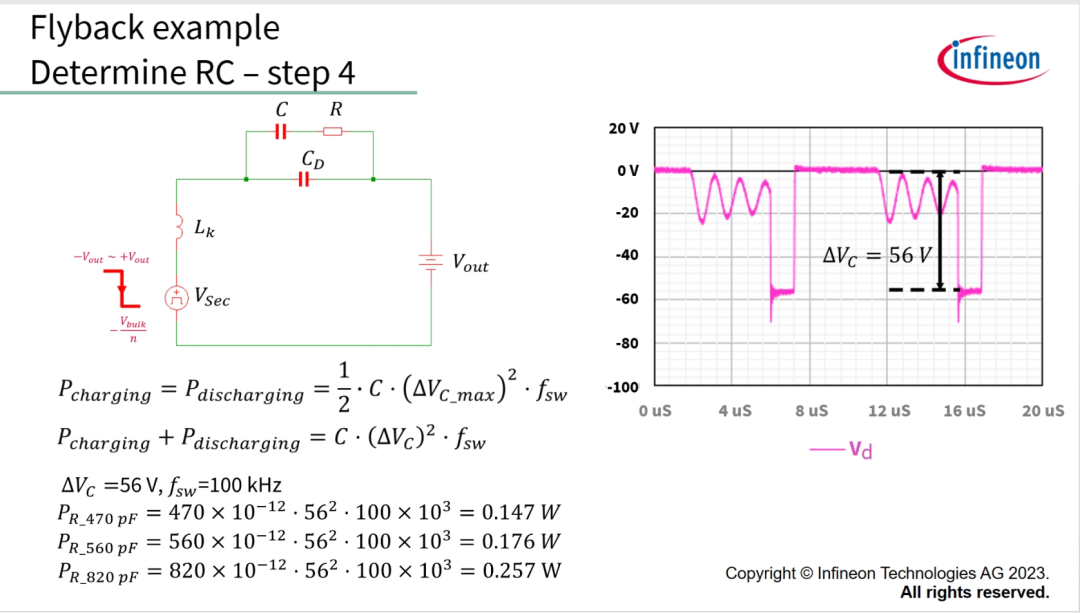

计算R的功率损耗:R的功耗实际由电容C充放电造成电阻上的损耗。这里用这个公式计算出充放电损耗。R的总损耗如下。例如C=470,560,820pF的功率损耗。此外,需要使用额定功率是Pr两倍以上的电阻。

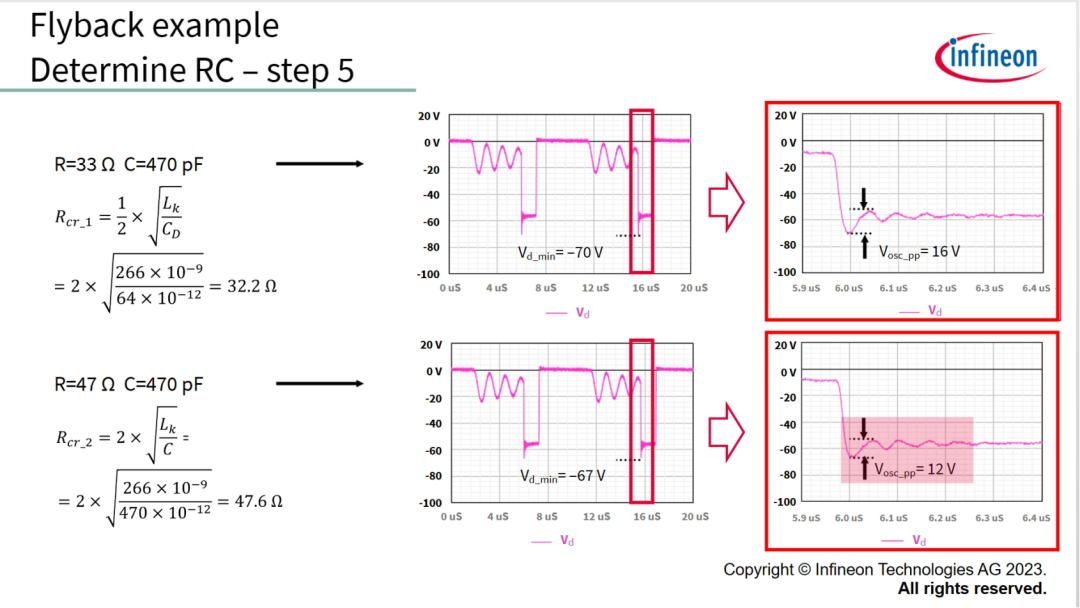

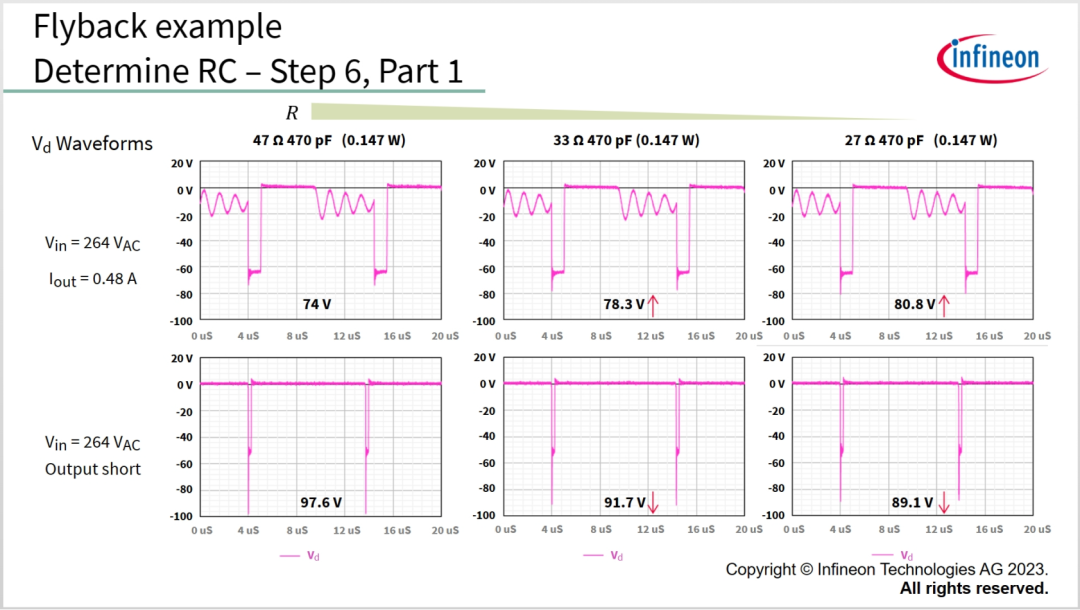

计算临界阻尼Rcr_1和Rcr_2,为计算较低的损耗,使用470pF电容,并用RC=33R,470pF的组合。,以及RC=47R,470pF组合来测试结果。Vin=220V,Iout=0.48A,如右图,电阻对振荡抑制有较好的效果。结果表明,电路2是导致峰值电压的主要原因,但这不代表47R就是最终选择。 还需要考虑其它情况。

当电路进入CCM模式,整流二极管出现反向恢复,使得Lk具有高的初始电流,导致Vd电压尖峰上升。

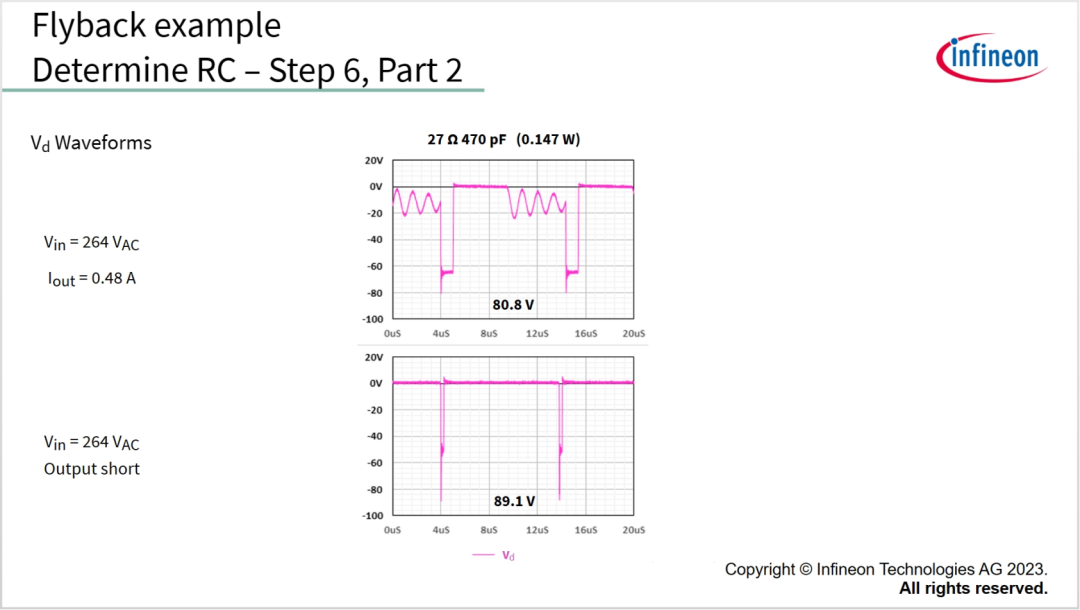

可以看到,C=470pF,和Iout=0.48A保持不变,R下降时,峰值电压上升,使得电路2成为峰值电压的主要原因。然而,最糟糕的情况是当输出短路时,Lk会带着最高的初始电流。这些波形显示同样的电容和下降的R,但输出未短路。当输出短路,R下降时,峰值电压下降。使得电路1成为导致峰值电压的主要原因。因此,加入Rsn很高,会减少进入电路2的电能,可能导致电路1成为导致电压尖峰的主要原因。因此在CCM中,有必要降低Rsn,以减少尖峰电压。

保持R不变,调整C。在正常工作和输出短路的情况下,大电容可降低峰值电压,但会增加功耗,如波形所示,C上升至一定成都后,峰值电压的幅值会下降变缓。

最后,应当基于功耗,峰值电压和EMI性能来选择合适的RC组合。

审核编辑:黄飞

电子发烧友App

电子发烧友App

评论