概 述

在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA的时钟频率高,内部时延小,全部控制逻辑都可由硬件完成,而且速度快,组成形式灵活,并可以集成外围控制、译码和接口电路。更最主要的是,FPGA可以采用IP内核技术,以通过继承、共享或购买所需的知识产权内核提高其开发进度。而利用EDA工具进行设计、综合和验证,则可加速设计过程,降低开发风险,缩短了开发周期,效率高而且更能适应市场。本数据采集系统就是基于FPGA技术设计的多路模拟量、数字量采集与处理系统。FPGA的IO端口多,且可以自由编程、支配、定义其功能,同时配以verilogHDL语言以及芯片自带的可定制模块,即可进行软件设计。FPGA的最大优点是可在线编程。此外,基于FPGA设计的数据采集器还可以方便地进行远程功能扩展,以适应不同应用场合的需要。

1 系统基本构架

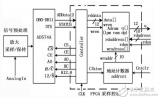

本文所设计的高速数据采集系统是某雷达信号处理系统的一部分,可用于雷达信号的预处理以及采集、缓存。本系统以高速FPGA为核心逻辑控制模块,并与高速ADC和DSP相连接。其系统基本架构如图1所示。

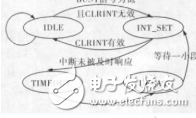

图1中的FPGA可用作数字接收机的预处理模块,该器件集成有PPL倍频、ADC控制接口、FIFO及其管理、SPI接口、DSP总线接口、状态和自检模块等。FPGA的内部结构功能框图如图2所示。

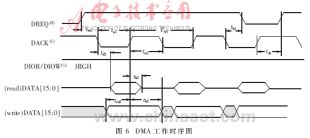

图2中的中断产生模块用于产生周期性中断,利用视频包络和100 MHz时钟可形成50 MHz的DMA同步传送时钟,然后通过外部口DMA方式将采样数据传送到DSP。ADC控制串行接口为通用三线串口,SPI总线接口实际上是一个串并转换器,可用于控制本振。本系统的DSP数据总线为64位宽度,地址为32位。

由于雷达信号接收机中的信号处理量大,信号复杂,因此,通过基于高速大容量FPGA芯片的实时数据采集系统可以很好的满足对信号预处理的需要。

2 芯片的选取

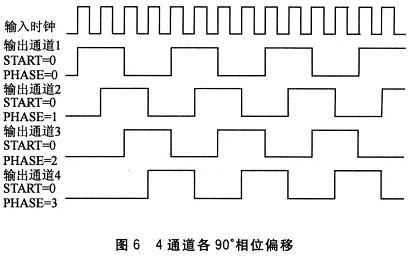

ADC是数据采集系统的核心,其性能指标往往是决定数据采集系统性能最关键的因素。本系统的中频频率为1125 MHz,带宽BW为250 MHz。ADC选用ATMEL公司的高速采样芯片AT84AD001本系统采用带通采样方式,其采样频率低于输人中频频率。但是ADC的输入带宽必须大于中频频率加二分之一带宽,AT84AD001的模拟输入带宽为1500 MHz,高于1125+125=1250 MHz,故可满足设计要求。AT84AD001的最高采样率为1000MHz,也可以满足系统要求。此外,AT84AD001的模拟输入、时钟输入和输出全部采用差分方式。设采样时钟频率fsw为500 MHz,内部提供了1:1/1:2降速率逻辑,其输出A、B、C、D四路的数据速率分别为fsw/2,数据宽度为8位,电平为差分LVDS,数据宽度为2×8=16位,但是,由于速率已经是250MSPS,故可以直接送给FPGA处理,而不需要再进行专门的降速率处理。

StratixII系列FPGA是Altera公司具有全新构架的高密度产品。它采用1.2V电压、90nm及全铜层SRAM工艺,是采用自适应构架的FPGA。与第一代Stratix相比,StratixII器件的逻辑密度是前者的2倍,速度也快了50%,在无线通信、高速数字信号处理和军事雷达等领域都有广泛的应用前景。本设计采用其中的EP2S90系列,该系列由三种不同大小的集成RAM块组成,包括512 bit的M512块、4 Kbit的M4K块以及512 Kbit的M-RAM块)。其中最大容量的M-RAM块就有4块,基于这三种块的RAM单元最多能达到9 Mbits的容量,因此,StratixII系列FPGA是那些对存储量要求很高的应用的理想选择。

3 系统的实现及仿真

ADC接口及控制模块

本系统选用AT84AD001B芯片,设计模拟输入的工作方式为I通道与Q通道有相互独立的两路输入,时钟输入的丁作方式为I通道和O通道有各自独立的时钟,并分别在上升沿时采样。

AT84AD001B有MODE、CLK、LDN及DATA等4个引脚用于三线串口配置。其中,MODE为高时,启用三线串口,设计时可将此引脚接入FPGA中,以便在FPGA中可以根据自身需要进行MODE的置0与置1的配置;CLK为三线串口的配置时钟输入引脚,该引脚允许输入的最大时钟频率是50 MHz,本设计的输入时钟为20 MHz,可以符合要求;LDN为通过三线串口配置寄存器的开始和结束信号的输入引脚;DATA为三线串口的寄存器配置数据输入引脚。

每个三线串口寄存器所需输人的配置数据包括3 bit的寄存器地址和16 bit送人该寄存器的数据,总共需配置8个寄存器,其相关时序图如3所示。

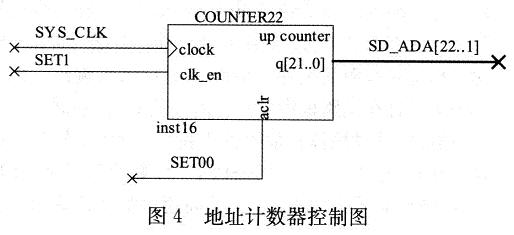

根据以上高速采样相关的三线串口组成情况,可以得到如图4所示的AD配置电路。

图4中各管脚的定义如下:

clk_20m:三线串口时钟输入;

rst:复位;

ad_mode:配置模式;

s_ldn:标志信号脚;

s_data:寄存器数据输人;

其仿真结果如图5所示,由图5可见,在ldn上升沿时寄存器数据开始输入,每20个周期读入一个寄存器数据。由此结果,即可知配置正确。

3.2 大容量FIFO数据缓存模块

由于采集的雷达信号数据量很大,所以,本系统通过Quartus中软件自带的宏功能MegaWizardPlag_in Manager来产生一个64 bit×32768words的大容量FIFO,从而有效地利用了这片FPGA的存储资源。其产生的FIFO模块如图6所示。

图6中,64位数据由ADC的高速数据采样提供,ADC的I、Q两路数据均为16位宽。为了获得更高的速度以及更大的数据缓存量,在数据进入FIFO之前,可对ADC的采样数据进行数据抽取和拼接,以将两组32位宽的IQ数据拼接成64位宽数据,然后一次送入FIFO中进行缓存。FIFO的wrreq写使能信号由前面提到的视频检测脉冲以及DSP的控制信号共同提供,其中写时钟wrclk与ADC数据拼接时钟同步,读时钟rdclk与DSP时钟同步,FIFO数据出口与DSP总线相连接。

系统的其他配置以及外围接口由于不是本文的重点,在此省略不讲。

在Ouartus平台下进行时钟分配、三线串口配置等相关处理,以及信号处理模块综合后,所得到的系统资源使用情况如图7所示。然后再利用VisualDSP++5.0平台读取采样信号数据,并用plot进行绘图,即可得到如图8所示的高速采样结果图。

4 结束语

本文是在参与实际项目的基础上完成的,本系统目前已经应用于某雷达信号处理机中。随着高速器件的开发和利用,数字接收机技术的迅速发展,其信号采集与处理的速度必将更快,处理质量会更好,处理数据量也会更大。

FPGA芯片在高速数据采集缓存系统中的应用

- FPGA(591969)

- 芯片(407703)

- 数据(87427)

相关推荐

5 Gsps高速数据采集系统该怎么设计?

高速实时频谱仪是对实时采集的数据进行频谱分析,要达到这样的目的,对数据采集系统的采样精度、采样率和存储量等指标提出了更高的要求。而在高速数据采集系统中,ADC在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响。

2019-09-02 06:44:39

FPGA芯片在高速数据采集缓存系统中有哪些应用?

在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA的时钟频率高,内部时延小,全部控制逻辑都可由硬件完成,而且速度快,组成形式灵活,并可以集成外围控制、译码和接口电路。更最主要

2019-11-01 07:40:10

FPGA实现数据采集的方式对比(传统串口、数据采集卡及外设计接口)

的EZ-USB FX2系列智能USB接口芯片。其作用是将主机所发送的命令序列经USB2.0端口输出,实现对数据采集系统的控制;同时把A/D转换器采集的数据以高速的数据序列形式发送到主机。其中,USB2.0端口

2020-01-07 07:00:00

数据采集询问

高速数据采集后通过网络传送给电脑。这里有个问题,FPGA高速采集了AD数据后,如何传送给电脑这里。现在方案是STM32+FPGA挂SDRAM, 这个方案可行吗?难点是FPGA高速采集的数据存储再了SDRAM中,STM32怎样拿到数据然后通过网络送回电脑。详细想了解方法。

2017-06-15 13:45:53

高速18位数据采集系统DAS参考设计

: MXIM)推出高速、18位数据采集系统(DAS)参考设计MAXREFDES74#,帮助FPGA工程师加快基于FPGA控制系统的评估和验证,以及产品的上市进程。

2019-07-02 06:12:11

高速数据采集系统的硬件结构,CPLD在高速数据采集系统中的应用

高速数据采集系统的硬件结构MAX7000系列CPLD及其开发平台介绍CPLD在高速数据采集系统中的应用

2021-04-08 06:11:56

高速数据采集卡QT1125在飞行质谱中的应用

高速数据采集卡采样256次,使得到谱图时间缩短到0.1秒左右。系统整体介绍工作流程高速脉冲信号进入高速数据采集卡,完成信号的数模转换,按特定顺序缓存到板载内存中,下次脉冲来时,FPGA将新的采集数据

2016-03-02 16:06:15

高速缓存/海量缓存的设计实现

子系统的性能要求和设计方案的基础上,提出了高速缓存和海量缓存方案,并将该方案成功地应用于DSP多通道超声信号采集与处理系统中。 对高速多通道采样数据存储的性能要求:一是高速性,现在高速数据采集

2020-12-04 15:59:14

【数据采集分享】基于LABVIEW的USB接口高速数据采集的设计

基于PCI总线的数据采集系统的进一步开发和应用,因此迫切需要设计一种更为简便通用的高速数据采集通信系统来完成数据采集以及与计算机的数据交互。 近年来通用串行总线(USB)以即插即用等技术优势得到了广泛

2014-12-16 11:32:57

【Aworks申请】高速数据采集系统

申请理由:本开发板为ARM系类,能移植Linux系统,可以实现快速高效的系统,并且能实现数据云共享。对于高速数据采集系统,开发板的资源可以适用,并且非常实用。项目描述:高速数据采集系统原理:通过高速

2015-07-17 14:43:58

【TL6748 DSP申请】雷达信号高速数据采集和处理

申请理由:借助此平台完成数据的处理项目描述:高速ADC+高密度FPGA+高性能DSP,其中FPGA主要负责高速数据缓存,并对整个高速数据采集系统进行控制;DSP器件拥有很强的数字信号处理能力和良好

2015-11-06 10:01:48

【锆石A4 FPGA申请】基于FPGA的多路实时运动数据采集器

申请理由:项目描述:项目名称:基于FPGA的多路实时运动数据采集器项目描述:结合ARM内核单片机的易操作性与FPGA的高速、并行运算的特点,设计一款快速、多路、实时运动数据采集器。一共包含14路信号

2016-08-15 17:13:19

一种基于FPGA和DSP的高速数据采集设计方案介绍

对数据采集与处理系统提出了新的更高的要求,即高速度、高精度和高实时性。对数据采集与处理系统的设计,有以下3种方案可供选择:(1)A/D+DSP方案在传统的高速信号处理中,大多采用这种方案。将A/D、D

2019-07-05 06:41:27

基于FPGA+AD7609的数据采集系统实现

。为了实现高速、连续采样的数据采集系统,本文介绍了一种基于 FPGA +AD7609的数据采集系统的构成及技术实现。采用 FPGA 作为主模块,AD7609为数据采集模块,并设计了硬件实现电路。实验测试

2018-08-09 14:28:00

基于FPGA与SRAM数据采集系统设计

基于FPGA与SRAM数据采集系统设计中文期刊文章作 者:江丽 肖思其作者机构:[1]湖南高速铁路职业技术学院,湖南衡阳421002出 版 物:《科技资讯》 (科技资讯)年 卷 期:2017年 第

2018-05-09 12:09:43

基于FPGA和EPP的图像传感器高速数据采集

。因此,为了采集数据量大的图像数据,本文采用了具有较高传输速率的增强型并行口协议(EPP)和FPGA,实现对OV7620CMOS图像传感器进行高速数据采集,它最高速率可以达到2Mb/s。

2020-04-30 07:47:07

基于FPGA的数据采集系统

基于FPGA的数据采集系统IEE ... 介绍了数据采集系统中以FPGA为处理核心、采用TI公司接口芯片的IEEE1394接口设计,给出了系统硬件设计和FPGA逻辑设计,讨论了IEEE1394总线

2012-08-11 15:43:47

基于FPGA的数据采集存储系统

设计高温环境下(最高120°)基于FPGA的数据采集存储系统,就是通过传感器采集数据,通过FPGA来控制,把数据存储到存储芯片上,回头可以通过接口读取数据显示在计算机上,求大师给我指导,我急需整个系统的protel原理图,请各位帮忙,我将感激不尽。最好有附件画出整个原理图,谢谢!

2012-10-29 21:37:12

基于FPGA的高速数据采集系统接口设计

的出现使FPGA的功能更加强大,但随之而来的是要求提高数据的传输速率,过去人们总是关心如何提高处理器运行速度,而现在关心的是怎样才能更快地将数据从一个芯片传输到另一个芯片。可见,高速数据采集系统

2018-12-18 10:22:18

基于FPGA的高速数据采集系统该怎么设计?

目前,在数据采集系统的硬件设计方案中,有采用通用单片机和USB相结合的方案,也有采用DSP和USB相结合的方案,前者虽然硬件成本低,但是时钟频率较低,难以满足数据采集系统对速度要求;后者虽然可以实现

2019-09-05 07:22:57

基于ARM+FPGA的高速同步数据采集

的网络数据传输。3、 系统结构高速同步数据采集系统主要包括以下几个部分:ARM控制器、存储电路、FPGA逻辑控制电路、A/D转换电路、FIFO缓存、电源电路、接口电路等。系统具备多通道数据采集接口

2010-08-31 09:14:55

基于USB数据采集系统的研究与设计--ResearchandDesignofDataAequisitio

传统总线不足之处,在此基础上研究了基于USB的数据采集系统,根据系统应该达到的技术指标,从而确定系统的整体框架和各个部分芯片的选择。整个系统包括硬件设计和软件设计两部分,实现数据高速转换和采集、数据

2009-06-10 00:57:49

基于USB总线的高速数据采集系统

基于PCI总线的数据采集系统的进一步开发和应用,因此迫切需要设计一种更为简便通用的高速数据采集通信系统来完成数据采集以及与计算机的数据交互。 近年来通用串行总线(USB)以即插即用等技术优势得到了广泛

2019-05-07 09:40:04

基于USB总线的高速数据采集系统

的核心,它包括A/D转换器、微控制器、USB通信接口等。在高速数据采集系统中?由于现场输入信号是高频模拟信号,因而信号的变化范围都比较大?如果采用单一的增益放大?那么放大以后的信号幅值有可能超过A/D

2009-04-11 17:20:15

如何利用FPGA实现高速连续数据采集系统设计?

高速连续数据采集系统的背景及功能是什么?如何利用FPGA实现高速连续数据采集系统设计?FPGA在高速连续数据采集系统中的应用有哪些?

2021-04-08 06:19:37

如何利用ARM和FPGA设计一种高速图像数据采集传输系统?

本文结合实际系统中的前端图像处理和图像数据传输的需要,充分利用ARM的灵活性和FPGA的并行性的特点,设计了一种基于ARM+FPGA的高速图像数据采集传输系统。

2021-06-02 06:18:50

如何设计多路数据采集系统中FIFo?

首先介绍了多路数据采集系统的总体设计、FIFO芯片IDT7202。然后分别分析了FIFO与CPLD、AD接口的设计方法。由16位模数转换芯片AD976完成模拟量至位数字量的转换,由ATERA公司

2020-12-31 07:52:43

实现高速数据采集有哪些方法?

数据采集在现代工业生产及科学研究中的重要地位日益突出,对实时高速数据采集的要求也不断提高。在信号测量、图像处理、音频信号处理等一些高速、高精度的测量中,都要求进行高速、高精度的数据采集。这就对数据采集

2019-07-31 07:25:28

嵌入式高速大缓存AD采集板卡怎么样?

高速多通道实时数据采集系统的方案在工业监控、环境监测等方面的应用非常广泛。随着科学技术的发展,数据采集技术正向着高精度、高速度、稳定可靠、集成化及实时系统的方向发展。并且通过搭载了最新的FPGA,使得产品的升级换代变得更加容易和便捷。

2019-10-23 08:12:56

工业应用>高速数据采集和生成

- 安装在高速 ADC(包括高速运算放大器、FIFO 和 SRAM)的周围。ADC 的数据输出流被写入 FIFO,存储在 SRAM 块中,并在 FPGA 的数据采集逻辑的控制下通过寄存器直接发送至外界

2012-12-12 11:48:15

怎么利用异步FIFO和PLL结构来实现高速缓存?

结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢ FPGA实现的异步FIFO和锁相环(PLL)结构来实现高速缓存,该结构可成倍提高数据流通速率,增加数据采集系统的实时性。采用FPGA设计高速缓存,能针对外部硬件系统的改变,通过修改片内程序以应用于不同的硬件环境。

2021-04-30 06:19:52

怎么实现一种基于FPGA高速数据采集系统中的输入输出接口?

本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。

2021-04-29 06:04:42

采用PCI总线流水式高速数据采集系统设计

采用PCI总线流水式高速数据采集系统设计摘要:目前基于PCI总线的高速数据采集系统,大多采用高速A/D,CPLD或FPGA,FIFO或双端口RAM以及通用PCI接口来设计,其通用性、灵活性差,不能

2009-10-30 15:09:49

高速数据采集系统中高速缓存与海量缓存的实现

探讨了高速数据采集系统中高速采样缓存的重要性和实现途径,阐述了基于ADSP-21065L的并行多通道数据采集板上高速采样缓存的设计与电路结构,给出了采用FPGA实现通道复用和采样数据

2009-04-23 17:08:09 23

23

23

23高速数据采集系统的设计

本文对高速数据采集系统的设计进行了讨论,介绍利用高速线性放大器、高速A/D 转换芯片、ISP 器件制作的DMA 接口,设计以单片机为核心的高速数据采集系统的方法。关键词: I

2009-07-15 11:16:00 22

22

22

22基于FPGA的高速连续数据采集系统的设计

本文提出了一种用于雷达回波信号采集的高速数据采集系统。该系统实现了对数十兆赫的回波信号进行连续的采样和存储。系统通过FPGA控制数据连续采集、缓冲,通过PCI9056将缓冲区

2009-08-15 11:45:53 23

23

23

23基于SignaltapII的高速数据采集系统

提出了使用FPGA控制DDR SDRAM的读写和Signaltap II的触发条件,实现了高速数据采集。通过FPGA和DDR SDRAM完成高速数据采集之后,利用在线逻辑分析仪Signaltap II将采集到的数据借助JTAG口

2009-09-15 16:25:26 31

31

31

31基于PC的多通道自带缓存数据采集系统的设计与实现

基于PC的多通道自带缓存数据采集系统的设计与实现:本文描述了一自带缓存的数据采集系统, 并将本系统所采用的技术与通用的数据采集系统作了比较, 最后提出了本系统作进一步

2009-10-11 11:12:45 12

12

12

12高速数据压缩与缓存的FPGA实现

本文设计了一种以 FPGA 为数据压缩和数据缓存单元的高速数据采集系统,其主要特点是对高速采集的数据进行实时压缩,再将压缩后的数据进行缓冲存储。该设计利用数据比较模

2009-11-30 15:32:36 20

20

20

20基于FPGA的高速多路数据采集系统的设计

本文介绍了一种基于FPGA 的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA 的实现方法。在硬件上FPGA 采用ACEX1K100 器件,用于实现A/D 转换器的控制电路、多路

2009-12-19 16:02:33 50

50

50

50基于FPGA的超高速数据采集与处理系统

介绍了一种基于FPGA 的超高速数据采集与处理系统,给出了系统实现的方案,并详细阐述了各硬件电路的具体构成。对系统软件功能做了简要介绍,并利用嵌入式逻辑分析仪对该超高

2010-01-20 16:03:27 58

58

58

58基于VirtexⅡ-PRO高速数据采集系统设计

在以XilinxⅡ- PRO 和MAX104A 为主要部件的高速数据采集系统中,提高系统处理速度的关键是芯片和芯片之间数据高速传输。文章重点介绍了LVDS 和LVPECL 接口匹配设计和高速串行RocketIO

2010-09-22 08:36:07 11

11

11

11采用FPGA的高速数据采集系统

采用FPGA的高速数据采集系统

随着科学技术的发展,数据采集技术进入到越来越多的领域。目前,已广泛应用于通信,图像处理,军事应用,消费电子,智能控制等方面

2009-04-20 11:03:13 2118

2118

2118

2118

基于USB2.0与FPGA技术的高速数据采集系统的设计

基于USB2.0与FPGA技术的高速数据采集系统的设计

基于USB2.0与FPGA技术的高速数据采集系统的设计

近年来笔记本电脑迅速普及和更新,其中大部分已经

2009-04-22 19:56:15 1347

1347

1347

1347

基于CPLD/FPGA高速数据采集系统的设计

基于CPLD/FPGA高速数据采集系统的设计

0 引 言 传统的数据采集系统一般采用单片机,系统大多通过PCI总线完成数据的传输。其缺点是数学运算能力差;

2010-01-27 09:35:01 508

508

508

508

时钟分配芯片在高速并行数据采集中的应用

时钟分配芯片在高速并行数据采集中的应用

1 经典采样理论

模拟世界与数字世界相互转换的理论基础是抽样定理。抽样定理告诉我们,

2010-02-05 09:47:36 1352

1352

1352

1352

FPGA在膜式氧合器测试数据采集系统中的应用

针对膜式氧合器测试中多传感器数据采集的特性,设计了一种医用膜式氧合器氧扩散渗透率检测的多路数据采集系统;系统以FPGA为主控制模块,对FPGA硬件资源进行功能划分,分别实现A/D转换控制、FIFO数据缓存、时钟分频等功能,最后通过USB接口实现了数据传输;

2011-03-15 15:16:08 21

21

21

21基于SATA硬盘和FPGA的高速数据采集存储系统

为解决现有采集存储系统不能同时满足高速率采集,大容量脱机且长时间持续存储的问题,设计了一种基于SATA硬盘和FPGA的数据采集和存储方案。本设计由AD9627转换芯片,Altera Cyclone系列

2011-11-15 11:35:19 169

169

169

169基于C8051F360和FPGA的高速数据采集系统设计

随着现代科学研究和工业生产对数据采集要求的日益提高,很多场合都需要对高频模拟信号进行高速、商精度的t化采集。本文针对高速数据采集系统中的实时性、采集速率等问题提出了

2011-11-16 12:55:34 114

114

114

114高速数据采集系统中CPLD的应用

CPLD在高速数据采集系统中的应用! 介绍了高速数据采集系统的整体框架分析了其中的通用部分CPLD系列产品的特点及其开发软件.CPLD根据高速数据采集系统的需要VHDL语言的形式,介绍了由

2011-12-17 00:12:00 26

26

26

26高速高精度的数据采集系统的设计与实现

设计了基于FPGA与ARM 芯片的数据采集系统,FPGA 负责控制A/D转换器,保证了采样精度与处理速度,ARM负责逻辑控制及与上位机交互的实现,并将采集到的数据通过USB高速上传至主机进行实时处理。对模拟数据采集的测试结果达到了较高的采样精度和速度,验证了整个系统的高速性和可行性。

2017-11-18 12:47:10 4154

4154

4154

4154

利用AD574A设计基于FPGA的高速数据采集系统

利用AD574A设计基于FPGA的高速数据采集系统,系统包含内嵌双口,在FPGA内部实现的RAM用于写入操作;地址计数器,用于提供存储地址保存采集数据。具备高采样精度、高集成度,并且速度快、灵活性强、可靠性高,易于升级与扩展。

2017-12-18 17:37:20 7689

7689

7689

7689

如何使用FPGA矩阵用于高速数据采集与控制系统的设计

提出了FPGA之间以及FPGA与外围A/D和D/A芯片的数据传输方案。最后揭示了光纤通信驱动的数据采集与控制过程及总线冲突解决策略。所设计的系统具有成本低、灵活性强的特点,实验表明该系统能够满足可靠性和实时性要求。

2018-10-23 19:32:54 5

5

5

5如何使用FPGA和DSP进行高速数据采集系统设计

介绍了1种基于FPGA和DSP的高速数据采集系统的设计和实现,其FPGA采用Altera公司ACEX 1K系列的EPIK50Tcl443器件,DSP芯片采用TI公司TMs320系列

2018-11-07 17:18:24 18

18

18

18高速数据采集记录系统

2018年8月,西安慕雷电子发布了全球顶级高速数据采集记录存储系统,采样率高达4GSPS,分辨率12bit,模拟带宽2GHZ,记录存储带宽高达6GB/S!西安慕雷电子供应全球顶级高速数据采集卡及超宽

2018-11-13 21:21:34 486

486

486

486如何使用FPGA设计高速实时数据采集存储系统的资料概述

设计了以FPGA器件XCSVIXS0为核心处理芯片的高速数据采集存储系统。在XCSVLXS0内部实现的高速状态机和相位延迟时钟作用下,采用4片高速A/D器件流水工作来提高数据采集速度。同时

2018-12-10 16:47:01 22

22

22

22如何使用FPGA进行高速雷达数据采集系统的设计概述

高速雷达数据采集系统的设计方法。该系统由FPGA芯片完成各芯片之间的逻辑控制,具有设计灵活、结构简单、实时性高、可靠性高等优点。

2018-12-24 15:20:00 19

19

19

19基于PIC总线的高速数据采集系统

本文详细介绍了一种基于 PCI 总线的高速数据采集系统的原理、组成和功能以及在 Windows 2000 环境下进行数据采集和存储的方法。该系统用于某型号卫星下行的高速数据采集。系统设计与技术的通用性可应用于其它类似的高速数据采集与处理系统中。

2021-04-14 14:29:30 13

13

13

13基于FPGA的高速数据采集系统该怎么设计?

点击上方 蓝字 关注我们 目前,在数据采集系统的硬件设计方案中,有采用通用单片机和USB相结合的方案,也有采用DSP和USB相结合的方案,前者虽然硬件成本低,但是时钟频率较低,难以满足数据采集系统

2023-10-06 14:55:02 1256

1256

1256

1256

电子发烧友App

电子发烧友App

评论