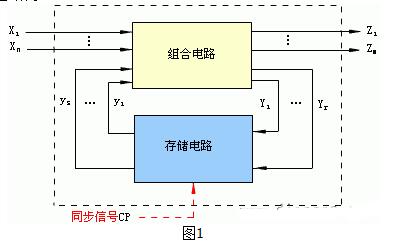

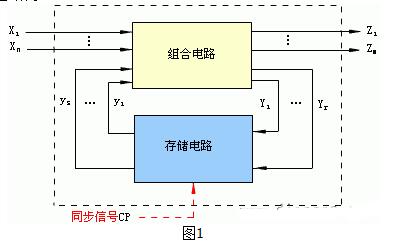

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

2018-01-31 09:27:23 53525

53525

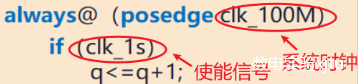

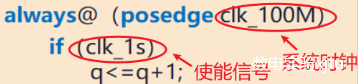

了解吗? (1)纯组合逻辑电路的缺点在哪? (3)纯组合逻辑电路完成不了什么功能? (2)为什么需要时钟和寄存器呢? 带着这三个疑问我们来认识一下时序逻辑电路。 二. 同步时序逻辑电路的作用 1. 时序逻辑电路对于组合逻辑的毛刺具有容忍度,

2020-12-25 14:39:28 4147

4147

时序逻辑电路的精华——计数器

2022-12-29 09:23:56 1010

1010 数字逻辑电路分为组合逻辑电路和时序逻辑电路。时序逻辑电路是由组合逻辑电路和时序逻辑器件构成(触发器),即数字逻辑电路是由组合逻辑和时序逻辑器件构成。

2023-03-21 09:49:49 476

476 时序逻辑电路的特点是输出信号不仅与电路的输入有关,还与电路原来的状态有关。

2023-09-17 16:22:32 1343

1343

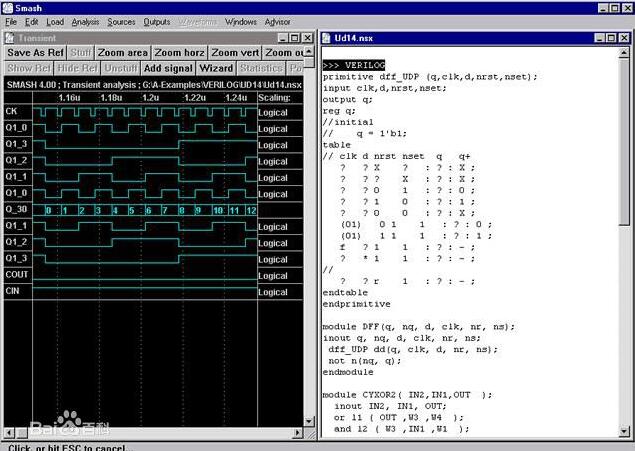

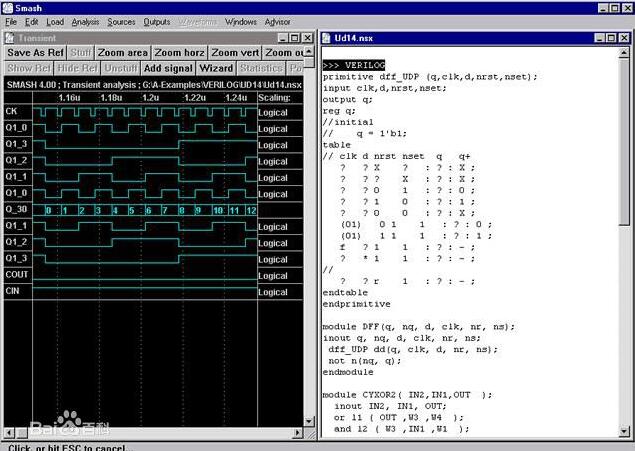

嵌入式开发Verilog教程(二)——Verilog HDL设计方法概述前言一、Verilog HDL语言简介1.1 Verilog HDL语言是什么1.2前言在数字逻辑设计领域,迫切需要一种共同

2021-11-08 09:30:31

Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言也是一种结构描述

2019-09-06 09:14:16

设计方法学等方面的基本概念出发来研究和探讨用于数字信号处理等领域的复杂硬线逻辑电路的设计技术和方法。特别强调利用Verilog硬件描述语言的Top-Down设计方法的介绍。Verilog HDL电路设计指导书

2018-12-10 15:31:15

时序逻辑电路的特点

2019-10-08 05:34:53

时序逻辑电路的设计实验1 进一步强化EDA仿真软件的使用;2 掌握利用MSI

2009-03-19 15:10:18

时序逻辑电路自启动功能怎么判断呢?求大神解答

2023-05-10 14:46:33

时序逻辑电路设计6.1 基本D触发器的设计6.2 JK触发器6.3 带异步复位/置位端的使能T触发器6.4 基本计数器的设计6.5 同步清零的计数器6.6 同步清零的可逆计数器6.7 同步预置数的计数器

2009-03-20 10:04:53

逻辑电路的纠错技术是如何实现的?纠错技术在逻辑电路中有什么作用?

2021-06-18 09:50:31

12.Verilog HDL语言实现时序逻辑电路第三阶段虽然利用第二阶段课程学到的HDL基本语法可以完成大部分的FPGA功能,但相对复杂的FPGA系统设计中,如果能够合理的应用Verilog HDL

2014-11-30 17:38:06

常用语句11.Verilog HDL语言实现组合逻辑电路12.Verilog HDL语言实现时序逻辑电路第三阶段虽然利用第二阶段课程学到的HDL基本语法可以完成大部分的FPGA功能,但相对复杂的FPGA

2014-12-12 09:38:19

逻辑电路 3.8 Verilog HDL语言实现时序逻辑电路 3.9 Verilog HDL语言与C语言的区别与联系 3.10 Verilog HDL程序设计经验 3.11 典型实例3:数字跑表

2012-02-09 15:45:32

fpga时序逻辑电路的分析和设计 时序逻辑电路的结构及特点时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。[hide][/hide]

2012-06-20 11:18:44

讲解组合逻辑电路的原理、应用和Verilog实现。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时

2020-04-24 15:07:49

为什么FPGA可以用来实现组合逻辑电路和时序逻辑电路呢?

2023-04-23 11:53:26

应用10.Verilog HDL语言的其他常用语句11.Verilog HDL语言实现组合逻辑电路12.Verilog HDL语言实现时序逻辑电路第三阶段虽然利用第二阶段课程学到的HDL基本语法可以完成大部分的FPGA

2012-06-13 17:43:58

句11.Verilog HDL语言实现组合逻辑电路12.Verilog HDL语言实现时序逻辑电路第三阶段 虽然利用第二阶段课程学到的HDL基本语法可以完成大部分的FPGA功能,但相对复杂的FPGA系统设计中

2018-09-19 11:34:03

句11.Verilog HDL语言实现组合逻辑电路12.Verilog HDL语言实现时序逻辑电路发烧友FPGA技术实训,深圳-广州-郑州-长沙-南宁均有分点,详情联系郭老师qq754634522 电话

2015-10-27 17:57:38

涉及时序逻辑电路的实例,希望能够帮助大家理解在FPGA中实现时序逻辑电路。与组合逻辑电路相比,时序逻辑电路需要时钟的参与,电路中会有存储器件的参与,时序逻辑电路的输出不仅取决于这一时刻的输入,也受此

2022-07-22 15:25:03

Verilog程序模块的结构是由哪些部分组成的?如何去实现时序逻辑电路和组合逻辑电路的设计呢?

2021-11-03 06:35:57

我们在实现FPGA逻辑电路时,时常会在Verilog代码里添加一些约束原语。前言我们在描述FPGA电路时,我们经常会在电路里添加一些像这样的约束原语:通过这种方式,我们可以指导FPGA在综合及布局

2022-07-22 14:28:10

各位大神求救啊用verilog语言实现电子钟

2014-05-04 16:37:51

设计时序逻辑电路时,如何解决电路不能自启动的问题?

是如何解决电路不能自启动,不是‘不能自启动’的定义

2023-05-10 14:44:22

多输入时序电路的基本原理是什么?基于数据选择器和D触发器的多输入时序逻辑电路设计

2021-04-29 07:04:38

组合逻辑电路的基本模块是什么?时序逻辑电路怎样进行工作的?

2021-09-18 09:19:42

1 进一步强化EDA仿真软件的使用;2 掌握利用MSI、可编程器件设计时序逻辑电路的特点、方法;3 掌握时序逻辑电路的调试方法;4&

2009-03-18 20:06:31 47

47 时序逻辑电路的输出不但和当前输入有关,还与系统的原先状态有关,即时序电路的当前输出由输入变量与电路原先的状态共同决定。为达到这一目的,时序逻辑电路从某一状态

2009-03-18 22:13:04 71

71 Verilog HDL 综合实用教程第1章 基础知识第2章 从Verilog结构到逻辑门第3章 建模示例第4章 模型的优化第5章 验证附录A 可综合的语言结构附录B 通用库

2009-07-20 11:21:13 86

86 采用 Verilog HDL 语言在Altera 公司的FPGA 芯片上实现了RISC_CPU 的关键部件状态控制器的设计,以及在与其它各种数字逻辑设计方法的比较下,显示出使用Verilog HDL语言的优越性.关键词

2009-08-21 10:50:05 69

69 同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步时序逻辑电路模型与描述方法开始,介绍同步时序逻辑电路的分析步骤和方法。然后

2009-09-01 09:06:27 0

0 异步时序逻辑电路:本章主要从同步时序逻辑电路与异步时序逻辑电路状态改变方式不同的特殊性出发, 系统的介绍异步时序逻辑电路的电路结构、工作原理、分析方法和设计方法。

2009-09-01 09:12:34 0

0 摘要:通过实际例子,阐述了次态卡诺图在分析和设计时序逻辑电路中的使用方法。该方法的使用可以使时序逻辑电路的分析和设计得到一定的简化,过程中思路清晰,状态转换直

2010-04-28 10:03:10 21

21 组合逻辑电路的特点是:在任意时刻,电路产生的稳定输出仅与当前时刻的输入有关。时序逻辑电路则与它不同,其特点是:在任意时刻电路产生的稳定输出不仅与当前时刻的输入

2010-05-30 09:46:59 44

44 数字逻辑电路按逻辑功能和电路组成的特点可分为组合逻辑电路和时序逻辑电路两大类。

2010-08-10 11:51:58 39

39 数字逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路在任一时刻的稳定输出只取决于当前的输入,而与过去的输入无关。在结构上,组合逻辑电路仅由若干逻

2010-08-12 15:54:42 0

0 数字电路分为组合逻辑电路(简称组合电路)和时序逻辑电路(简称时序电路)两类。在第三章中讨论的电路为组合电路。组合电路的结构模型如图4.1所示,它的输出函数表达式为

2010-08-13 15:23:02 24

24 在讨论时序逻辑电路的分析与设计之前,让我们先回顾一下在第四章中介绍过的时序电路结构框图和一些相关术语。时序电路的结构框图如图5.1所示.。

2010-08-13 15:24:35 69

69 数字集成电路,根据原理可分为两大类,既组合逻辑电路和时序逻辑电路。

组合逻辑电路的组成是逻辑门电路。电路的输出状态仅由同一时刻的输入状态决定,与电路的原

2010-08-18 15:05:23 55

55 实验十六 时序逻辑电路? 实验(1) 计数器?一、实验目的?⒈ 熟悉计数器的设计方法及工作原理。?⒉ 了解同步计数器与异步计数器的区别。?⒊ 应用

2008-09-24 22:17:08 3210

3210

第二十七讲 同步时序逻辑电路的设计

7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步时序逻辑电路的设计方法

2009-03-30 16:31:56 3438

3438

时序逻辑电路的分析方法

1. 时序逻辑电路的特点 在时序逻辑电路中,任意时刻的输出信号不仅取决于当时的输入信

2009-04-07 23:18:11 8146

8146

时序逻辑电路分析实例

例1 分析图所示电路的逻辑功能。设起始状态是

2009-04-07 23:20:25 4398

4398

时序逻辑电路的特点

在第三章所讨论的组合逻辑电路中,任一时刻的输出信号仅仅取决于该时刻的输入信号,而与电路原来

2009-09-30 18:19:22 9900

9900

Verilog HDL程序基本结构与程序入门

Verilog HDL程序基本结构

Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的

2010-02-08 11:43:30 2185

2185 Verilog HDL语言简介

1.什么是Verilog HDLVerilog HDL是硬件描述语言的一种,用于数

2010-02-09 08:59:33 3609

3609 VHDL和Verilog HDL语言对比

Verilog HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。VHDL是在1987年成为IEEE标准,Verilog HDL

2010-02-09 09:01:17 10317

10317 时序逻辑电路实例解析

一、触发器 1、电位触发方式触发器

2010-04-15 13:46:25 5041

5041 Verilog_HDL的基本语法详解(夏宇闻版):Verilog HDL是一种用于数字逻辑电路设计的语言。用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。Verilog HDL既是一种行为描述的语言也是一种结

2012-10-08 14:48:31 0

0 主要讲了时序逻辑电路的相关知识,能够方便大家学习使用

2016-02-29 14:25:53 0

0 电子专业单片机相关知识学习教材资料之时序逻辑电路的分析与设计

2016-09-02 14:30:26 0

0 Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),Verilog HDL语言是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2017-02-11 14:00:20 35998

35998

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。而C语言是一门通用计算机编程语言,应用广泛。

2017-12-08 16:43:30 11804

11804 时序逻辑电路其任一时刻的输出不仅取决于该时刻的输入,而且还与过去各时刻的输入有关。常见的时序逻辑电路有触发器、计数器、寄存器等。由于时序逻辑电路具有存储或记忆的功能,检修起来就比较复杂。

2018-04-09 16:00:00 5673

5673

组合逻辑电路和时序逻辑电路都是数字电路,组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 17:26:04 91326

91326

分析时序逻辑电路也就是找出该时序逻辑电路的逻辑功能,即找出时序逻辑电路的状态和输出变量在输入变量和时钟信号作用下的变化规律。上面讲过的时序逻辑电路的驱动方程、状态方程和输出方程就全面地描述了时序逻辑电路的逻辑功能。

2018-01-30 18:55:32 123039

123039

时序逻辑路是数字电路的一种,时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2018-01-30 19:19:25 63960

63960

本文开始介绍了时序逻辑电路的特点和时序逻辑电路的三种逻辑器件,其次介绍了时序逻辑电路的组成与时序逻辑电路检修方法,最后介绍了时序逻辑电路的应用举例。

2018-03-01 10:53:38 106878

106878

Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2018-03-23 11:46:04 94153

94153

本文档的主要内容详细介绍的是如何使用Verilog-HDL做CPLD设计的时序逻辑电路的实现。

2018-12-12 16:25:46 8

8 本文档的主要内容详细介绍的是数字电路教程之时序逻辑电路课件的详细资料免费下载主要内容包括了:一 概述,二 时序逻辑电路的分析方法,三 若干常用的时序逻辑电路,四 时序逻辑电路的设计方法,五 时序逻辑电路中的竞争冒险现象

2018-12-28 08:00:00 12

12 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-02-26 15:22:20 30485

30485 时序逻辑电路是由组合逻辑电路与记忆电路(又称存储电路) 组合而成的。 常见时序逻辑电路有触发器、 寄存器和计数器等。

2019-02-26 15:25:01 49624

49624 组合逻辑电路是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路不仅仅取决于当前的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

2019-02-26 15:32:30 62614

62614 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2019-05-16 18:32:37 7636

7636

中国大学MOOC

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-08-06 06:12:00 3449

3449

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-05 07:08:00 2539

2539

大家都知道软件设计使用软件编程语言,例如我们熟知的C、Java等等,而FPGA设计使用的是HDL语言,例如VHDL和Verilog HDL。说的直白点,FPGA的设计就是逻辑电路的实现,就是把我们

2019-12-05 07:11:00 1497

1497

本课程以目前流行的Xilinx 7系列FPGA的开发为主线,全面讲解FPGA的原理及电路设计、Verilog HDL语言及VIVADO的应用,并循序渐进地从组合逻辑、时序逻辑的开发开始,深入到FPGA的基础应用、综合应用和进阶应用。

2019-12-02 07:10:00 2914

2914

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2019-11-28 07:02:00 2638

2638 大家都知道软件设计使用软件编程语言,例如我们熟知的C、Java等等,而FPGA设计使用的是HDL语言,例如VHDL和Verilog HDL。说的直白点,FPGA的设计就是逻辑电路的实现,就是把我们

2019-12-05 07:10:00 2977

2977

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。

2019-11-13 07:03:00 3029

3029 Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2019-11-20 07:00:00 5088

5088 硬件描述语言基本语法和实践

(1)VHDL 和Verilog HDL的各自特点和应用范围

(2)Verilog HDL基本结构语言要素与语法规则

(3) Verilog HDL组合逻辑语句结构

2019-07-03 17:36:00 53

53 Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL

2020-06-17 16:13:11 12910

12910 本文档的主要内容详细介绍的是模拟电路教程之时序逻辑电路的课件资料免费下载包括了:1 概述,2 时序逻辑电路的分析方法,3 若干常用的时序逻辑电路,4 时序逻辑电路的设计方法。

2020-06-22 08:00:00 13

13 HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL和VHDL是世界上最流行

2020-08-26 09:14:31 53460

53460 Verilog HDL是一种硬件描述语言(HDL:Hardware Description Language),以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

2020-11-02 17:30:55 23

23 在现阶段,作为设计人员熟练掌握 Verilog HDL程序设计的多样性和可综合性,是至关重要的。作为数字集成电路的基础,基本数字逻辑电路的设计是进行复杂电路的前提。本章通过对数字电路中基本逻辑电路的erilog HDL程序设计进行讲述,掌握基本逻辑电路的可综合性设计,为具有特定功能的复杂电路的设计打下基础

2020-12-09 11:24:00 33

33 Verilog HDL是一种以文本形式描述数字系统硬件的结构和行为的硬件描述语言,也可描述逻辑电路图、逻辑表达式等。Verilog HDL和VHDL是目前主流的、最受欢迎的两种硬件描述语言。

2021-07-23 14:36:55 9910

9910 笔试时也很常见。 [例1] 一个简单的状态机设计--序列检测器 序列检测器是时序数字电路设计中经典的教学范例,下面我们将用Verilog HDL语言来描述、仿真、并实现它。 序列检测器的逻辑功能描述

2021-08-10 16:33:55 6561

6561

嵌入式开发Verilog教程(二)——Verilog HDL设计方法概述前言一、Verilog HDL语言简介1.1 Verilog HDL语言是什么1.2前言在数字逻辑设计领域,迫切需要一种共同

2021-11-03 16:36:01 13

13 笔试时也很常见。[例1] 一个简单的状态机设计--序列检测器序列检测器是时序数字电路设计中经典的教学范例,下面我们将用Verilog HDL语言来描述、仿真、并实现它。序列检测器的逻辑功能...

2021-12-17 18:28:40 15

15 时序逻辑电路——任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。

2022-12-05 14:49:30 7

7 数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入

2023-03-14 17:06:50 4815

4815

时序电路的考察主要涉及分析与设计两个部分,上文介绍了时序逻辑电路的一些分析方法,重点介绍了同步时序电路分析的步骤与注意事项。 本文就时序逻辑电路设计的相关问题进行讨论,重点介绍时序逻辑电路的核心部分——计数器。

2023-05-22 17:01:29 1882

1882

时序逻辑电路分析和设计的基础是组合逻辑电路与触发器,所以想要分析和设计,前提就是必须熟练掌握各种常见的组合逻辑电路与触发器功能,尤其是各种触发器的特征方程与触发模式,因此前几文的基础显得尤为重要。 本文主要介绍时序逻辑电路的分析方法。

2023-05-22 18:24:31 1983

1983

时序逻辑电路分为同步时序逻辑电路和异步时序逻辑电路两大类。

2023-06-21 14:35:58 2539

2539

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。 Verilog HDL

2023-08-29 15:58:29 0

0 电子发烧友网站提供《时序逻辑电路电子课件.ppt》资料免费下载

2023-11-21 14:43:40 0

0 时序逻辑电路是一种能够存储信息并根据时钟信号按照特定顺序执行操作的电路。它是计算机硬件中非常重要的一部分,用于实现存储器、时序控制器等功能。与之相对的是组合逻辑电路,它根据输入信号的组合情况,立即

2024-02-06 11:18:34 497

497

电子发烧友App

电子发烧友App

评论