和一个产品的任何其他方面一样,产品说明书也可以得到不断的改进,厂商正努力地详细阐明产品说明书1。然而,市场上已经遗留了许多产品/产品说明书版本,对新版本或者更早的版本来说,不同标准的采用也取决于不同的因素。即使有一些特定的标准已经公开发表(如参考书目 2 所提到的),标准的统一仍然是遥遥无期。

本文的目的就在于突出不同厂商或同一厂商在为不同的高速模数转换器 (ADC) 撰写产品说明书时所采用的标准之间的差异。表 1 是选择正确器件时可以使用的速查表。

| 规范 | 需要考虑的事项 |

| 功耗 | 在相同条件使用时,确保包括输出电源,并且该电源符合规定。 |

| 输入时钟放大器 | 如果您想对高输入频率进行采样,请查询差动时钟输入和输入时钟放大器。 |

| SNR、SINAD、 SFDR、THD |

要注意 dB 的单位,它们可能是指 dBc 或 dBFS。 |

| 输出时序 | 确保输出时序规定正确,且具有足够的窗口来采集数据。 一些器件提供了一个具有更佳时序窗口的输出时钟,以实现更轻松的接口。 |

| 输入带宽 | 没有必要确保器件性能要达到规定的频率。 |

| 总体规范 |

|

表 1 选择高速 ADC 的速查表

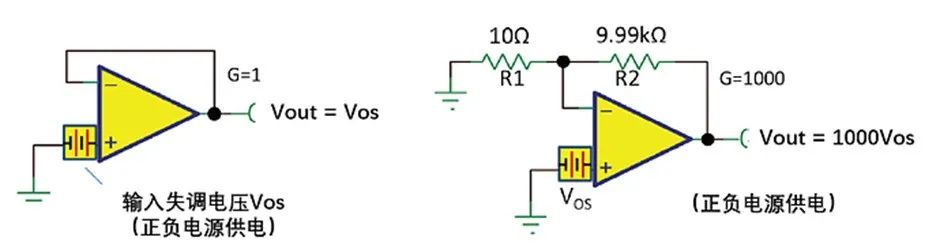

dB、dBc 与 dBFS 的比较

评估高速 ADC 产品说明书所示性能的一个主要标准是动态特性或诸如 SNR, SINAD、THD 以及 SFDR 的交流可调规范。例如,假设 SINAD(也称为 SNDR 或 SNRD)为信噪比,即信号功率与其他频段功率(失真与噪声)总和的比值。通常,把这个比值转换成对数值并以 dB 表示。

产品说明书间最大的差异在于单位的选择,特别应用于选择信号功率的标准。撇开导致这种差异的细节,我们来看一下信号功率完全可以用于测量的信号功率3,或者可以是类似满量程的信号的外推功率。为了避免混淆,TI 将第一种情况下的单位记作 dBc(dB 与载波的比),将第二种情况记作 dB(用于较早的产品说明书)或 dBFS(dB 与满量程的比,用于最新的产品说明书)。虽然两者之间没有主次之分,并且下文将说明它们之间可以彼此推导,但是当厂商只以“dB”为单位进行说明的时候还是会产生混淆。在 TI 的两家竞争对手撰写的产品说明书中,“dB”等于 dBc,而在第三家竞争对手撰写的产品说明书中,“dB”等于 dBFS。

什么因素会影响最终的比较结果呢?假设以-1 dBFS 的输入振幅测量来自不同厂商的两个转换器。这就意味着在测试期间,输入值是在满量程以下 1dB 的正弦曲线,换句话说,振幅 (A) 约为 ADC 满动态量程的 90%。再假设两个转换器性能相同,因此具有相同的噪声与失真功率。在第一种情况下(“dB”等于dBc),厂商用输入功率 (A) 除以噪声加失真功率 (N+D) 来计算信噪比SINAD1。在第二种情况下(“dB”等于 dBFS),厂商推导信号功率至满量程,在这种情况下导致最终的数值增加了 1dB(当输入为 -1dBFS 时)。因此,SINAD2 = SINAD1 + 1。第一家厂商的器件看起来似乎差了 1dB,但实际上与第二家厂商的器件是相同的。dBc 的值可以从 dBFS 值求得,只要加上输入振幅(以 dBFS 为单位):以 dBc 为单位的规范=以 dBFS 为单位的规范+以 dBFS 为单位的AIN。

当我们比较以 dBc 规范表示的两个转换器时,另一点值得注意的是输入振幅也会因器件的不同而不同。很显然,随着输入振幅的减小,信号值(在 dBc 规范中)也极可能变得很小(因为信号功率减小时一些噪声底限的组成却保持不变)。因此,为了使之比较有意义,两个输入振幅必须相等。只要将两个输入振幅的差异添加到由较小的输入振幅获得规范,就可以做出很好的推断。

显然由于大多数转换器的规定信号都接近于满量程,最后信号水平的差异(取决于所使用的单位)通常不会大于 2 dB。但是信号水平的差异不仅可以代表某些应用相当大的差异,而且还会影响最终产品设计的增益甚至影响整个设计。

最终的问题是如何分辨 ADC 产品说明书中的 dB 是 dBc 规范还是 dBFS 规范。一个最简单的方法是直接询问厂商;如果行不通,设计人员可以查看产品说明书的典型性能的曲线图部分。厂商通常都会针对 dBc 和 dBFS 规范给出不同的曲线图,可以根据曲线图的数值与产品说明书中规定的数值进行比较。

功耗规范

功耗是产品说明书的另一个常见的差异点。TI 习惯上在产品说明书的首页列出典型工作状态下转换器的总功耗。这些状态包括在最高采样速率下的输入差与低频或直流的比较,以及在数字侧每一引脚上施加 10-pF 的负载。当然,TI 也开始分离内核功耗(模拟,AVDD)与数字供电损耗(输出 DVDD)。这主要是因为其他厂商几乎都只标注了模拟功耗而不包括接口功耗。一些厂商在产品说明书里列出了接口功耗,但是用户必须注意一些测量条件,例如输入频率,每个引脚的输出负载以及输出电压,这些都会显著的影响测量值。

此外,还必须特别注意 ADC 可能有的特有模式。并不只是 TI 的产品说明书存在这种情况,一些厂商的转换器在模式 A 下进行功耗测量并在产品说明书中列出,但是其他动态规范却在模式 B 下给出。再例如,对于那些可承受较宽数字电源电压的转换器而言,产品说明书在最高 DVDD 电压下给出时序规范,但却在最低 DVDD 电压下给出功耗值。

最后,还必须注意转换器对功率的贡献。一些转换器可能以丢失内部信息为代价来节省功率损耗,例如接受差动时钟(为了实现更低的噪声/抖动)所需要的参考电压或时钟放大器、诸如 PECL 或 LVDS 的小摆幅时钟电平,或者截平滤波时钟(正弦曲线)。这个问题将在下文进一步阐述。

时钟信号

为了获得最佳的 ADC 性能4,时钟信号是最令人担心的问题。虽然所有的 ADC 都有一个时钟输入端,但其中一些要比另一些更容易使用。最关键的问题是时钟抖动、占空比以及必须的时钟电平,当用高输入频率进行采样时,能够大体上获得较好的性能参数。

为了实现低抖动,用户通常使用带通滤波器过滤时钟信号来达到该目的。这还将产生 50% 的占空比,接近于许多 ADC 的最佳条件。不过,由于该滤波器的插入损耗时钟信号振幅将受到影响,且时钟信号将变成正弦曲线而不是方波。为了接收高质量的时钟信号,TI 和其他一些厂商在 ADC 的输入端添加了时钟放大器。它的作用是将正弦曲线修正成方波并为内部电路的时钟循环提供所需的增益。此外,时钟放大器还提供了差动接口,能够减小时钟信号线路中噪声耦合的影响,从而减小抖动。当然,这是以增加 ADC 的功耗为代价的。

然而,一些 ADC 可能还需要 CMOS 电平的方波时钟信号。这类 ADC 的输入必须是单端口的,而且能够抑制外部噪声源与时钟路径耦合。大部分此类 ADC 是为了对低输入频率(50 MHz 以下)进行采样并且能够获得很好的性能。医学超声波就是此类 ADC 的一种典型应用。不过,用户在更高的输入频率(例如通讯应用中)下为了获得高信噪比(大于 60s),就需要提供外部元件来使时钟信号变成方波,并有效地增大功率与电路板面积。即使有了这些外部元件,用户仍然必须考虑单端接口,而且最终的设计很可能不能获得 ADC 采用内部时钟放大器时所能达到的最优性能。

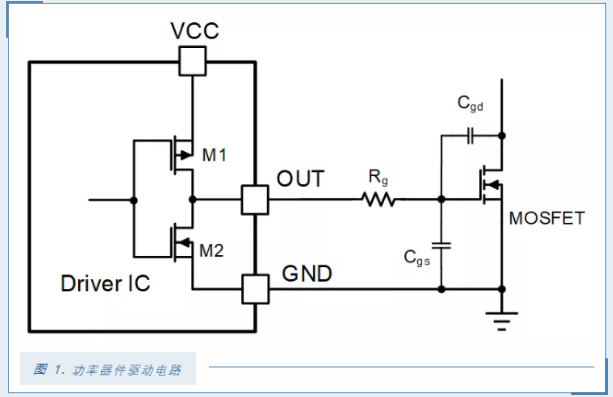

为了提供一致的产品说明书,TI 在相同时钟条件下的产品说明书中使用了相同的图表与性能参数。对于具有差动输入时钟信号的器件而言,通常采用正弦曲线,虽然它并不是 ADC 的最佳条件(由于时钟边缘压摆率的限制)。为了涵盖转换器所有可能的应用情况,TI 开始在产品说明书中引入了 3D 等高线图表(请参见图 1),这就允许用户可以得到在给定输入与采样频率下的典型性能。我们知道,输入时钟信号的所有条件在试验时都是保持不变的,除非改变采样频率。这意味着如果使用正弦波时钟信号,减小采样频率将会使时钟边缘变慢,从而加剧实际的抖动。这是每个 ADC 普遍存在的现象,4但是 TI 设计的 ADC 能够尽可能地将抖动最小化。虽然这是最坏的情况,而且减小抖动的技术有很多种,但是在实验中改变时钟条件是不公平的;同样的,如果保持时钟条件不变,那么信噪比 SNR 将随着抖动的增加而降低。用户必须要知道,如果没有时钟放大器,性能的降低可能更多。此外,用户还必须要清楚如果能够提供一个抖动很小的方波时钟信号,那么 ADC 的性能就会有很大的提高。

图 1 SNR 与输入和采样频率5的曲线关系

输出时序

为了捕捉传输到 FPGA、ASIC、DDC 或其他跟随 ADC 的逻辑器件的输出数据,用户必须要知道输出数据的窗口是稳定的。不过,重点是大多数厂商均致力于提供一致且完善的产品说明书限制。这是因为用于生产的最终测试结果受一些因素的影响,例如自动测试设备的精度、不能直接访问输出端(数据正在缓冲中)、很难像产品说明书一样设置相同的条件(例如数字负载)等等。为了克服这些局限性,TI 通过设计与特征化(即用统计方法来设置这些参数),当生产中不对设备进行测试时,这能促使我们设置更宽的防护频带。而如果将相同的限制条件用于其他厂商的话,经常会导致不完善或不精确的产品说明书。

设计人员应对没有任何质保书的器件、有质保书但是条件不切实际的器件(例如 0-pF 负载)、没有明确用于捕获数据所需的参数的器件(例如,给出了建立时间但没有给出保持时间)、没有说明规范所使用的 VOH 和 VOL电平的器件(例如,给出从 50% 到 50% 的信息,但是要推导出 VIH/VIL 逻辑电平却很麻烦)、或者没有说明对整个工作温度范围内详细参数的器件进行明确的询问。

此外,为了改进数据捕获窗口,TI 与其他厂商均提供了一款输出时钟,与输入时钟相比该时钟能够更好地跟踪输出数据。使用输出时钟可以减小应用中的时序局限。

最后,请注意,建立与保持时间的定义和门电路建立与保持时间的对应部分相同。在门电路中,建立时间表示数据在门电路输入端准备好的时间比时钟边缘闭锁它的时间提前了多少。时间提前得越多,使用该闭锁门电路就越困难。在 ADC 中,建立时间表示数据稳定时间比输入或输出 ADC 时钟边缘提前了多少。建立时间越长,捕获数据就越容易。这些规则在保持时间上也同样适用。

过程增益

与 SNR 的两个参数相比较,用户必须考虑到 ADC 的采样速率。信噪比可通过对收敛于奈奎斯特曲线的总体噪声底限进行积分得到。当然,用户的信号只会占据一些带宽;只有在这个带宽上的噪声才会影响到信号,而其他噪声可由数字滤波器滤除。对于相同的 SNR 而言,采样速率高的 ADC 噪声底限比较低。例如,一个 200kHz 带宽,信噪比为 90-dBFS 的 ∆∑ 型 ADC 的性能在理论上比产品说明书中规定的信噪比为 75-dBFS、100 MSPS 的 14 位 ADC—— ADS5424 要好。当然,如果在使用 ADS5424 对 200-kHz 带宽进行采样之后(明显超过 100 MSPS 的采样率),我们采用数字滤波来滤除带宽外的噪声(从 200 kHz 直到 50 MHz),ADS5424 的等效信噪比在这一带宽上为:

SNR200 kHz = 75 + 10×log10(50×106/200×103) = 99 dBFS >> 90 dBFS。

ADS5424 的信噪比将明显优于 ∆∑ 型 ADC(为了示例,假设噪声在奈奎斯特曲线上均匀分布,也就是说没有明显的闪烁噪声影响)。前述方程式的第二项称为过程增益。随着过采样比的增加,用户在相同信噪比每增加采样率一倍,噪声底限就会降低 3 dB。换言之,相关频带上的等效精度将增加 0.5 比特。

数据适用的条件与最小值

如果没有明确的条件,那么规范将是没有意义的。在广告业、市场营销材料以及选择参数表中这一点尤其重要,条件能够简化产品说明书显示的信息,但在某些情况下,并没有提到测量条件。

同时,典型值通常代表了分布的平均值。不过,用户应注意看一下最小值,特别是当器件在某一特定范围内工作(例如多变的温度环境)时。在典型与最小参数之间的大范围变化会出现一些问题。变化是否由最终测试结果的局限性引起?如果是,则该器件可能适用,但是这样做的风险是只能保证最小值。最差的情况是器件本身所导致的局限性,工艺的变化(不同器件之间)可以导致设计的不耐用性。为了使器件具有较好的稳健性并屏蔽此类问题的一个不错的做法是查看产品说明书中的典型性能变化与电源电压或温度的关系曲线图,如图 2 中的示例所示。

图 2 ADS5424 SFDR 与模拟电源和温度范围的关系曲线6

与功率参数一样,在相同的产品说明书中查找不同的参数(例如 SNR 和 SFDR)时,必须确保它们是在相同条件下给出的参数。例如,某些器件的 SFDR 模式以牺牲 SNR 为代价来改善 SFDR;或者它们有不同的输入范围,这会影响到 SFDR(在较小输入范围内较好)和 SNR(在较大输入范围内较好)。

最后,需注意的是,大多数规范在是在接近满量程范围内给出的。然而,SFDR(在 dBFS 规范中)在输入振幅减小时可能变好也可能变得更糟糕。厂商在最终测试中不能屏蔽很多条件,因为那样会增加测试时间和测试成本;但他们通常会给出说明各种条件影响的典型图表。

输入带宽

通常,输入带宽代表了 ADC 响应平坦度与输入频率的关系。其并没有表明该器件在这些输入频率下能够保持应有的性能。用户必须从图表中核实相关性能;如果图表中没有,用户必须从厂商那里寻求支持或者对器件本身进行评估。

结论

本文详细说明了厂商用于编写高速 ADC 产品说明书的规范之间的主要差异,提早考虑这些差异有助于设计人员避免在设计过程中出现突发问题。

电子发烧友App

电子发烧友App

评论