1 AD9225的结构

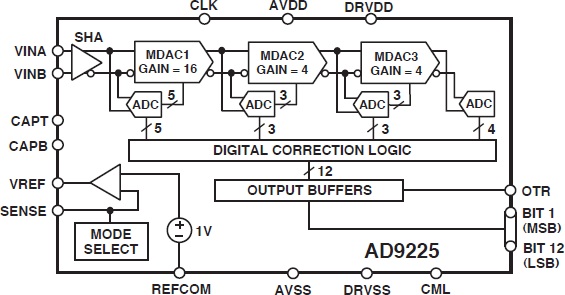

AD9225是ADI公司生产的单片、单电源供电、12位精度、25Msps高速模数转换器,片内集成高性能的采样保持放大器和参考电压源。AD9225采用带有误差校正逻辑的四级差分流水结构,以保证在25Msps采样率下获得精确的12位数据。除了最后一级,每一级都有一个低分辨率的闪速A/D与一个残差放大器(MDAC)相连。此放大器用来放大重建DAC的输出和下一级闪速A/D的输入差,每一级的最后一位作为冗余位,以校验数字误差,其结构如图1所示。

图1 AD9225结构图

2 AD9225的输入和输出

(1) 时钟输入

AD9225采用单一的时钟信号来控制内部所有的转换,A/D采样是在时钟的上升沿完成。在25Msps的转换速率下,采样时钟的占空比应保持在45%~55%之间;随着转换速率的降低,占空比也可以随之降低。在低电平期间,输入SHA处于采样状态;高电平期间,输入SHA处于保持状态。图2为其时序图。图2中:

图2 AD9225时序图

tch——高电平持续时间,最小值为18 ns;

tcl——低电平持续时间,最小值为18 ns;

tod——数据延迟时间,最小值为13 ns。

从时序图可以看出:转换器每个时钟周期(上升沿)捕获一个采样值,三个周期以后才可以输出转换结果。这是由于AD9225采用的四级流水结构,虽然可以获得较高的分辨率,但却是以牺牲流水延迟为代价的。

(2) 模拟输入AD9225的模拟输入引脚是VINA、VINB,其绝对输入电压范围由电源电压决定:

其中, AVSS正常情况下为0 V,AVDD正常情况下为+5 V。

AD9225有高度灵活的输入结构,可以方便地和单端或差分输入信号进行连接。采用单端输入时,VINA可通过直流或交流方式与输入信号耦合,VINB要偏置到合适的电压;采用差分输入时,VINA和VINB要由输入信号同时驱动。

(3) 数字输出

AD9225 采用直接二进制码输出12位的转换数据,并有一位溢出指示位(OTR),连同最高有效位可以用来确定数据是否溢出。图3为溢出和正常状态的逻辑判断图。

图3 溢出和正常状态的逻辑判断图

3 AD9225参考电压和量程的选用

参考电压VREF决定了AD9225的量程,即

满刻度量程= 2×VREF

VREF的值由SENSE引脚确定。如果SENSE与AVSS 相连,VREF是2.0 V,量程是0~4 V;如果SENSE与VREF直接相连, VREF是1.0 V,量程是0~2 V;如果SENSE与VREF通过电阻网络相连,则VREF可以是1.0~2.0 V之间的任意值,量程是0~2VREF;如果SENSE与AVDD 相连,表示禁用内部参考源,即VREF由外部参考电压源驱动。内部电路用到的参考电压是出现在CAPT和CAPB端。表1是参考电压和输入量程的总结。

表1 参考电压和输入量程

4 AD9225的存储方案设计

在高速数据采集电路的实现中,有两个关键的问题:一是模拟信号的高速转换;二是变换后数据的存储及提取。AD9225的采样速度可达25Msps,完全可以满足大多数数据采集系统的要求,故首要解决的关键问题是与存储器的配合问题。 在数据采集电路中, 有以下几种存储方案可供选择。

(1)分时存储方案

分时存储方案的原理是将高速采集到的数据进行分时处理, 通过高速锁存器按时序地分配给N个存储器。虽然电路中增加了SRAM的片数,但使存储深度增加,用低价格的SRAM构成高速数据存储电路,获得较高的(单位速度×单位存储深度)/价格比。但由于电路单数据口的特点,不利于数据的实时处理,并且为使数据被锁存后留有足够的时间让存储器完成数据的存储,需要产生特殊的写信号线 。

(2)双端口存储方案

双端口存储器的特点是,在同一个芯片里,同一个存储单元具有相同的两套寻址机构和输入输出机构,可以通过两个端口对芯片中的任何一个地址作非同步的读和写操作,读写时间最快达到十几ns。当两个端口同时(5 ns以内 )对芯片中同一个存储单元寻址时, 芯片中有一个协调电路将参与协调。双端口存储器方案适用于小存储深度、数据实时处理的场合。由于双端口存储器本身具备了两套寻址系统,在电路的设计时,可以免去在数据存储和读取时对地址时钟信号的切换问题的考虑,使数据变得简单和快捷。

(3)先进先出存储方案

先进先出存储器的同一个存储单元配备有两个口:一个是输入口,只负责数据的写入;另一个是输出口,只负责数据的输出。先进先出(FIFO)存储器方案适用于小存储深度,数据需实时处理的场合。

对用户而言,存储器的存储速度和存储容量是一对矛盾体:双口RAM和FIFO可以实现很高的存储速度,但其存储容量难以满足对大量数据存储的需求;一般的静态RAM虽然速度有限,但其存储深度却是双口RAM和FIFO难以企及的,并且可以容易地实现多片扩展。对高速数据采集系统而言,由于采样速率快、数据多,要求存储深度比较大,实时处理的难度比较高,一般的静态RAM就可以满足速度要求。628512容量为512Kbit,存取时间70 ns,可以满足10Msps以上的采样要求,比较具有典型意义。图4是AD9225与628512的接口电路图,存储方案实际是分时存储的特例。

图4 AD9225与628512的接口图

AD9225输出的12位数据,再加溢出指示位OTR共13位与两片628512相连。两片628512组成并联结构,由同一地址发生器产生地址,同一写信号线控制写操作。20位地址发生器由五片同步计数器74161构成。注意,此处不能采用异步计数器,因为异步计数器的输出延时太大。

存储器的存储过程可以分解成三个过程来讨论:① 地址码加在RAM芯片的地址输入端,选中相应的存储单元,使其可以进行写操作。② 将要写入的数据放在数据总线上。③ 加上片选信号及写信号,这两个有效信号打开三态门,使DB上的数据进入输入回路,送到存储单元的位线上,从而写入该存储单元。

图4所示的接口电路中,地址码信息和数据码信息在同一时钟信号的上升沿产生,片选线由地址发生器的最高位(A19)提供。写信号线是接口的最关键部分,它必须保证在AD9225转换完成以后,在保持地址信息和数据信息不变的情况下,有足够的低电平持续时间完成存储操作。低速的数据采集系统可直接采用CLK作为写信号。高速ADC在使用时,对时钟的占空比要求很高。AD9225要求CLK的占空比在45%~55%之间,如果还直接采用CLK作为写信号,将难以满足要求。例如,如果采样速率为10 Msps,CLK的低电平持续时间仅为50 ns,小于628512的存储时间70 ns,因此,必须要对晶振信号进行适当的逻辑转换以获得足够的写周期。考虑到写信号仅在低电平状态有效,在产生信号时,可以尽量减少高电平的持续时间。经过多次仿真试验,作者采用图5所示的逻辑控制电路来获得相应的写信号。

图5 逻辑控制电路

对应于此逻辑电路的时序如图6所示。

图6 逻辑控制电路时序图

5 结论

本文详细介绍了一种高 速A/D转换芯片AD9225的结构和应用,在比较了各种高速数据采集系统的存储方案的基础上,给出了AD9225与628512存储器的接口电路。该电路实际上是高速ADC与一般RAM接口的缩影。在写信号的实现上,采用了控制逻辑,具有创新性和通用性。

电子发烧友App

电子发烧友App

评论