Hoover 通常,它需要一个可具有高达 1nsRMS 抖动的函数发生器。常常需要采用一个高质量的 RF 发生器或晶体振荡器以从 16 或 18 位 ADC 获得最佳的 SNR 值,即使在相对较低的输入频率

2018-08-28 09:31:02 5393

5393 RCC电路原理与设计及问题解析

RCC电路,单端反激式的一种,结构简单,主要应用在1~200W,首先变压器设计最为重要,RCC电路结构主要包括: 1.

2009-12-14 10:31:05 24103

24103 模数转换器的电源去耦问题解析

尽管高速ADC给电源带来的总负载是稳定的,但需要电流以ADC采样速率和此频率的谐波快速跳变。由于

2011-01-01 12:30:11 990

990 本文即第2部分中,这种组合抖动将用于计算ADC的信噪比 (SNR),之后将其与实际测量情况进行比较。

2012-05-07 11:31:22 1428

1428

模/数转换器(ADC)电路设计中,特别是当系统设计人员需要处理各种摆幅的电压信号时,很容易产生的一个误区是缩小输入信号范围,以适应ADC的满量程范围,这将大大降低信噪比(SNR)。综合来看,低压

2013-09-22 12:12:56 3874

3874

图所示电路是14位、125 MSPS四通道ADC系统的简化图,该电路使用后端数字求和将信噪比(SNR)从单通道ADC的 74 dBFS提升到四通道ADC的78.5 dBFS。这项技术特别适合要求高SNR(如超声和雷达)的应用,并且利用了现代高性能、低功耗、四通道流水线式ADC。

2013-10-30 10:07:29 2206

2206

获得ADC的最佳SNR性能并不仅仅是给ADC输入提供低噪声信号的问题,提供一个低噪声基准电压是同等重要。虽然基准噪声在零标度没有影响,但是在全标度,基准上的任何噪声在输出代码中都将是可见的。对于某个

2022-07-13 09:17:27 1039

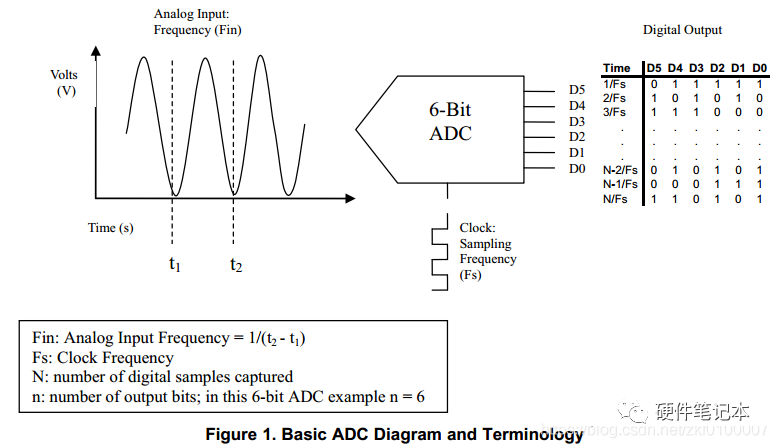

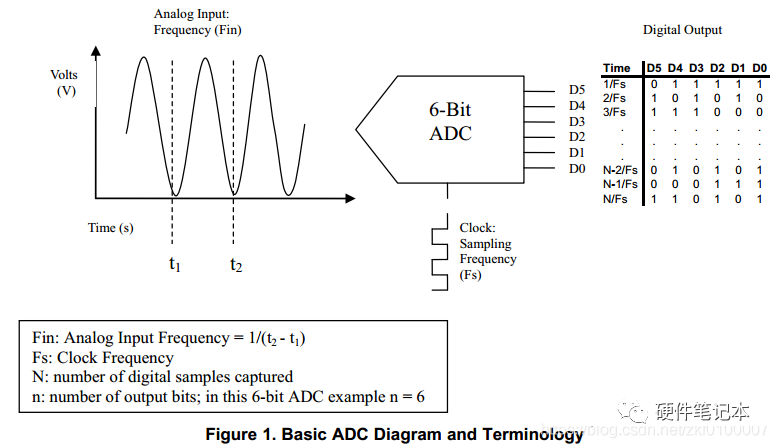

1039 本文的目的是介绍高速ADC相关的理论和知识,详细介绍了采样理论、数据手册指标、ADC选型准则和评估方法、时钟抖动和其它一些通用的系统级考虑。另外,一些用户希望通过交织、平均或抖动(dithering)技术进一步提升ADC的性能。

2023-03-16 09:15:15 4738

4738 本文的目的是介绍高速ADC相关的理论和知识,详细介绍了采样理论、数据手册指标、ADC选型准则和评估方法、时钟抖动和其它一些通用的系统级考虑。 另外,一些用户希望通过交织、平均或抖动(dithering)技术进一步提升ADC的性能。

2023-04-15 14:00:51 1333

1333

您在测试 ADC 的SNR时,您可能会连接一个低抖动时钟器件到转换器的时钟输入引脚,并施加一个适度低噪的输入信号。如果您并未从您的转换器获得SNR产品说明书标称性能,则说明存在

2011-10-12 12:00:09 2661

2661

大家好,我正在尝试使用33210A信号发生器来确定PCB布局不佳的ADC的SNR损耗。来自数据表的ADC的SNR为85dB,我的测量结果为70dB。我需要确定ADC侧的15dB差异以及mych如何来

2019-05-29 12:29:57

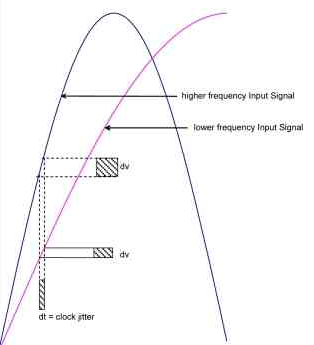

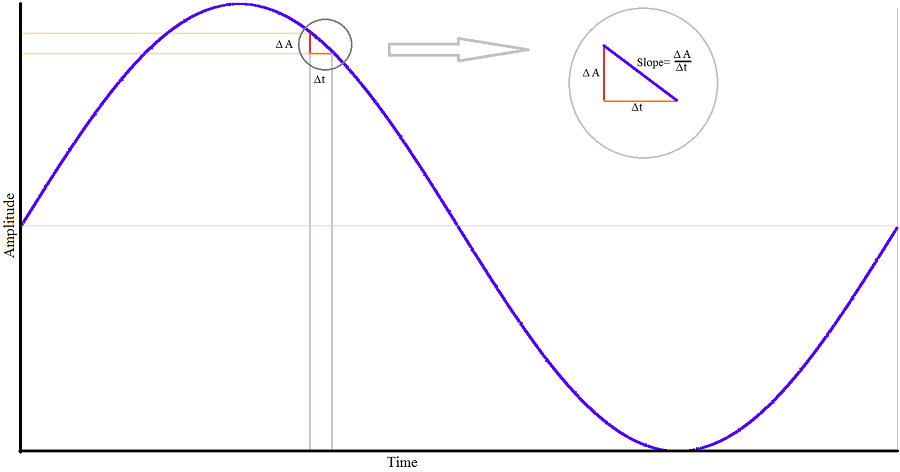

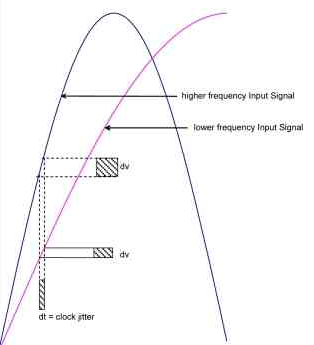

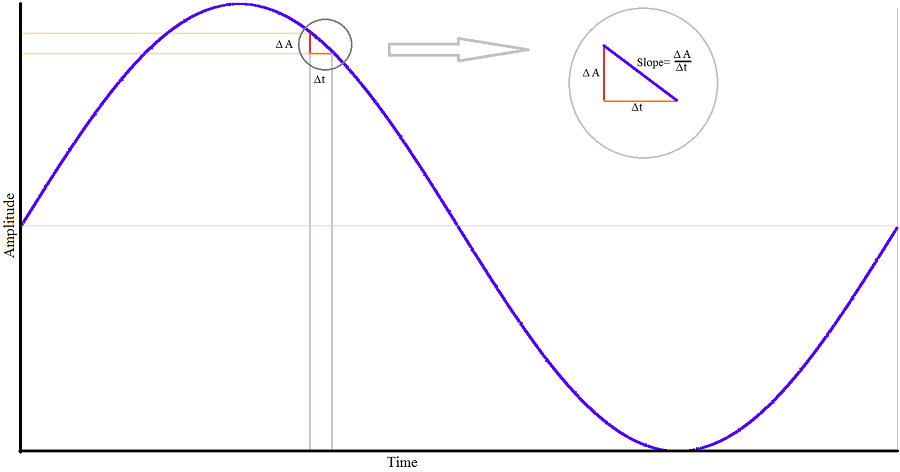

进行采样。这要求具有稳定的采样时 钟,因为任何不理想的时钟源都将产生一定相位噪声。抖动是指采样时钟载波上两个指定频率偏移之间的时段上的相位噪声积分。对于ADC,一般认为宽带噪声是最重要的因素

2019-10-23 08:00:00

来说,测试中需要对 ESG 或 PSG 产生的信号进行进一步的滤波以滤去谐波和杂散信号,滤波器的参数要根据用户实际使用的信号频率范围选择。对于高精度的 ADC 来说,采样时钟的抖动对于测试结果

2018-04-03 10:39:35

/1.8V)的 ADC功耗。因此,将该链的低噪声 LDO去除可以产生巨大的节能效果。去除 LDO 还可以降低设计的板级空间、热量以及成本。 本文阐述了包括超高性能 16 位 ADC 在内的一些 TI 高速

2018-09-26 11:04:47

至关重要。 噪声信噪比(SNR)和失真要求对ADC的选择有帮助,因而一般在设计早期确定。转换器看到的噪声量与其自己的噪声量之比即为SNR。SNR与带宽、信号质量(抖动)和增益相关。提高增益也会提高与之相关

2018-09-17 15:48:29

重新采样数据,产生一个新的清洁数据流。这些器件可显著提高信号质量,而且经常用在抖动规范极为严格的光模块之前。除非距离信号源只有一英寸,否则很可能需要采用一个重定时器。重定时器实例包括DS100RT410

2018-09-13 10:02:04

时钟抖动引起的采样噪声为:

计算SNR为:

为何这里不像《[MT-001_cn] 揭开公式(SNR = 6.02N + 1.76dB)的神秘面纱,以及为什么我们要予以关注》文章里那样,信号用

2023-12-01 08:30:52

C语言习题解析库

2015-03-11 15:20:07

一个放大器系统:ADC + STA339BW + MCU,MCU产生12MHz时钟应用于ADC(连接到MCLK引脚)和STA339BW(连接到XTI引脚)。我不知道会有多少差异,这会影响THD

2019-07-22 16:10:23

采样时钟考量在高性能采样数据系统中,应使用低相位噪声晶体振荡器产生ADC(或DAC)采样时钟,因为采样时钟抖动会调制模拟输入/输出信号,并提高噪声和失真底。采样时钟发生器应与高噪声数字电路隔离

2014-11-20 10:58:30

-Delta ADC常见问题解答 ,欢迎小伙伴们下载~~附件Sigma-Delta ADC 常见问题解答_V2.0.pdf923.4 KB

2018-12-10 11:20:32

技术三千问:【技术三千问】之《玩转ART-Pi》,看这篇就够了!干货汇总【技术三千问】之《AT组件问题汇总与解析》,干货汇总!【技术三千问】之《UART串口问题解析》,干货汇总!【技术三千问】之

2021-08-05 06:54:19

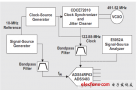

本文为高速数据转换器提供了一个低抖动时钟源的参考设计,目标是在时钟频率高达2GHz时,边沿间抖动《 100fs。对于1GHz模拟输出频率,所产生的抖动信噪比SNR为:-20 × log(2 × π × f × tj) = -64dB。

2021-04-15 06:28:19

DN1013- 了解时钟抖动对高速ADC的影响

2019-07-17 06:41:39

`描述此参考设计展示了高速放大器 THS4509 执行单端至差动转换以驱动高速模数转换器 (ADC),同时保持卓越的噪声和失真性能的能力。为交流和直流耦合应用显示了连接到 ADS4449 四通

2015-05-11 10:33:40

描述TIDA-01016 是一款适合高动态范围高速 ADC 的时钟解决方案。射频输入信号由高速 ADC 直接采用射频取样法捕获。ADC32RF80 是一款双通道 14 位 3GSPS 射频取样

2018-09-30 09:26:09

哪些参数会影响SNR?哪种评估SNR最好?以上来自于谷歌翻译以下为原文 Which are the parameters that impact on SNR? Which is the best way to evaluate the SNR?

2018-09-28 16:47:28

时钟抖动,这是ADC采样频率较高时常见的SNR降级原因之一。高速,高分辨率ADC对时钟输入的质量非常敏感。要在高速ADC中实现卓越的SNR,必须根据应用输入频率的要求仔细考虑均方根(rms)时钟抖动

2018-11-01 11:33:13

引言要获得 ADC 的最佳 SNR 性能并不仅仅是给 ADC 输入提供低噪声信号,提供一个低噪声基准电压是同等重要。虽然基准噪声在零标度没有影响,但是在全标度,基准上的任何噪声在输出代码中都将是可见

2019-07-25 07:15:15

如何推导ADC的SNR?如何准确地估算某个时钟源的抖动?如何将其与ADC的孔径抖动组合?

2021-05-13 06:17:20

高信噪比=低ADC孔径抖动吗?在设计中,为了避免降低ADC的性能,工程师一般会采用抖动极低的采样时钟。然而,用于产生采样时钟的振荡器常常用相位噪声而非时间抖动来描述特性。那么,有木有方法将振荡器相位噪声转换为时间抖动呢?

2019-08-13 06:27:54

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。那么时钟抖动会对高速ADC的性能有什么影响呢?

2021-04-08 06:00:04

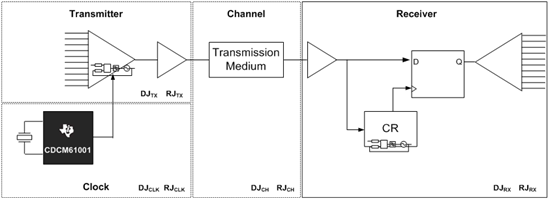

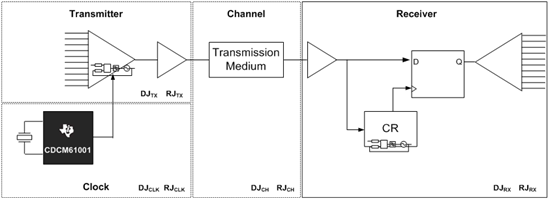

作者:John Johnson,德州仪器 本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成

2018-09-19 14:23:47

本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。 用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成了各种委员会和标准机构,根据其开发标准的目标

2022-11-23 06:59:24

的时钟源之问题。——Guy Hoover通常,它需要一个可具有高达 1nsRMS 抖动的函数发生器。常常需要采用一个高质量的 RF 发生器或晶体振荡器以从 16 或 18 位 ADC 获得最佳的 SNR

2018-07-19 16:23:22

是量化有用信号,产生量化噪声的,对于1bitADC,产生7.78db的SNR本地噪声是白噪声,量化后还是白噪声,所以幅值等完全不变这样,只要对于本地噪声比信号还大的场合,无论用什么ADC都可以,都不会劣化SNR类似的,时钟抖动等均毫无影响 请问这种推论到底哪里有问题?错在哪?

2018-08-19 06:31:10

读写24C02的时候为什么一直有IIC_Wait_Ack();ACK应答是自动产生的吗?

2020-05-29 10:13:54

` 本帖最后由 web_master 于 2013-9-26 14:19 编辑

运算放大器经典问题解析——设计运放电路必备常识![hide] [/hide]`

2013-09-26 11:48:56

的。整个抖动转移带宽由低带宽环路控制,典型情况下采用电压控制晶体振荡器(VCXO)。当CDR是系统中唯一的时钟发生单元时,抖动转移带宽与抖动容差必须符合ITU-T规范。抖动产生是另一个重要的参数。抖动产生

2014-12-09 14:36:58

包含千兆采样率ADC的系统设计会遇到许多复杂情况。面临的主要挑战包括时钟驱动、模拟输入级和高速数字接口。本文探讨了如何才能克服这些挑战,并给出了在千兆赫兹的速度下进行系统优化的方法。在讨论中,时钟

2019-05-30 05:00:04

电子设计竞赛赛题解析

东西是非常不错的,可供参考.

2016-12-17 12:43:15 0

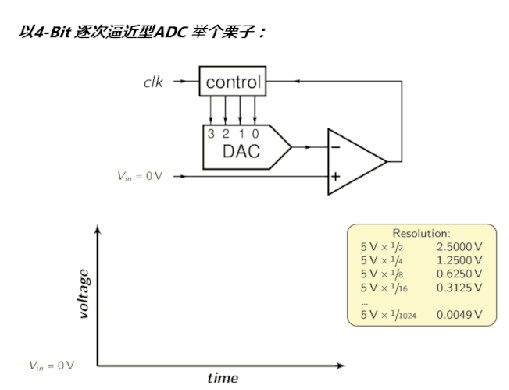

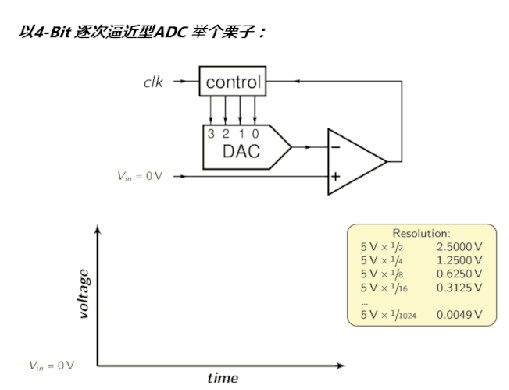

0 解析逐次逼近ADC

2009-05-04 13:29:41 24

24 本文研究了直扩超宽带通信系统的关键技术----定时抖动及其抑制方法,主要分析了定时抖动产生的原因、分布规律和各种有效的抑制方法。文中第一次对DS-UWB 系统定时抖动产生的各

2009-08-10 14:24:07 15

15 极高速ADC(>1 GSPS)需要一种低抖动的采样时钟,以保持信噪比(SNR)。这些8比特和10比特转换器具有由量化噪声设置的最佳情形的噪声基底。对满量程正弦波进行采样的N比特ADC,SNR的

2009-09-30 10:04:05 20

20 介绍了一种用于高速ADC 的低抖动时钟稳定电路。这个电路由延迟锁相环(DLL)来实现。这个DLL 有两个功能:一是通过把一个时钟沿固定精确延迟半个周期,再与另一个沿组成一个新

2009-11-26 15:55:15 28

28 本文主要讨论采样时钟抖动对ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

2009-11-27 11:24:07 15

15 高速互联链路中参考时钟的抖动分析与测量

在高速互联链路中,发送器的参考工作时钟的抖动是影响整个

2010-04-15 14:01:39 19

19 高速ADC供电指南

为使高速模数转换器发挥最高性能,必须为其提供干净的直流电源。高噪声电源会导致信噪比(SNR)下降和/或ADC输出中出现不良的杂散成分。本文将介绍有关ADC

2011-01-01 12:18:09 94

94 按钮式数字电位器的防抖动和重复动作问题解决方法

介绍按钮式数字电位器的防抖动和重复动作问题的一种解决方法,以及对数字电位器电压、电流、级

2009-04-05 09:26:26 2871

2871

车台天线的位置和辐射问题解析

1、车台外接的天线,放在后备箱上比放在车顶中间的效果是不是差一些?

回答:车台的天线共有四

2010-01-04 09:44:48 3186

3186 凌力尔特推出16位ADC,可实现实现卓越的SNR

不久前,凌力尔特公司(Linear)推出 16 位 SAR ADC LTC2393-16,该器件以高达 1Msps 的采样率实现卓越的 94dB SNR,而且无周期延迟。LTC

2010-01-18 08:35:51 946

946 高速ADC,什么是高速ADC

背景知识:

随着计算机技术、通信技术和微电子技术的高速发展,大大促进了ADC技术的发展,ADC作为模拟量与数据量接

2010-03-24 13:28:01 9741

9741 16位、1Msps SAR ADC实现94dB SNR、可测量±4.096V的宽输入范围

加利福尼亚州米尔皮塔斯 (MILPITAS, CA) – 2010 年 1 月 14 日 – 凌力尔特公司(Line

2010-12-26 15:40:19 1431

1431 您在使用一个高速模数转换器 (ADC) 时,总是期望性能能够达到产品说明书载明的信噪比 (SNR) 值,这是很正常的事情。您在测试 ADC 的 SNR 时,您可能会连接一个低抖动时钟器件到

2011-01-05 10:44:48 1284

1284 为实现高信噪比(SNR),ADC的孔径抖动必须很低(参见参考文献1、2和3)。目前可提供孔径抖动低至60 fs rms的ADC(AD9445 14位125 MSPS和AD9446 16位100 MSPS)。为了避免降低ADC的性能,必须采用抖动极低

2011-11-17 15:10:53 28

28 苏泊尔微电脑电磁炉故障问题解析,本内容介绍了苏泊尔电磁炉故障问题的分析

2012-05-11 15:14:47 6390

6390

SNR boost是一种噪声成型技术,该技术能够改变量化噪声的频谱

2013-03-14 16:02:01 17

17 自动控制原理习题解析,有需要的下来看看。

2016-05-05 14:06:42 0

0 风力摆控制系统赛题解析

2016-12-09 23:00:44 31

31 了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。 在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能

2017-05-15 15:20:59 13

13 新型的高速ADC 都具备高模拟输入带宽(约为最大采样频率的3 到6 倍),因此它们可以用于许多欠采样应用中。ADC 设计的最新进展极大地扩展了可用输入范围,这样系统设计人员便可以去掉至少一个中间频率

2017-05-18 09:47:38 1

1 时钟产生抖动(jitter)会使发生抖动的时钟信号与未发生抖动的时钟信号在时域上存在偏差,从而使模数转换器的采样频率发生紊乱,最终导致模数转换器采样的不稳定性,使输出信号存在频谱毛刺,导致误码率上升

2017-11-11 18:22:26 9

9 本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。 ADC 是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定

2017-11-27 14:59:20 17

17 本文继续进行时钟抖动的分析,阐明了如何通过改善ADC的孔径抖动来提高ADC的SNR。

2018-05-08 17:48:41 7

7 《高等学校优秀教材?电工学知识要点与习题解析》为配合秦曾煌教授主编的《电工学》(第六版)而编写的辅导书。《电工学知识要点与习题解析/高等学校优秀教材辅导丛书》主要包括知识要点、书后思考题解答、书后

2020-01-10 11:48:10 56

56 ADC 的 SNR:SNR(signal noise ratio)是指信噪比,受许多因素影响,包括分辨率,线性度和准确性(量化级别与真实模拟信号的匹配程度),混叠和抖动。ADC 的 SNR 通常

2020-08-13 17:25:09 2157

2157

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。借助本文,我们将使读者更好地理解时钟抖动问题及其对高速ADC性能的影响。

2020-08-20 14:25:16 791

791

作为基线,DC1826A-A 的时钟输入采用一个罗德与施瓦茨 SMB100A RF 发生器来驱动,并由 Stanford Research SR1 提供模拟输入。结果是图 1 中的 PScope 数据,其产生一个 98.247dBFS SNR。

2021-01-04 15:44:49 2667

2667

AN-1221: 使用ADF4002 PLL产生高速模数转换器所需的极低抖动编码(采样)时钟

2021-03-19 08:59:00 13

13 16 位、1Msps SAR ADC 实现 94dB SNR、可测量 ±4.096V 的宽输入范围

2021-03-20 17:46:23 0

0 MT-200:降低ADC时钟接口抖动

2021-03-21 01:18:30 7

7 DN568 - 基准滤波器使 32 位 ADC SNR 增加 6dB

2021-03-21 12:27:12 13

13 前言 :本文我们介绍下ADC采样时钟的抖动(Jitter)参数对ADC采样的影响,主要介绍以下内容: 时钟抖动的构成 时钟抖动对ADC SNR的影响 如何计算时钟抖动 如何优化时钟抖动 1.采样理论

2021-04-07 16:43:45 7378

7378

自适应抖动缓冲器-下载产生码

2021-04-12 16:47:30 3

3 LTC2391-16:16位、250ksps SAR ADC,带94dB SNR数据表

2021-04-17 09:25:40 2

2 LTC2373-18:18位、1Msps、8通道SAR ADC,带100dB SNR数据表

2021-04-18 12:52:57 6

6 超低抖动时钟的产生与分配

2021-04-18 14:13:51 8

8 LTC2378-16:16位、1 Msps、低功耗SAR ADC,带97dB SNR数据表

2021-04-23 16:18:36 7

7 ADC时钟接口中的最小抖动

2021-05-09 12:19:40 6

6 DN1013-了解时钟抖动对高速ADC的影响

2021-05-11 18:22:19 0

0 LTC2392-16:16位、500ksps SAR ADC,带94dB SNR数据表

2021-05-17 14:00:52 3

3 自适应抖动缓冲器-下载产生码

2021-06-16 11:08:38 4

4 电工学-知识要点与习题解析电子版

2021-07-23 09:33:51 0

0 樊昌信《通信原理》真题解析及讲义电子版

2021-09-06 14:40:47 0

0

图 1 显示了集成有一个嵌入式时钟的典型高速通信链路。每个子系统(时钟、发送器、通道和接收机)都会对整体抖动预算的增加产生影响。子系统抖动包括一个决定性 (DJ) 组件和一个随机组件 (RJ),如图

2021-11-22 15:52:21 1284

1284

《电路考研精要与典型题解析》陈燕主编

2022-01-14 15:33:40 0

0 《信号与系统 第3版》习题解析

2022-03-21 15:06:19 0

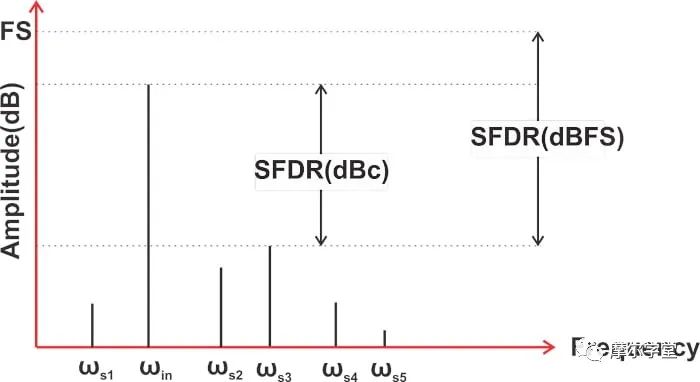

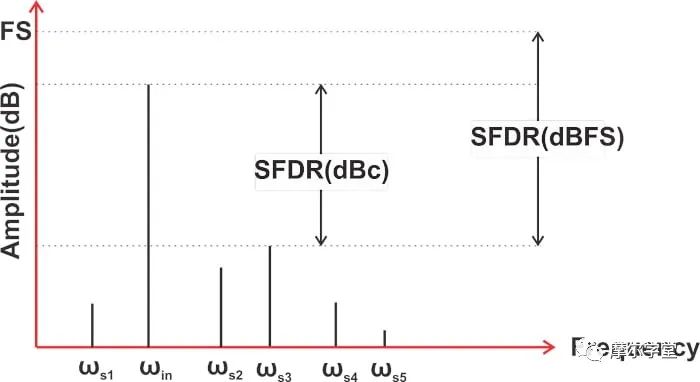

0 时钟抖动、采样率和量化噪声是影响 ADC 中 SNR 和 SFDR 的最关键因素

2022-08-11 14:26:08 2684

2684

本文件的目的是介绍与高速模数转换器(ADC)。本文件详细介绍了抽样理论,数据表规格、ADC选择标准和评估方法、时钟抖动等常见问题系统级问题。此外,一些最终用户希望扩展通过实现交织、平均或抖动技术实现ADC。的好处和关注点本文讨论了交织、平均和抖动ADC

2022-09-20 14:23:49 3

3 时钟抖动解秘—高速链路时钟抖动规范基础知识

2022-11-07 08:07:30 1

1 源,即采样保持 (S/H) 电路和 ADC 的编码器部分。

我们还将了解 ADC 中 SFDR 和SNR(信噪比)之间的一般权衡,并为以后有关应用抖动技术改善 ADC SFDR 的有趣讨论奠定

2023-05-11 15:22:25 892

892

比亚迪汉EV高速行驶抖动故障现象故障诊断故障排除一辆比亚迪汉EV,车主反馈车辆在120km/h高速行驶中有抖动现象。故障现象故障诊断故障排除原因分析1、车轮不平衡2、传动半轴不平衡3、轮毂法兰

2023-03-03 11:30:57 2009

2009

电子发烧友网站提供《时钟抖动对ADC性能有什么影响.pdf》资料免费下载

2023-11-28 10:24:10 1

1

电子发烧友App

电子发烧友App

评论