本电路的AD1674工作在完全受控方式。A/D转换为12位,而转换后数据分两次读取,即先读数据的高八位,后读数据的低四位。

1.3.1 A/D转换的启动方式

A/D转换的启动方式有两种:8253定时器硬件启动和写端口软件启动。

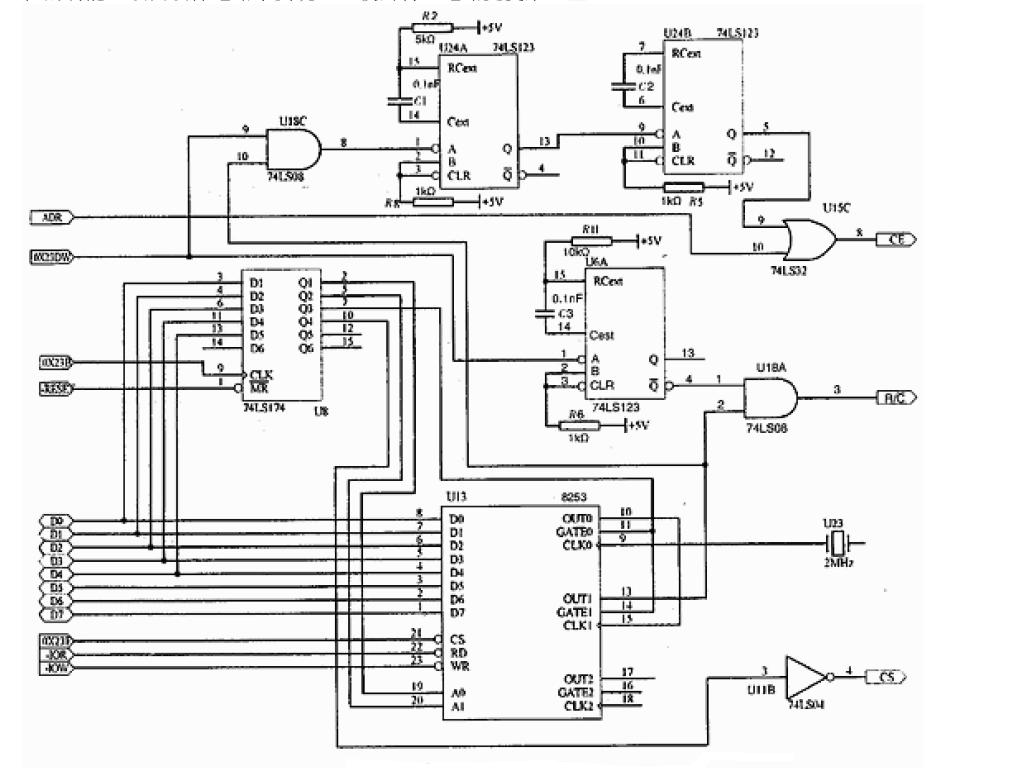

8253定时器启动方式应用于对数据采集的时隔要求准确的场合,该方式是利用8253的定时脉冲启动A/D转换,通过8253数据总线缓冲器(端口地址为&0X23F)输出鉴别通道的计数初值,通过向6位锁存器74LS174(端口地址为&0X23B)写入控制字设定8253的控制字以及A/D片选控制位。6位锁存器数据位定义说明如下:

A1A0=00:&0X23D口输出的数据为计数器0的计数值。

A1A0=01:&0X23F口输出的数据为计数器1的计数值。

A1A0=10:&0X23F口输出的数据为计数器2的计数值。

A1A0=11:&0X23F口输出的数据为计数器8253的方式字。

G0&G1=1:起动计数器0和计数器1;G0&G=0:禁止计数器0和计数器1。

CS=1:选中A/D芯片CS=0;不选中A/D芯片。

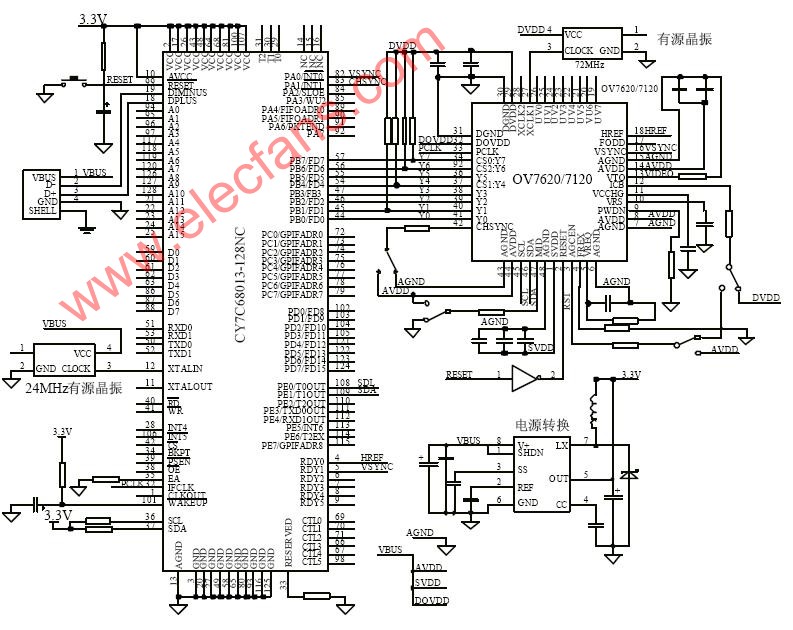

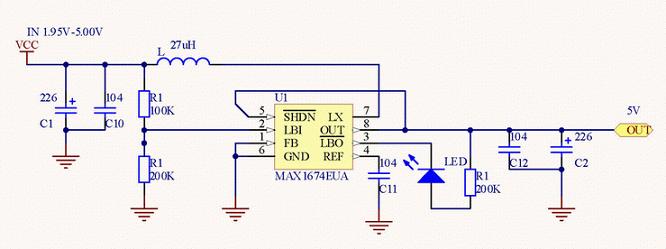

具体的实现电路如图2所示。首先将8253定时通道0与通道1串联起来定时,通道0的时钟输入CLK0的频率是2MHz,工作在方式3(方波比率发生器)下,通道0的输出OUT0为频率1MHz的方波,作为通道1的输入时钟CLK1。通道1设定为方式2,即通道1的输出OUT1从输出开始一直维持高电平,计数回零后,输出为低电平并自动重新装入原计数值,低电平维持一个时钟周期后,输出恢复高电平并重新作减法计数。输出OUT1分为两路信号,一路通过与门U18A输出,作为AD1674的R/C控制信号;另一路经过单稳触发器U24延时和调节定时宽度后,再通过或门U15C输出作为AD1674的CE控制信号。当OUT1输出宽度为1μs的低电平脉冲时,一方面使控制信号R/C的转换有效,同时经延时和调节定时宽度后,使A/D的使能控制CE开始启动A/D转换。因此在装入计数初值以后,只要设置6位锁存器U8的控制字,就可利用8253定时器启动A/D。

写启动A/D方式应用于软件定时,即通过对端口(地址为&0X23D)写来触发A/D转换。如图2所示,端口写信号一方面经过单稳触发器U6A调节定时宽度(宽度为1μs)后,作为AD1674的R/C控制信号,同时经过另一单稳触发器U24延时和调节定时宽度后,再通过或门U15C输出作为AD1674的CE控制信号。

可见两种启动A/D转换的过程相似。相比较而言,前者的采样间隔是由8253定时脉冲的周期决定的,属于可编程定时器方式定时,共特点是采样间隔准确;后者则由相邻两次写端口(地址为&0X23D)的时间差决定采样间隔,为软件定时方式,特点是灵活方便。

1.3.2 A/D转换数据的读取方式

在数据采集系统中,计算机读取A/D转换数据的方式一般有三种,即查询、中断和DMA方式。其中查询方式就是通过查询标志位来判断A/D是否转换完毕,如果A/D转换完毕则读入转换的数据。这种方式下CPU主动查询,通过CPU读取A/D转换的数据,故实现的硬件电路简单,但数据读取速度慢,同时在WINDOWS的多任务执行方式下,存在着A/D转换数据不能及时读入的问题。中断方式是利用A/D转换完毕的标志位触发一硬中断,然后中断管理器向CPU提出中断申请。在中断允许的情况下,执行中断服务程序读入转换的数据。这种方式实现的硬件电路也比较简单,但中断服务程序的介入,引起数据采集程序的断点的不可预测性,这样会导致数据采集程序的失控。DMA方式利用A/D转换完毕的标志位向DMA控制器提出DMA申请,当DMA控制器从CPU取得总线控制权时,接口便与内存之间直接地进行数据交换(不经过CPU)。这种方式下,由于不经过CPU读入数据,故提高了数据传输速度。同时由于A/D转换器主动申请数据传输,而DMA申请比外设中断申请的优先级高,A/D转换数据能够及时读入,系统性能也得到了提高,但实现的硬件电路较前两种方式复杂。

本电路设计有查询、中断和DMA三种数据传输方式。通过一拨码盘开关来选择不同的的传输方式。如图3所示,当A/D转换完毕时,标志位STS由高电平变为低是电平,从而引起D触发器U20A触发,U20A的输出Q由低电平变成高电平。当拨码盘开关S1选择为查询方式时,该U20A的输出Q通过一个三态门(端口地址为&0X23F)与数据线D6相连,提供计算机查询;在中断方式下,该U20A的输出Q直接与硬中断引脚IRQ2相连,当Q由低电平变成高电平时,引起计算机中断。在前两种方式下,通过软件编程,向一锁存器U22的最低位写入0或1,选择读取A/D转换数据的高八位或低四位,且由专门的端口(地址为&0X23D)读取A/D转换的数据。实现的硬件电路简单。而在DMA方式下,通过应答信号DACK1寻址,并不由专门的端口读取A/D转换的数据,故选择A/D转换数据的高八位或低四位的功能必须由硬件电路来实现,比较而言,电路更复杂一些。

下面介绍DMA方式下的具体实现电路。DMA请求电路由两个D触发器组成,当A/D转换完毕时,U20A的输出Q由低电平变成高电平,DRQ1=1,DMA通道1发出请求,DRQ1被认可后进行两次DMA传输。在第一次DMA传输期间,触发器U20B的输出Q为低电平,A/D转换数据的高八位传输到指定内存单元。在第一次DMA传输结束时,DACK1由低电平变成高电平,触发器U20B的输出为高电平,但触发器U20A的输出Q仍然是高电平,该电平申请第二次DMA传输。在第二次DMA传输期间,触发器U20B的输出为高电平,A/D转换数据的低四位传输到指定的内存单元。当第二次DMA传输结束时,DACK1由低电平变成高电平,使触发U20B输出低电平,同时触发器U20A的输出Q变为低电平,DRQ1=0变为低电平,DRQ1=0,DMA通道1的请求被撤销,结束一次A/D转换12位数据传输过程。

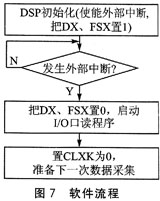

2 软件设计

该接口电路支持各种带有口指令操作的高级语言和8086/8088汇编语言。以下就以Turbo C为例对相应的部分编程,经供参考。

2.1 A/D编程

该编程适合于中断或查询方式下的编程,端口地址=0x238~0x23f。

outportb(0x23c,0x00); /*初始化清零*/

outportb(0x23a,0x00); /*选择传输高8位数据并为A/D转换作准备*/

{

}; /*启动A/D并检查A/D是否转换完毕*/

dh=inportb(0x23d); /*输入高八位数据*/

outporth(0x23a,0x01); /*选择传输低四位数据*/

dl=inportb(0x23d); /*输入低四位数据*/

outportb(0x23a,0x00); /*选择传输高8位数据并为A/D转换作准备*/

dl=dl>>4;

dh1=dh;

dl=(dh1<<4)+dl;

dh=dh>>4; /*将高八位低四位数据转化为高四位低八位数据*/

d=dh*256+dl; /*拼合12位数据*/

u=(d-2047)*10.0/4096; /*转换电压值*/

2.2 写启动和查询方式的编程

outportb(0x23d,0x00); /*写启动A/D转换*/

if(inporth(0x23e)&0x80);/*D7=1则A/D转换完毕*/

电子发烧友App

电子发烧友App

评论