8(八)路触发锁存电路

- 锁存(20516)

相关推荐

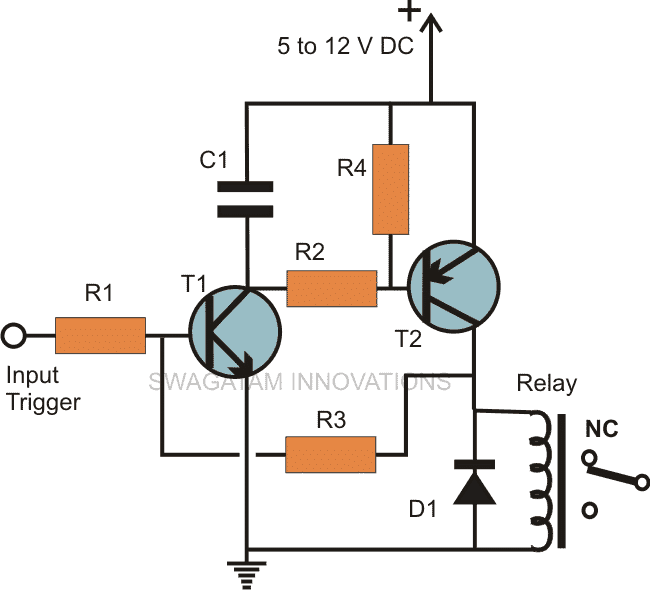

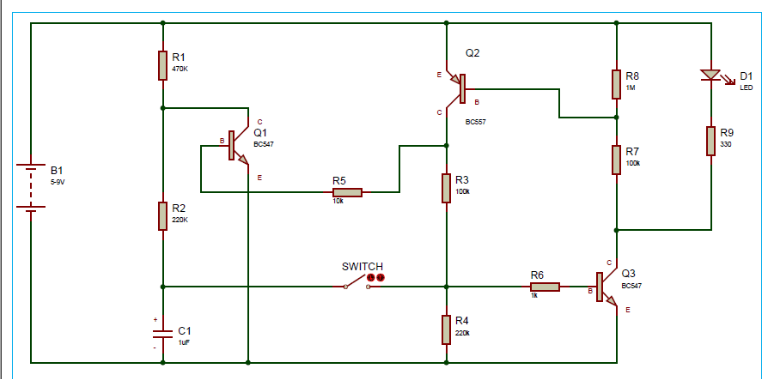

基于晶体管的迷你锁存电路

如图所示的迷你锁存电路使用几个晶体管,在需要锁存继电器以响应瞬时触发的应用中非常有用。在这里,当在输入端施加瞬时正触发时,晶体管与继电器一起补充和传导。同时,反馈电压通过R3到达T1的基极,即使在

2023-06-10 17:50:00 1137

1137

1137

1137

FPGA学习之触发器和锁存器

锁存器是构成各种时序电路的基本元件,它的特点是具有0和1两种稳定的状态,一旦状态被确定,就能自行保持,即长期存储1位的二进制码,直到有外部信号作用时才有可能改变。锁存器是一种对电平敏感的存储单元电路,它们可以在特定输入电平作用下改变状态。

2023-03-23 16:03:32 658

658

658

658

锁存器和触发器的定义和比较

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态,当Gate输入为高电平时,输入D透明传输到输出Q;当Gate从高变低或者保持低电平时,输出Q被锁存保持不变。锁存器是电平触发的存储器。

2023-03-23 14:48:54 1357

1357

1357

1357

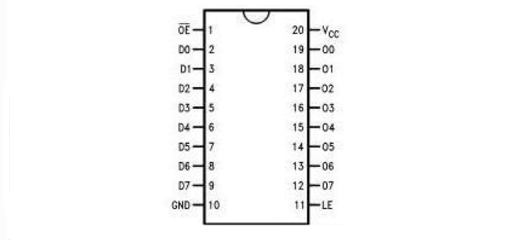

具有 5 V 容限输入/输出的八路D型透明锁存器;三态-74LVC573A_Q100

具有 5 V 容限输入/输出的八路 D 型透明锁存器;三态-74LVC573A_Q100

2023-02-20 19:09:38 0

0

0

0具有 5 V 容限输入的八路D型透明锁存器 / 输出;三态-74LVC373A_Q100

具有 5 V 容限输入的八路 D 型透明锁存器 / 输出;三态-74LVC373A_Q100

2023-02-16 21:11:37 0

0

0

0具有 5 V 容限输入的八路D型透明锁存器 / 输出;3-状态-74LVC573A

具有 5 V 容限输入的八路 D 型透明锁存器 / 输出;3 - 状态-74LVC573A

2023-02-15 19:47:18 0

0

0

0具有 5 V 容限输入的八路D型透明锁存器 / 输出;三态-74LVC373A

具有 5 V 容限输入的八路 D 型透明锁存器 / 输出;三态-74LVC373A

2023-02-15 19:46:22 0

0

0

0关于FPGA中锁存器的生成:if语句和case语句的完整性影响

锁存器(Latch)是数字逻辑电路中很重要的一种基本电路,常见的锁存器包括三个端口:数据输入口、数据输出口、使能端。当使能端为高电平时,输入口的数据直接送到输出口,此时输入输出口可以看成是直接

2023-02-09 21:05:05 597

597

597

597Verilog中 锁存器/触发器/寄存器的区别

锁存器(latch):是电平触发的存储单元,数据存储的动作(状态转换)取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2023-01-31 14:57:40 1186

1186

1186

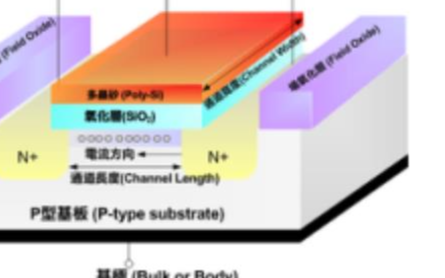

1186解读从CMOS到触发器 锁存器常见结构与锁存器应用

主要内容: ·双稳态器件 ·锁存器常见结构 ·锁存器的应用 ·触发器 ·触发器的建立时间和保持时间 1、双稳态器件 ** 双稳态器件**是指稳定状态有两种,一种是0,一种是1的器件;双稳态器件

2023-01-28 09:28:00 2426

2426

2426

2426

锁存器、触发器、寄存器的关联与区别及其相应的verilog描述

1:锁存器、触发器、寄存器的关联与区别 首先应该明确锁存器和触发器是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合逻辑电路的特性。 锁存

2022-12-19 12:25:01 3721

3721

3721

3721锁存器的主要特性、种类及应用

锁存器是具有两个稳定状态的时序逻辑电路,即它是双稳态多谐振荡器。锁存器有一个反馈路径来保留信息。因此,锁存器可以是存储设备。只要设备处于开机状态,锁存器就可以存储一位信息。当使能启用时,锁存器会在输入更改时立即更改存储的信息,即它们是电平触发设备。当使能信号打开时,它会持续对输入进行采样。

2022-09-12 16:13:00 6069

6069

6069

6069

如何制作一个软锁存电路

电路中,电路只能被锁存到一种状态,并且可以改变需要移除电源的状态。通常移位寄存器和触发器用于锁存电路,就像我们在Clap-on-Clap-off 电路中使用的一样。

2022-08-25 16:32:47 2778

2778

2778

2778

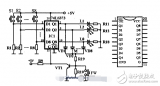

八路抢答器设计论文

电子电路朝数字化、集成化方向发展,因此设计出数字化全集成电路的多路抢答器是现代电子技术发展的要求0 笔者按照这一要求,并根据74LS373八路锁存器的功能特点,用74LS373和其它几块常用的)#12 系列

2008-12-01 21:13:16

AiP74LVC573带三态控制的8路D型锁存器

AiP74LVC573由8个D型锁存器组成,每个锁存器具有独立的D型输入以及面向总线应用的三态输出。所有内部锁存器共用一个锁存使能(LE)输入和一个输出使能(OE)输入。 当LE为高电平时,Dn输入

2022-02-21 15:46:10 5

5

5

5锁存器详解

P0口作为分时复用接口,既要作为数据总线口,又要作为地址总线口 输出的低8位地址需要用8位锁存器锁存 ALE的下降沿将P0口输出的低8位地址锁存• 对于锁存器: ○ /OE为输出使能端 § /OE

2021-11-26 20:51:04 11

11

11

118位CPU设计(1) 门电路和锁存器、触发器

这是一个系列文章,从最简单的门电路介绍,从基础的锁存器、触发器、编码器、译码器等一系列数字逻辑电路开始,最终构造一个简易版的CPU实物

2021-11-06 09:20:58 16

16

16

16锁存器与寄存器有哪些区别

首先应该明确锁存器和触发器也是由与非门之类的东西构成。尤其是锁存器,虽说数字电路定义含有锁存器或触发器的电路叫时序电路,但锁存器有很多组合电路的特性。 组合电路就是一个真值表,一个函数,一组输入对应

2021-08-12 10:26:12 3567

3567

3567

3567锁存器与触发器的区别

作者:电子工程师小李 1)锁存器 锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。 简单地说

2020-11-29 11:02:11 20662

20662

20662

20662FPGA的设计中为什么避免使用锁存器

文章都对锁存器有个误解,我们后面会详细说明。 这篇文章,我们包含如下内容: ①锁存器、触发器和寄存器的原理和区别,为什么锁存器不好? ② 什么样的代码会产生锁存器? ③ 为什么锁存器依然存在于FPGA中? 锁存器、触发器和寄存器的原理和区别,为什么锁存器

2020-11-16 11:42:00 7206

7206

7206

7206

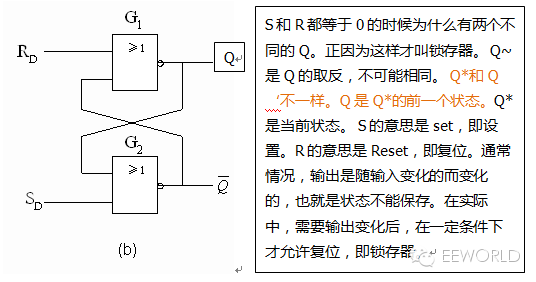

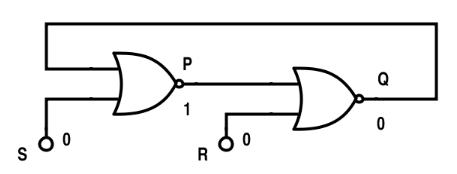

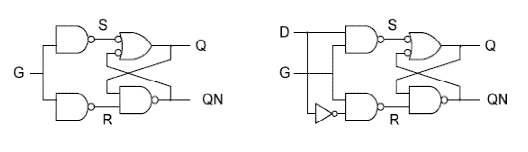

RS锁存器和D锁存器的电路结构及工作原理

一、SR锁存器 1、RS锁存器的电路结构及工作原理 RS锁存器是一两输入、两输出的电路,其电路如图1(a),其有两个互相交叉反馈相连的两个与非门构成,其两个输出为两个相反的输出(或称为互补输出),图

2020-10-07 15:24:00 42935

42935

42935

42935

如何操作基本类型的锁存器和触发器

锁存器(有时也称为S/R锁存器)是最小的存储器块。它们可以使用两个NOR逻辑门(S和R为高电平有效)或两个NAND门(输入为低电平有效)构建,并用于构建更复杂的锁存器和触发器。

2019-07-30 11:23:28 5658

5658

5658

5658

D型触发器电路真值表和计数器数的据锁存器摘要

D型触发器是一个改进的置位复位触发器,增加了一个反相器,由此可见以防止S和R输入处于相同的逻辑电平,此状态将强制两个输出都处于逻辑“1”,超越反馈锁存动作,无论哪个输入先进入逻辑电平“1”都将失去控制,而另一个仍处于逻辑“0”的输入控制锁存器的结果状态。

2019-06-26 15:36:28 14537

14537

14537

14537

基于CD4511进行八路抢答器电路的设计资料说明

CD4511是一片CMOSBCD—锁存/7段译码/驱动器,用于驱动共阴极LED(数码管)显示器的BCD码-七段码译码器。具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。可直接驱动共阴LED数码管。下面将介绍基于CD4511的八路抢答器电路的设计。

2019-01-08 08:00:00 61

61

61

61锁存器Latch和触发器Flip-flop有何区别

本文首先介绍了锁存器Latch结构和锁存器latch的优缺点,其次介绍了触发器Flip-flop的结构与优缺点,最后介绍了锁存器Latch和触发器Flip-flop两者之间的区别。

2018-04-18 14:10:10 128942

128942

128942

128942

锁存器、触发器、寄存器和缓冲器的区别

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2018-03-26 10:57:46 15588

15588

15588

15588d锁存器与sr锁存器的区别

锁存器就是把单片机的输出的数据先存起来,可以让单片机继续做其它事。它的LE为高的时候,数据就可以通过它。当为低时,它的输出端就会被锁定RS触发器是构成其它各种功能触发器的基本组成部分。又称为基本RS触发器。

2018-01-31 14:48:13 28618

28618

28618

28618

锁存器使用总结

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题

2018-01-31 13:57:22 11284

11284

11284

11284

基于8D锁存器74LS373的抢答器设计电路

利用74LS373设计的抢答器电路它由一片8D锁存器74LS373。8只组别按键开关S1-S8,8组别抢答有效的状态显示发光二极管L1-L8,一个复位按键FW等组成。该8路竞赛抢答器,每组受控于一个抢答按键开关,高电平表示抢答有效。

2017-12-05 10:28:25 10605

10605

10605

10605

基于cd4511的八路抢答器电路

电流。可直接驱动共阴LED数码管。下面将介绍基于CD4511的八路抢答器电路的设计。 电路功能 1、抢答器同时供8名选手或8个代表队比赛,分别用8个按钮S1~S8表示。 2、设置一个系统清除和抢答控制开关S,该开关由主持人控制。 3、抢答器具有锁存与显示功能。即选手按动按钮,锁

2017-11-23 09:08:38 65371

65371

65371

65371锁存器和触发器的区别

锁存器(latch)---对脉冲电平敏感,在时钟脉冲的电平作用下改变状态 锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

2017-11-02 09:24:41 92855

92855

92855

92855

锁存器的主要作用有哪些?

所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。典型的锁存器逻辑电路是 D 触发器电路。 PS:锁存信号(即对LE赋高电平时Data端的输入信号)。锁存,就是把信号暂存以维持某种电平状态。

2017-10-30 14:35:53 58733

58733

58733

58733

使用简易锁存电路保护电源

您曾经是否需要过一款简单、低成本的锁存电路?您可以通过选择电阻器值建立 SCR 的保持电流。为了让锁存电路在触发以后仍然保持开启,两个基极发射极结点必须要有足够的电压(~0.

2011-11-24 11:20:40 1123

1123

1123

1123

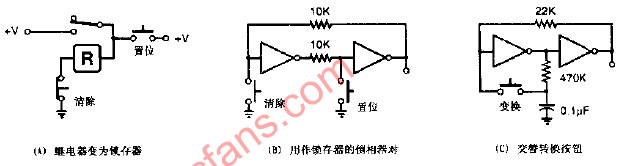

锁存继电器的CMOS电路研究

瞬动开关提供驱动电路的步进电压信号。电路使用一个简单的下拉开关动作,如由RS、CS和S2构成,或一个触发器的锁存动作,如由IC1A、IC1B、R1、R2、C1和S1构成。

2011-07-27 15:31:27 1729

1729

1729

1729

锁存器和触发器原理

1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 233

233

233

233地址锁存器,地址锁存器是什么意思

地址锁存器,地址锁存器是什么意思

地址锁存器就是一个暂存器,它根据控制信号的状态,将总线上地址代码暂存起来。8086/8088数

2010-03-09 09:49:49 4547

4547

4547

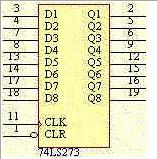

4547地址锁存器--74LS273

地址锁存器--74LS273

74LS273是带清除端的八D触发器,只有清除端为高电平时才具有锁存功能,锁存控制端为11脚CLK,在上升沿锁存。单片机的ALE端输出的锁存控制信号必须经反

2009-03-14 15:37:57 4529

4529

4529

4529

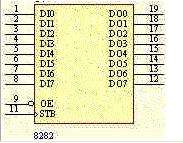

地址锁存器--8282

地址锁存器--8282

8282是带有三态门的八D锁存器,当使能信号线OE为低电平时,三态门处于导通状态,允许1Q-8Q输出到OUT1-OUT8,当OE端为高电平时,输出三态门断开,输出线OUT1-O

2009-03-14 15:37:24 8894

8894

8894

8894

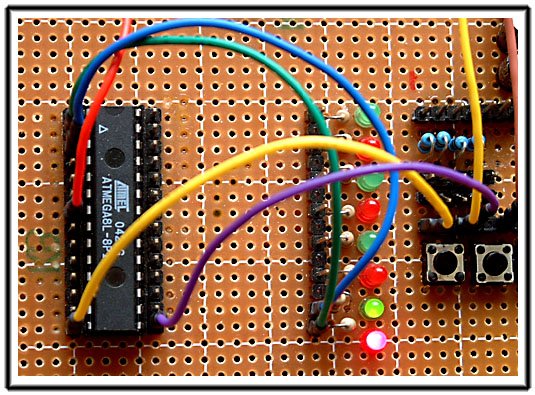

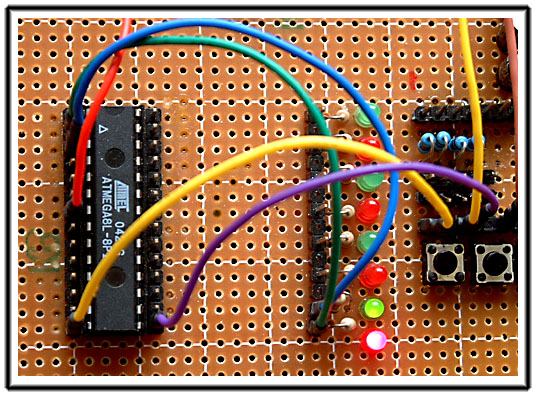

用Atmega8实现8路键盘D触发锁存器功能(含源程序代码)

用Atmega8实现8路键盘D触发锁存器功能(含源程序代码)

实现目的:

当管脚设定为输入时,了解如何可以编程设

2008-11-01 09:42:22 1490

1490

1490

1490 电子发烧友App

电子发烧友App

评论