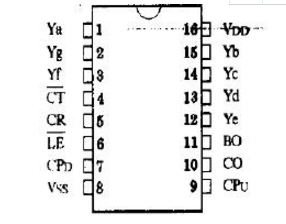

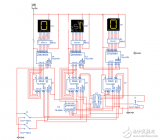

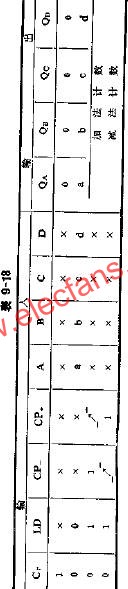

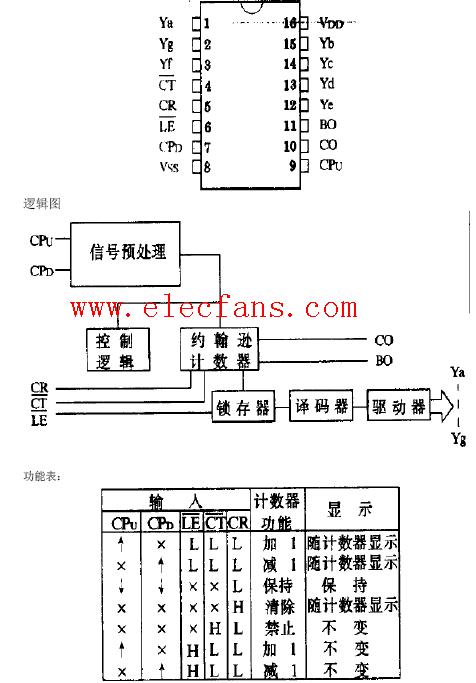

可逆计数器的应用

电子发烧友App

电子发烧友App

硬声App

硬声App

完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网>电子技术应用>电子技术>电路图>信号处理电子电路图>可逆计数器的应用

相关推荐

444

444

2392

2392

0

0 32

32 38241

38241

30

30 3

3 6455

6455

6

6 13507

13507

11606

11606

96385

96385

18394

18394 7718

7718

18

18 2832

2832

22

22 8

8 244

244 2438

2438

814

814

811

811

1197

1197

76

76 4593

4593

604

604 542

542 489

489 40145

40145

417

417

评论