74LS160构成的100进制同步加法计数器

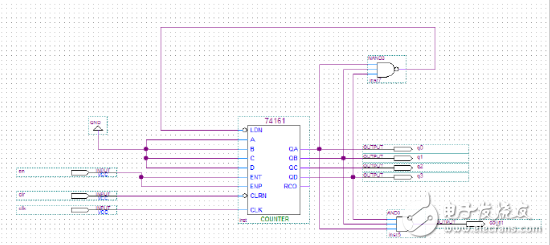

由图可看出:低位片CT74LS160(1)在计到9以前,其进位输出CO=Q3Q0=0,高位片CT74LS160(2)的CTT=0,保持原状态不变。当低位片计到9时,其输出CO=1,即高位片的CTT=1,这时,高位片才能接收CP端输入的计数脉冲。所以,输入第10个计数脉冲时,低位片回到0状态,同时使高位片加1。

74LS160构成的100进制同步加法计数器

- 计数器(91962)

- 74ls160(18607)

相关推荐

74ls160构成24进制计数器

本文主要介绍了74ls160构成24进制计数器电路设计。本设计采用异步清零。由两片十进制同步加法计数器74LS160和一片与非门74LS00以及相应的电阻开关组成。由外加送来的计数脉冲送入两个计数器

2018-01-18 15:43:05 145644

145644

145644

145644

74ls160设计60进制计数器

计数器是一个用以实现计数功能的时序部件,本设计主要设备是两个74LS160同步十进制计数器,并且由200HZ,5V电源供给。作高位芯片与作低芯片位之间级联。

2017-12-21 17:23:51 224996

224996

224996

224996

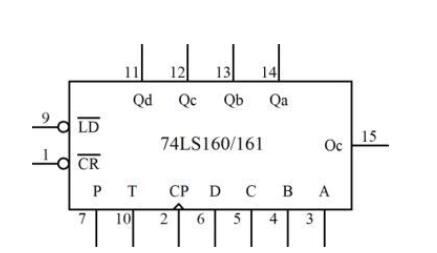

74ls160和74ls161区别

本文主要介绍了74ls160和74ls161区别。74ls161为四位二进制,74ls160 为2-10进制;且都为同步可预置计数器。74ls161 是4位二进制同步计数器(直接清除),74ls160 是4位十进制同步计数器(直接清除)。

2018-05-08 10:23:35 113147

113147

113147

113147

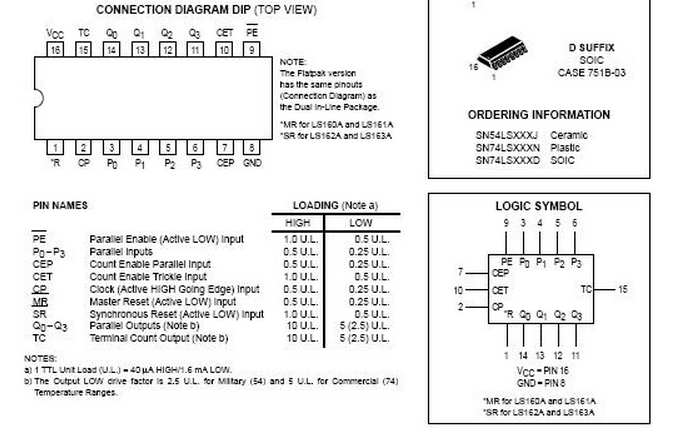

74LS160

74LS160 - Synchronous Decade Counters(direct clear) - Hitachi Semiconductor

1970-01-01 08:00:00

74ls160十进制计数器

本文主要介绍了74ls160十进制计数器电路的设计与实现。74LS160是二~十进制同步可预置计数器,1脚Cr为清零端,低电平有效.2脚CP为时钟脉冲输人端,上升沿触发.3~6V脚D1一D4为数据

2018-01-18 15:14:45 182091

182091

182091

182091

74ls161分频电路图大全(脉冲分频电路\同步加法计数器)

74LS161(或74LS160)和二4输入与非门74LS20构成百以内任意进制计数器,并采用LED数码管显示计数进制。采用555定时器构成多谐振荡电路,为同步加法计数器提供时钟输入信号。

2018-05-08 14:41:38 95799

95799

95799

95799

74ls192和74ls160的区别有哪些

74ls192和74ls160同为十进制计数器,这两者之间有些什么区别呢?本文对这两款十进制计数器进行了介绍。

2017-12-21 10:27:08 29885

29885

29885

29885

同步计数器74ls162设计24进制计数器

本文首先介绍了计数器种类与应用,其次介绍了74LS160并行置零法设计24进制计数器电路图,最后介绍了74ls162设计24进制计数器原理电路图。

2018-05-08 11:46:43 54648

54648

54648

5464874LS160中文资料pdf

54160/74160十进制同步计数器(异步清除)简要说明:160 为可预置的十进制同步计数器,共有 54/74160 和 54/74LS160 两种线路结构型式,其主要电特性的典型值如下:型号 F

2008-03-19 19:42:55 500

500

500

500基于74LS160的N进制计数器仿真设计

针对任意进制(N进制)计数器的设计目的,采用反馈复零法对基于同步十进制计数器7415160进行设计,分别采用异步清零法实现了6进制计数器和同步置数法实现7进制计数器的设计,通过应用EWB软件对所设

2017-12-21 17:08:37 60783

60783

60783

60783

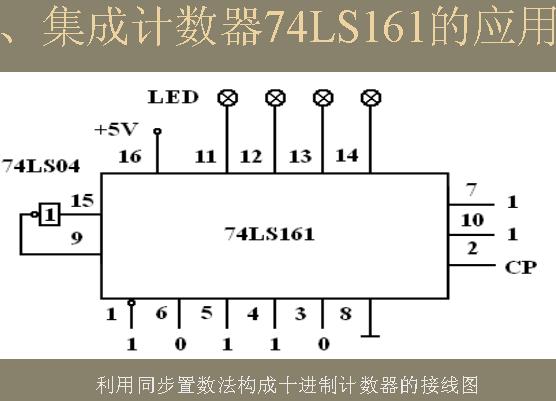

74ls161中文资料_74ls161计数器功能及其应用

本文介绍了74ls161的引脚图及功能和应用74ls161的60进制同步加法计数器和十进制计数器。

2018-01-02 15:13:02 534630

534630

534630

534630

74ls161制作24进制计数器设计

74ls161为二进制同步计数器,具有同步预置数、异步清零以及保持等功能。两片74ls161可设计一个24进制计数器。

2018-01-16 15:30:46 110315

110315

110315

110315

采用归零法的N进制计数器原理

计数器是一种重要的时序逻辑电路,广泛应用于各类数字系统中。介绍以集成计数器74LS161和74LS160为基础,用归零法设计N进制计数器的原理与步骤。用此方法设计了3种36进制计数器,并

2012-03-20 10:21:38 95

95

95

9574LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)

本文主要介绍了74LS161集成计数器电路(2、3、4、6、8、10、60进制计数器)。74LS161是4位二进制同步计数器,该计数器能同步并行预置数据,具有清零置数,计数和保持功能,具有进位输出端

2018-01-18 10:56:39 324594

324594

324594

324594

74ls160数字钟仿真电路(振荡器\74LS47D\计数器\74LS48)

、秒计数电路。采用两片74LS160按下图所示连接,可以构成作60分频计数,用于数字钟中的秒计数器。标准秒脉冲经过控制门进入秒计数器,并显示其计数值,当计数满60时得到一个进位“分”脉冲,同时秒计数器

2018-05-08 09:11:33 61651

61651

61651

61651

74ls290计数器电路大全(六种进制计数器电路)

74ls290是一个二,五,十进制计数器,本文为大家介绍由74ls290构成的各种进制计数器的电路。

2018-01-26 09:26:11 106188

106188

106188

106188

74ls163实现任意进制计数器

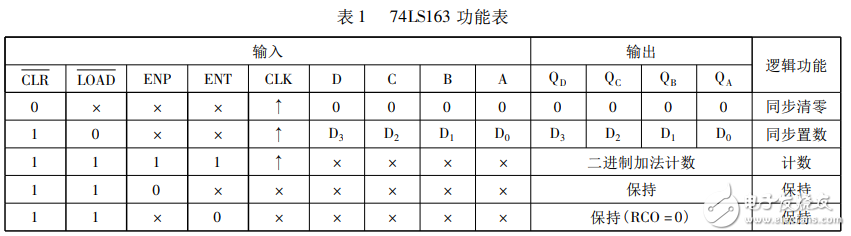

本文主要介绍了74ls163实现任意进制计数器。74LS163是集成4位二进制加法计数器,功能表如表1所示。其中CLK为时钟脉冲输入端、ENP及ENT为计数控制端、LOAD为同步预置数控制端、CLR

2018-05-08 12:10:14 78487

78487

78487

78487

基于可编程计数器74LS161的循环码计数器设计

基于探索MSI可编程同步二进制加法计数器74LS161改变应用方向进行功能扩展的目的,采用逻辑修改的方法给出了在二进制计数的基础上实现循环码计数的设计方法,即以74LS161已有的状态

2012-02-29 11:55:13 115

115

115

11574ls161构成12进制计数器设计

74LS160是十进制计数器,要实现十二进制计数器必须用两片实现级联,把各位芯片预置1,当数码管显示9时,个位芯片开始进位即B端为0C端为1,经过与非门输出高电平,十位芯片开始工作,十位芯片由0变为

2018-01-16 15:17:32 111115

111115

111115

111115

74ls160引脚功能_逻辑功能_特性参数及应用电路

74LS160 芯片同步十进制计数器(直接清零) ·用于快速计数的内部超前进位 ·用于n 位级联的进位输出 ·同步可编程序 ·有置数控制线 ·二极管箝位输入 ·直接清零 ·同步计数 本电路是由4 个

2017-12-21 16:29:13 584471

584471

584471

584471

74LS161异步置零法构成任意进制计数器的Multisim仿真

介绍了集成4位二进制计数器 74LS161 异步置零法构成任意进制计数器的 Multisim 仿真方案,即以波形方式显示计数器的计数过程、过渡状态形成异步置零信号的过程,用四踪示波器以面板

2011-08-05 14:25:22 330

330

330

33074ls160引脚图及功能真值表介绍

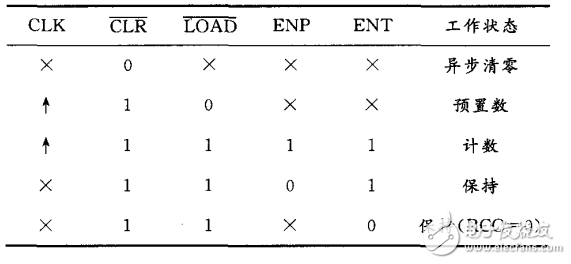

74ls160引脚图管脚图及功能真值表,74ls160引脚图管脚图74LS160的功能真值表-综合电路图 74ls160引脚图管脚图 74LS160的功能真值表

2022-05-25 16:39:14 102427

102427

102427

102427

74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)

本文主要介绍了74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)。74LS163是(模16)四位二进制同步计数器。该计数器能同步并行预置数据,同步清零,具有清零、置数、计数和保持四种

2018-05-08 14:27:23 51924

51924

51924

51924

74ls90设计60进制计数器

60进制计数器,由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择同步十进制计数器

2017-12-22 13:55:48 148134

148134

148134

148134

关于单片机的测频范围和误差分析

为了提高测量的精度,拓展单片机的测频范围,本设计采取了对信号进行分频的方法。设计中采用两片同步十进制加法计数器 74LS160 来组成一个 100 分频器。该 100 分频器由两个同步十进制加法

2020-08-21 14:43:07 8815

8815

8815

8815

74LS160数字逻辑芯片的工作原理

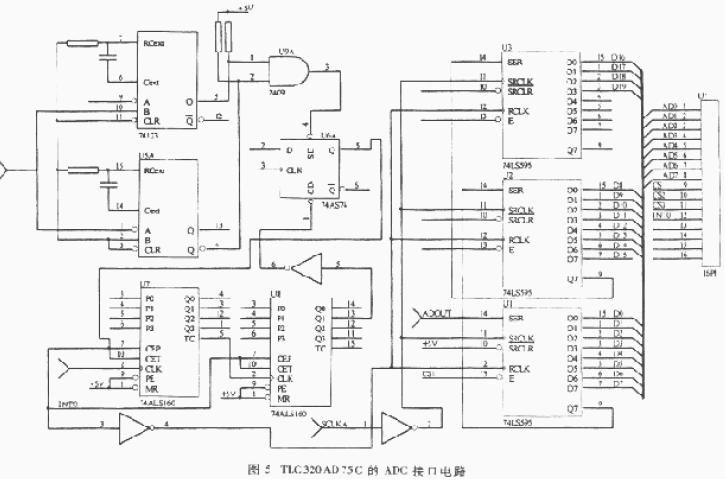

74LS160是常用的数字逻辑芯片,为十进制计数器,具有计数、置数、禁止清零等功能,其内部是由D触发器和逻辑门电路构成的。芯片具有两个使能端ENP和ENT,高电平有效,具有一个清零端MR,低电平有效,在计数时需要接高电平。D0-D3是并行输入,Q0-Q3是输出端,而且具有进位端RCO。

2020-01-25 14:37:00 113780

113780

113780

113780

74ls190应用电路图大全(五款74ls190不同进制计数器电路)

本文主要介绍了五款74ls190应用电路图。包括了60和100进制计数器(递增)电路,56进制递减计数器与100进制递减计数器电路和2位十进制可加减计数器电路。

2018-05-28 16:18:11 54071

54071

54071

54071

计数器74LS161的Multisim仿真

本文主要介绍了计数器74LS161的Multisim仿真。74LS161是具有异步置零、计数、预置数和保持功能的可编程集成中规模同步4位二进制加法计数器。用Muhisim仿真软件虚拟仪器中的字组

2018-01-17 18:19:48 59143

59143

59143

59143

基于74LS161的60进制计数器设计方案介绍

使用两片74LS161芯片级联的形式来构成六十进制计数器,一片控制个位,为十进制;另一片控制十位,为六进制。

2018-01-17 13:58:47 52599

52599

52599

52599

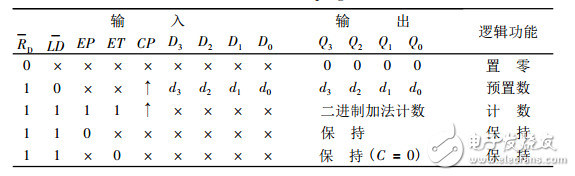

C180 2-10进制同步加法计数器的应用线路图

C180(CMOS)2-10进制同步加法计数器由同步的四级D型触发器组成.它的管脚外引线排列和功用如图所示,C180 2-10进制

2010-10-19 14:56:14 1889

1889

1889

1889

74LS290组成的十进制计数器电路图分享

计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。本文为大家介绍74LS290组成的十进制计数器。

2018-01-25 14:52:47 25181

25181

25181

25181

基于74ls192设计4/7进制计数器详解

由题目及其要求分析可知,首先要使用74LS192或40192设计一个4进制计数器和一个7进制计数器,然后通过数码管来显示状态。两种进制间的切换可以通过一个单刀双掷开关来实现。其重点和难点在于设计一个4进制计数器和一个7进制计数器。

2018-01-31 16:18:13 54591

54591

54591

54591

基于Proteus的任意进制计数器设计与仿真

提出一种基于Proteus 软件的任意进制计数器的设计。以74LS163 集成计数器为基础,用置数法设计了两种48 进制计数器,采用Proteus 软件对计数器进行仿真。结果表明,Proteus 软件具有实现48 进制计数器的功能。仿真图像清晰,能快速准确地验证设计结果。

2016-07-29 18:53:03 24

24

24

24100进制计数器

100进制计数器一、 实验目的:1、 熟悉MAX+PLUS环境的基本操作。2、 掌握VHDL和原理图的设计输入方式。3、 设计100进制计数器。二、&

2009-06-28 00:07:21 7414

7414

7414

741474ls163实现十进制计数器电路

本文主要介绍了74ls163实现十进制计数器电路。改变74LS163二进制计数器为十进制计数器,即用一FDS4435BZ个与非门,其两个输人取自QA和QD,输出接清零端α‘R。当第9个脉冲结束时,钣

2018-05-08 11:31:20 44957

44957

44957

44957

74ls160系列电路

74ls160系列电路:

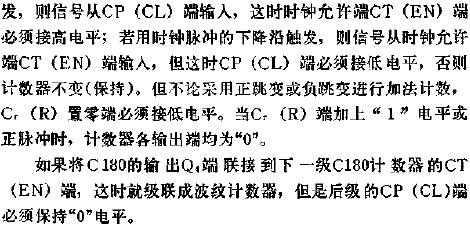

下图是TLC320AD75C 的ADC 与MCS51 接口电路,DAC 接口电路是上述电路的逆过程,只要将8位输出锁存移位

2008-01-06 21:58:30 3900

3900

3900

3900

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)

本文主要介绍了五款74ls192计数器应用电路图。其中包括了74ls192电子骰子电路、74ls192计时电路、74ls192定时电路、74ls19230进制计数器电路及两位十进制计数器。

2018-05-28 10:20:01 116393

116393

116393

116393

基于74LS161的扭环形计数器自启动设计

本文主要介绍了基于74LS161的扭环形计数器自启动设计。分析了扭环形计数器工作时的状态转换过程和MSI可编程计数器74LS161的逻辑功能,提出了采用74LS161构成扭环形计数器一些新的设计方案及几种逻辑修改方法。

2018-01-17 18:05:43 36195

36195

36195

36195

74ls161十进制计数器电路图

74LS161为4位二进制同步加法计数器。其中 是异步清零端, 是预置数控制端,D3 D2 D1 D0是预置数输入端,CTt和CTp是计数使能端,CO是进位输出端(CO=Q3 Q0

2021-07-09 16:12:21 73502

73502

73502

73502

基于Multisim的计数器设计仿真

计数器是常用的时序逻辑电路器件,文中介绍了以四位同步二进制集成计数器74LS161和异步二-五-十模值计数器74LS290为主要芯片,设计实现了任意模值计数器电路,并用Multisim软件进行了

2013-07-26 11:38:41 133

133

133

133两个74LS192级联构成两位十进制计数器

本文主要介绍了两个74LS192级联构成两位十进制计数器。以两个74LS192级联构成两位十进制计数器控制实现0.0~9.9V的切换为例。低位计数器输出Qo、Qi、Q2、Q3分别提供0.1V

2018-05-09 09:52:23 53651

53651

53651

53651

100进制加减计数器的设计与制作

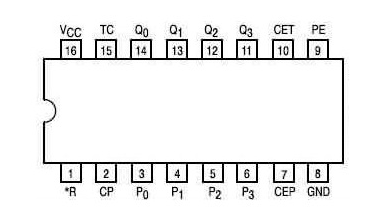

100进制加减计数器的设计与制作:本电路结构如图袁主要由晶体振荡电路,分频电路,控制电路,计数电路,译码电路,数码管显示等几部分构成。

2009-10-22 21:50:19 228

228

228

228浅谈用74LS90设计任意进制计数器

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,而且常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能,在电路设计中应用相当广泛。文章介绍一种用74LS90设计任意进制计数器的简单方法。

2017-12-22 13:39:13 103060

103060

103060

103060

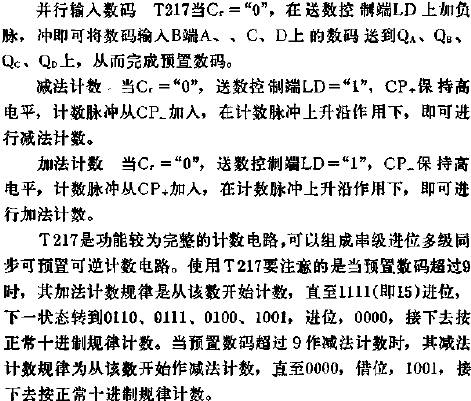

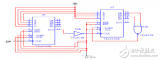

T217 2-10进制同步可预置可逆计数器的应用电路图

T217是2-10进制同步可预置可逆计数器,能同时作加法计数和减法计数.它的主要电参数为:电源电流ICC小于100MA,计数

2010-10-19 14:41:30 811

811

811

811

基于MSI的N进制计数器设计方法

计数器是数字逻辑系统中的基本部件,它是数字系统中用得最多的时序逻辑电路,本文主要阐述了用中规模集成计数器设计任意进制同步加法计数器的设计思想,并对设计方法和步骤作

2012-02-28 11:41:43 6157

6157

6157

6157

电子发烧友App

电子发烧友App

评论