用CMOS集成电路构成的数控分频计数器

- 计数器(91962)

相关推荐

集成电路CD40161-多功能计数器和分频器的电子元件

CD40161是一款常用的集成电路(IC)元件。它是一个多功能的计数器和分频器,具有广泛的应用领域。云芯将带您深入解释CD40161的功能、特点、应用以及未来前景,帮助您更好地了解这一电子元件。

2023-10-16 11:43:11 116

116

116

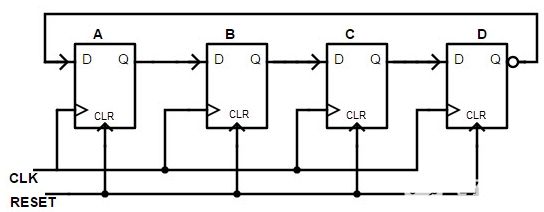

116用D触发器构成异步二进制加/减计数器

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

2023-10-11 09:41:13 170

170

170

170

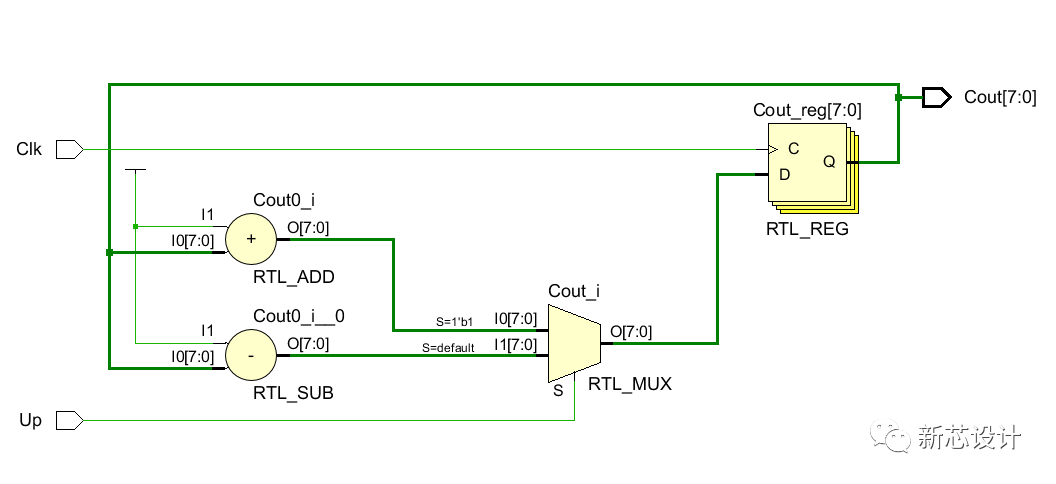

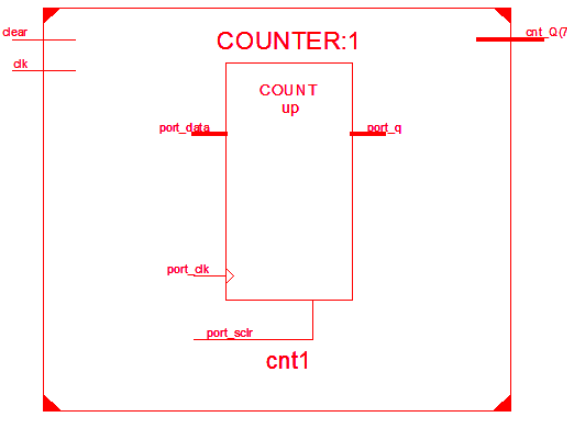

基于Verilog的经典数字电路设计—计数器

在数字系统中,使用得最多的时序电路差不多就是计数器了。计数器不仅能够用于对时钟脉冲计数,还可以用于分频、定时、产生节拍脉冲、产生脉冲序列以及进行数字运算等等。

2023-10-09 17:48:34 150

150

150

150

按功能分集成电路有哪些类型 集成电路的工作速度主要取决于什么

数字集成电路 (Digital Integrated Circuit,DIC):数字集成电路主要用于处理和操作数字信号,执行逻辑运算、计数和存储等功能。常见的数字集成电路包括逻辑门、触发器、计数器、存储器等。

2023-08-04 15:48:01 405

405

405

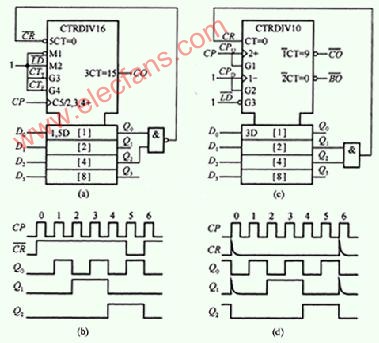

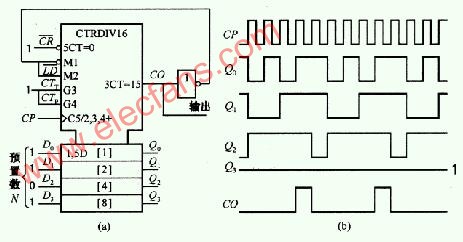

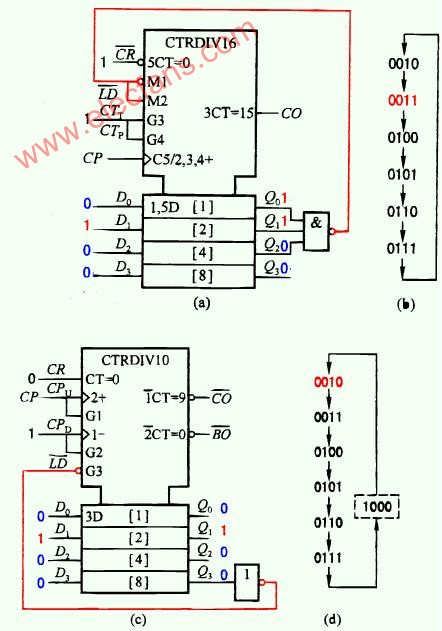

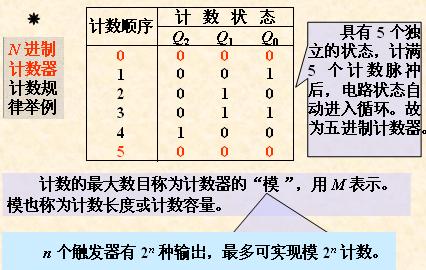

405N进制计数器的实现

电子电器必不可少的核心器件。在时序逻辑电路中,集成计数器的应用更是无孔不入,无所不在。应用集成计数器,加上简单的电路及连线,就可以组成各种形式的、任意进制的计数器,广泛应用于计数、计时、分频等电路中

2008-07-05 13:41:26

PLC计数器例子之3个计数器构成的24小时时钟

控制要求 利用 3 个计数器配合 1s 时钟脉冲标志 M1013,构成一个标准 24 小时时钟。 元件说明 控制程序 程序说明

2023-04-17 15:43:31 0

0

0

0同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?

在数字电子产品中,计数器是由一系列触发器组成的时序逻辑电路。顾名思义,计数器用于计算输入在负或正边沿转换中出现的次数。根据触发触发器的方式,计数器可以分为两类:同步计数器和异步计数器。了解这两种计数器的工作原理以及它们之间的区别。

2023-03-25 17:31:07 11617

11617

11617

11617

计数器及时序电路

1、了解时序电路的经典设计方法(D触发器、JK触发器和一般逻辑门组成的时序逻辑电路)。

2、了解同步计数器,异步计数器的使用方法。

3、了解同步计数器通过清零阻塞法和预显数法得到循环任意进制

2022-07-10 14:37:37 15

15

15

15比较TTL集成电路与CMOS集成电路

比较TTL集成电路与CMOS集成电路元件构成高低电平范围集成度比较:逻辑门电路比较元件构成TTL集成电路使用(transistor)晶体管,也就是PN结。功耗较大,驱动能力强,一般工作电压+5V

2021-11-30 20:51:05 26

26

26

26"stm32f0按键计数器程序_数字系统设计, 8个经典计数器电路方案合辑"

计数器(Counter)由基本的计数单元和控制门所组成,是在数字系统中对脉冲的个数进行计数,以实现测量、计数和控制功能,且兼有分频功能的仪器。计数器按进位制不同,分为二进制计数器和十进制计数器;按

2021-11-25 18:06:07 32

32

32

32什么是计数器芯片?

什么是计数器芯片? 一般来说,计数器芯片就是用来实现计数这种最基础运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数

2021-07-13 14:09:37 11289

11289

11289

11289计数器电路设计中分频电路的作用解析

假设时钟分频是N,则设置一个计数器,计数长度是N(即从0计数到N-1),然后在计数器为计数到(N-1)/2的时候,翻转一下分频时钟信号。

2020-11-06 13:59:47 9216

9216

9216

9216

采用中规模集成计数器进行任意进制计数器设计的解决方案

计数器是数字逻辑系统中的基本部件, 它是数字系统中用得最多的时序逻辑电路,其主要功能就是用计数器的不同状态来记忆输入脉冲的个数。除此以外还具有定时、分频、运算等逻辑功能。 计数器不仅能用于对时钟脉冲的计数, 还可使用于定时、分频、产生节拍脉冲以及进行数字运算等。只要是稍微复杂一些的

2019-05-30 08:24:00 12413

12413

12413

12413

计数器原理

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2019-01-24 14:35:40 62199

62199

62199

62199数字分频器(SN7490、SN7442、SN74150)

关键词:SN74150 , SN7442 , SN7490 , 数字分频器 如图所示为数字分频电路。该电路由3块集成电路构成,分频系数可以从1~9变化。计数器SN7490输出的二-十进制数送至译码器

2018-10-08 07:58:01 1571

1571

1571

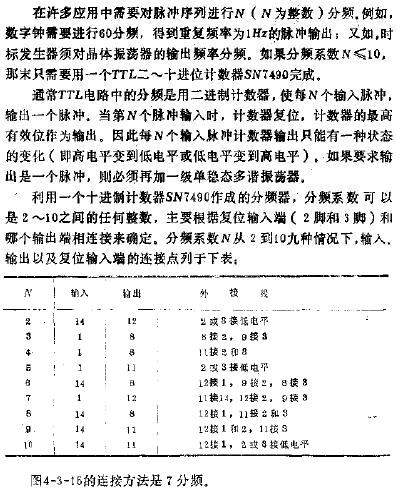

1571由TTL十进制计数器构成的分频器

关键词:TTL , 分频器 , 计数器 , 十进制 如图所示为由TTL十进制计数器构成的分频电路。在许多情况下。需要对脉冲序列进行N(N为整数)分频。例如,数字钟需要进行60分频,得到重复频率为

2018-10-03 18:46:02 2650

2650

2650

2650计数器逻辑功能测试实验报告

本文主要介绍了计数器逻辑功能测试实验报告。时序逻辑电路中,有一种电路叫计数器,计数器是用来对时钟脉冲进行计数的,运用计数原理还可拓展为对数字系统进行定时、分频和执行数字运算等功能。

2018-06-27 08:00:00 15

15

15

1574ls161分频电路图大全(脉冲分频电路\同步加法计数器)

本文主要介绍了74ls161分频电路图大全(脉冲分频电路\同步加法计数器)。计数器又称为分频器。N进制计数器的进位输出脉冲就是计数器输入脉冲的N分频。N进制计数器可直接作为N分频器。用同步加法计数器

2018-05-08 14:41:38 95799

95799

95799

95799

74ls163应用电路图大全(N进制计数器\分频电路\时钟脉冲)

功能,并且具有进位信号输出,可串接计数使用。重点分析了构成N进制计数器、以74LS163为基础设计一个6分频电路等。

2018-05-08 14:27:23 51924

51924

51924

51924

机械计数器结构及原理图

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2018-02-24 15:31:08 43744

43744

43744

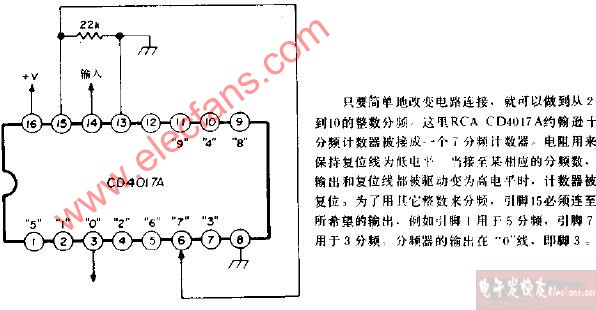

43744cd4017计数器电路图(三款cd4017计数器电路)

本文开始对CD4017功能与CD4017逻辑结构图进行了介绍,其次分别介绍了用CD4017和选择开关组成多进制计数器、CD4017组成的1/n计数器电路与用CD4017组成1~17进制计数器电路图。

2018-01-31 13:58:06 22819

22819

22819

22819

74ls290计数器电路大全(六种进制计数器电路)

74ls290是一个二,五,十进制计数器,本文为大家介绍由74ls290构成的各种进制计数器的电路。

2018-01-26 09:26:11 106188

106188

106188

106188

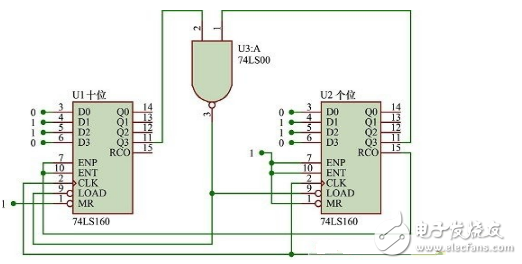

74ls160构成24进制计数器

本文主要介绍了74ls160构成24进制计数器电路设计。本设计采用异步清零。由两片十进制同步加法计数器74LS160和一片与非门74LS00以及相应的电阻开关组成。由外加送来的计数脉冲送入两个计数器

2018-01-18 15:43:05 145644

145644

145644

145644

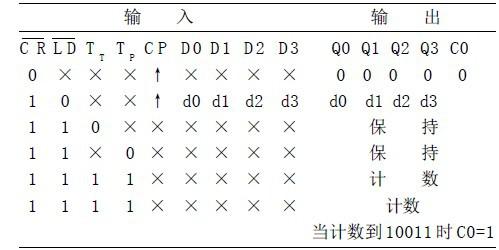

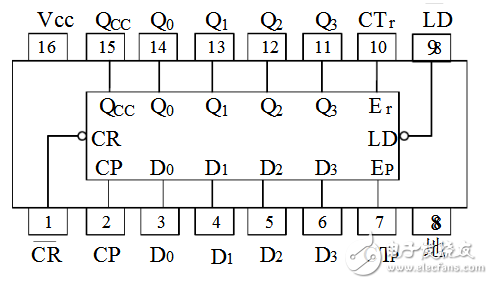

计数器74ls161工作原理(分频电路、真值表、逻辑功能)

本文主要介绍了计数器74ls161工作原理(分频电路、真值表、逻辑功能)。74LS161为二进制同步计数器,具有同步预置数、异步清零以及保持等功能。CP是时钟脉冲信号端,CLK是异步清零端,LD

2018-01-17 19:14:24 307967

307967

307967

307967

任意进制计数器设计方案汇总(七款模拟电路设计原理详解)

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2018-01-17 17:36:07 67188

67188

67188

67188

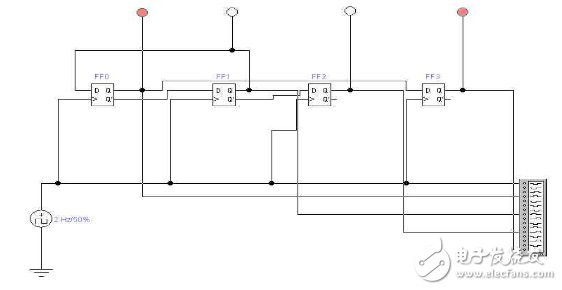

环形计数器介绍_4位环形计数器波形图

环形计数器是由移位寄存器加上一定的反馈电路构成的,用移位寄存器构成环形计数器的一般框图,它是由一个移位寄存器和一个组合反馈逻辑电路闭环构成,反馈电路的输出接向移位寄存器的串行输入端,反馈电路的输入端根据移位寄存器计数器类型的不同,可接向移位寄存器的串行输出端或某些触发器的输出端。

2018-01-16 14:54:44 40935

40935

40935

40935

浅谈用74LS90设计任意进制计数器

计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,而且常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能,在电路设计中应用相当广泛。文章介绍一种用74LS90设计任意进制计数器的简单方法。

2017-12-22 13:39:13 103060

103060

103060

103060

24进制计数器的设计

集成计数器常见的是多位二进制计数器及十进制计数器,当需要实现其它进制计数器时,通常利用现有的集成计数器进行适当的连接而构成。对于当设计要求没有限定计数器的状态编码时电路设计的灵活性问题已有文献进行

2017-11-09 16:36:16 81

81

81

81计数器的控制及应用

计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成

2017-09-25 10:13:37 8

8

8

8十进制计数器/分频器

约翰逊MC14017B是五级十进制计数器内置代码转换器。 高速运行和约翰逊spike-free输出是通过使用十进制计数器的设计。 十个解码输出通常是低,只在适当的十进制时间走高。 输出的正向变化的时钟脉冲。 这部分可用于分频应用程序以及十进制计数器或十进制译码显示应用程序。

2017-04-06 09:03:48 28

28

28

28基于Proteus的任意进制计数器设计与仿真

提出一种基于Proteus 软件的任意进制计数器的设计。以74LS163 集成计数器为基础,用置数法设计了两种48 进制计数器,采用Proteus 软件对计数器进行仿真。结果表明,Proteus 软件具有实现48 进制计数器的功能。仿真图像清晰,能快速准确地验证设计结果。

2016-07-29 18:53:03 24

24

24

24基于Multisim的计数器设计仿真

计数器是常用的时序逻辑电路器件,文中介绍了以四位同步二进制集成计数器74LS161和异步二-五-十模值计数器74LS290为主要芯片,设计实现了任意模值计数器电路,并用Multisim软件进行了

2013-07-26 11:38:41 133

133

133

133采用归零法的N进制计数器原理

计数器是一种重要的时序逻辑电路,广泛应用于各类数字系统中。介绍以集成计数器74LS161和74LS160为基础,用归零法设计N进制计数器的原理与步骤。用此方法设计了3种36进制计数器,并

2012-03-20 10:21:38 95

95

95

95基于MSI的N进制计数器设计方法

计数器是数字逻辑系统中的基本部件,它是数字系统中用得最多的时序逻辑电路,本文主要阐述了用中规模集成计数器设计任意进制同步加法计数器的设计思想,并对设计方法和步骤作

2012-02-28 11:41:43 6157

6157

6157

6157

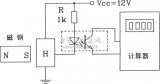

霍尔接近开关构成的计数器电路

图中采用了光电耦合器隔离和8位计算器。每当磁钢接近HK-1开关一次,计算器记一个数,并累加,从而完成 计数 功能。霍尔接近开关构成的计数器电路:

2011-09-29 11:56:00 4474

4474

4474

4474

基于计数器的数字电子钟的设计

本设计就是研究用数字电路实现的数字电子钟,整体的电路设计就是由振荡器、分频器、计数器、译码器、LED显示器、校时电路组成。这种用数字电路实现的电子钟与机械式时钟相比具

2011-09-14 10:50:58 9468

9468

9468

9468

74LS161异步置零法构成任意进制计数器的Multisim仿真

介绍了集成4位二进制计数器 74LS161 异步置零法构成任意进制计数器的 Multisim 仿真方案,即以波形方式显示计数器的计数过程、过渡状态形成异步置零信号的过程,用四踪示波器以面板

2011-08-05 14:25:22 330

330

330

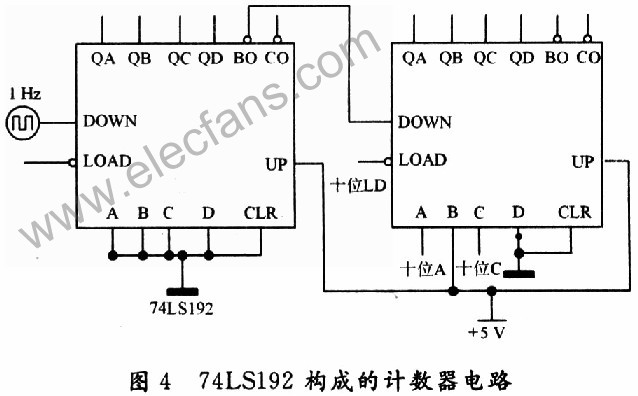

33074LSl92构成的计数器电路图

74LSl92构成的计数器电路图如图4所示:左边的1片74LSl92芯片为计数器的个位,右边的1片74LSl92芯片为计数器的十位,个位和十位计数器的四个输出端都接上数码管显示。其中作为个位

2010-08-23 09:35:03 2206

2206

2206

2206

移位型计数器中反馈逻辑电路的设计

摘要:移位型计数器是以移位寄存器为主体构成的同步计数器。这类计数器具有电路连接简单,编码别具特色的特点,用途十分广泛。文中介绍了移位型计数器中反馈逻辑电路设计

2010-04-26 11:16:54 29

29

29

29计数器,计数器的工作原理是什么?

计数器,计数器的工作原理是什么?

在数字系统中使用最多的时序电路是计数器。计数器不仅能用于对时钟脉冲进行计数还可以用于分频、定时,产生

2010-03-08 13:50:14 59468

59468

59468

59468CMOS集成电路使用操作原则

CMOS集成电路使用操作原则

所有MOS集成电路(包括 P 沟道 MOS, N 沟道 MOS, 互补 MOS — CMOS 集成电路) 都有一层绝缘栅,以防止电压击穿。一般器件

2010-02-05 09:23:18 931

931

931

931利用复位端构成的模6计数器电路

利用复位端构成的模6计数器电路

利用集成计数器的预置端和复位端可以构成任意模计数器。下图所示依次是利用74163和74192构成的

2010-01-12 13:54:31 4276

4276

4276

4276

CMOS 集成电路使用操作准则

CMOS 集成电路使用操作准则

CMOS 集成电路使用操作准则 所有 MOS 集成电路 (包括 P 沟道 MOS, N 沟道 MOS, 互补 MOS — CMOS 集成电路) 都有一层绝缘栅,

2009-11-30 11:08:12 775

775

775

775100进制加减计数器的设计与制作

100进制加减计数器的设计与制作:本电路结构如图袁主要由晶体振荡电路,分频电路,控制电路,计数电路,译码电路,数码管显示等几部分构成。

2009-10-22 21:50:19 228

228

228

228可逆、可预置计数器CD4029构成的任意N分频减法计数电路

图3是可逆、可预置计数器CD4029构成的任意N分频减法计数电路,U/D接“L”电平进行减法计数,B/D接“L”电平按BCD输出码进行计数,低位的Co进位到高位的CT输

2009-06-22 07:44:38 4593

4593

4593

4593

2-4分频电路(双D-FF或双JK-FF器件来构成)

用于N=2-4分频比的电路,常用双D-FF或双JK-FF器件来构成,分频比n>4的电路,则常采用计数器(如可预置计数器)来实现更为方便,一般无需再用单个FF来组合。

2009-06-22 07:43:15 6925

6925

6925

6925

集成计数器实验

实验六 集成计数器一、 实验目的1、 掌握TTL集成计数器74LS161的逻辑功能2、 熟悉74LS161的管脚排列3、 了解74LS161的应用二、 实验器材 实

2009-03-20 18:01:09 37

37

37

37 电子发烧友App

电子发烧友App

评论