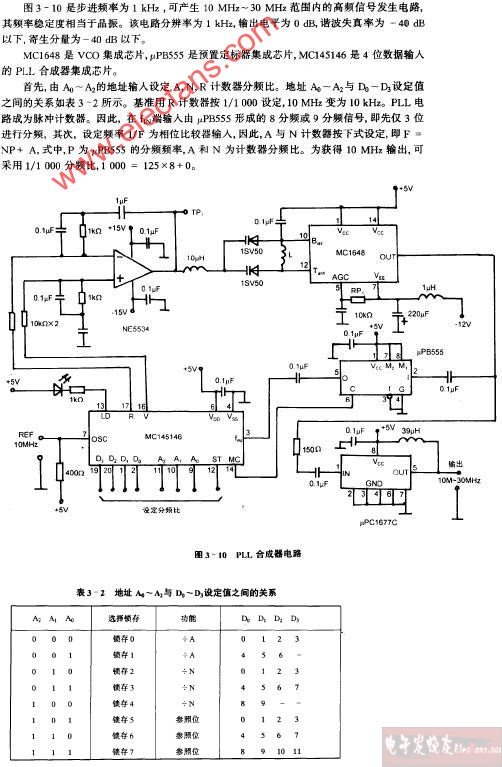

锁相环频率合成器的优缺点 锁相环频率合成器,又称为PLL(Phase Locked Loop),是一种广泛应用的电路,能够将输入信号的频率合成为电路所需要的频率,并且能够实现对信号的相位和频率

2023-09-02 14:59:33 246

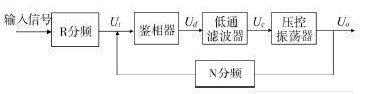

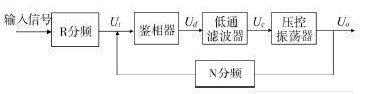

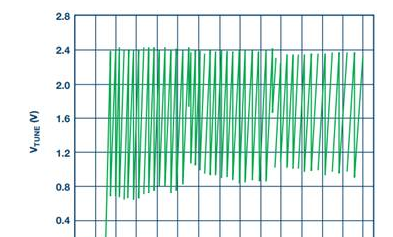

246 频率合成器在锁相环 (PLL) 中工作,其中相位/频率检测器 (PFD) 将反馈频率与参考频率的分频版本进行比较(图 1)。PFD的输出电流脉冲经过滤波和积分以产生电压。该电压驱动外部压控振荡器 (VCO) 增加或降低输出频率,从而将 PFD 的平均输出驱动至零。

2023-06-17 14:59:01 493

493

MAX2902 ISM发送器设计用于与外部频率合成器IC组合,形成完整的TX路径方案。根据系统要求,可以使用小数N分频或整数N分频频率合成器IC。了解两种频率合成器的通道步长、相位噪声和PLL锁定

2023-03-03 15:22:43 249

249

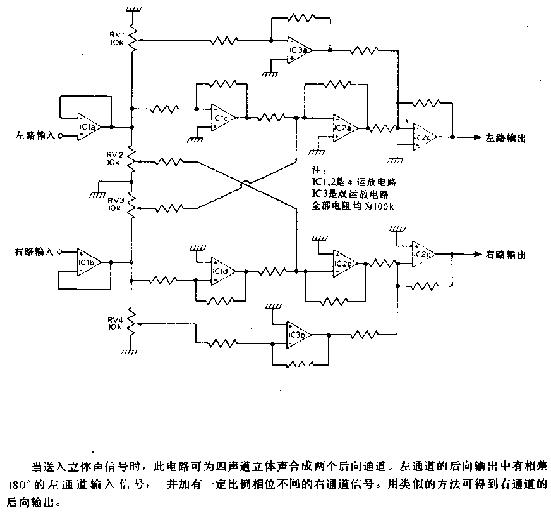

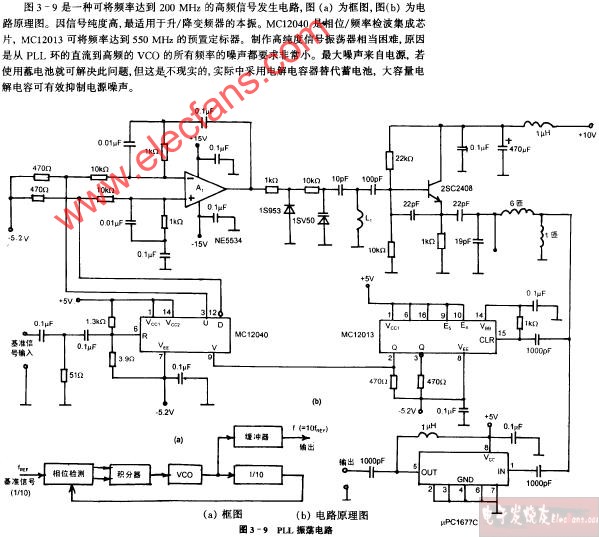

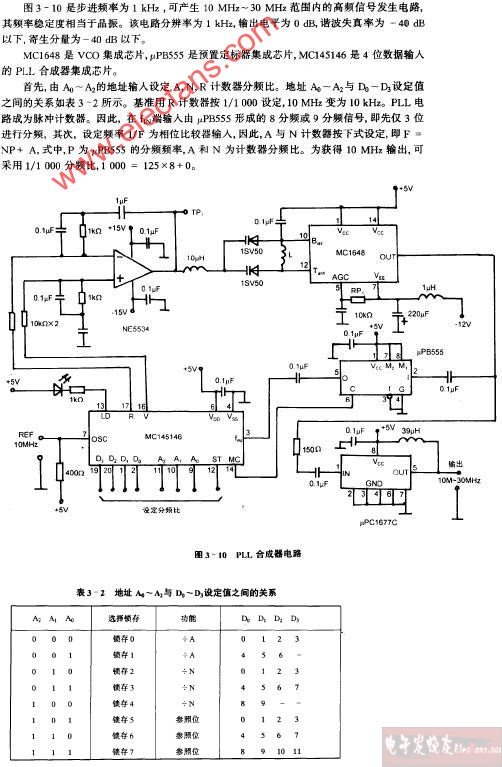

pll频率合成器工作原理与pll频率合成器的原理图解释 我们要搞清楚pll频率合成器工作原理与pll频率合成器的原理图就要先搞清楚pll和频率合成器的概念。 频率合成器:将一个高稳定度和高精度的标准

2023-02-24 18:19:52 4878

4878

频率合成器在锁相环 (PLL) 中工作,其中相位/频率检测器 (PFD) 将反馈频率与参考频率的分频版本进行比较(图 1)。PFD的输出电流脉冲经过滤波和积分以产生电压。该电压驱动外部压控振荡器 (VCO) 增加或降低输出频率,从而将 PFD 的平均输出驱动至零。

2023-02-03 10:50:09 487

487

已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性能架构的实现。

2022-10-14 10:30:36 1451

1451 时钟发生器/PLL频率合成器SOP-82~15V2MHz封装:SOP-8

2022-08-19 15:57:46 0

0 本文设计了一种多环锁相频率合成器。多环锁相环路有直接数字频率合成(DDS)环路和锁相频率合成环路(PLL)组成。充分利用两个不同环路的优点,既保证了高的输出频率,又得到了较高的频率分辨率。【关键词

2010-05-13 09:09:53

ADF4107 PLL频率合成器数据表

2021-06-18 10:01:57 7

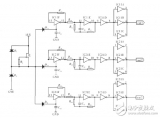

7 图1所示电路使用带集成式VCO和外部PLL的ADF4350频率合成器,通过隔离PLL频率合成器电路与VCO电路将杂散输出降至最低。集成PLL和VCO的器件可从数字PLL电路馈通至VCO,由于PLL

2021-05-28 17:50:57 7

7 ADF4007:高频分频器/PLL合成器数据表

2021-05-20 11:57:37 0

0 ADF4108:PLL频率合成器数据表

2021-05-19 18:23:27 13

13 LTC6951:集成压控振荡器数据表的超低抖动多输出时钟合成器

2021-05-19 11:33:05 8

8 ADF4106:PLL频率合成器数据表

2021-04-29 08:52:36 11

11 ADF4150HV:高压小数N/整数N PLL合成器数据表

2021-04-28 18:30:46 1

1 ADF4193:低相位噪声、快速建立PLL频率合成器数据表

2021-04-27 21:07:31 3

3 ADF4206/ADF4208:双射频PLL频率合成器数据表

2021-04-26 08:11:58 7

7 ADF4150:小数N/整数N PLL合成器数据表

2021-04-23 08:20:24 9

9 ADF4212L:双低功耗PLL频率合成器数据表

2021-04-22 19:18:02 5

5 ADF4151:小数N/整数N PLL合成器数据表

2021-04-14 14:41:56 7

7 ADF4107:PLL频率合成器数据表

2021-04-14 09:44:36 8

8 ADF41020:18 GHz微波PLL频率合成器

2021-03-21 10:16:11 10

10 AN-873: ADF4xxx系列PLL频率合成器的锁定检测

2021-03-21 09:34:20 6

6 ADF4155:整数N/小数N分频PLL频率合成器

2021-03-20 17:01:57 11

11 UG-160: 整数N分频PLL频率合成器评估板

2021-03-20 10:17:59 6

6 UG-161:PLL频率合成器评估板

2021-03-20 09:54:34 6

6 UG-158: 7.5 GHz PLL频率合成器评估板

2021-03-20 09:48:41 2

2 UG-164:针对PLL频率合成器的1750 MHz评估板用户指南

2021-03-19 12:49:22 4

4 UG-092: ADF4001 PLL频率合成器评估板

2021-03-19 12:32:51 5

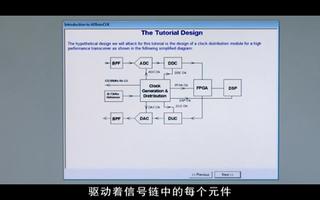

5 几乎每个RF和微波系统都需要频率合成器。频率合成器产生本振信号以驱动混频器、调制器、解调器及其他许多RF和。频率合成器常被视为系统的心跳,创建方法之一是使用锁相环(PLL)频率合成器。传统上,一个

2020-10-15 10:43:00 4

4 利用频率合成器,你可以产生单一参考频率的各种不同倍数的输出频率。其主要应用是为RF信号 的上变频和下变频产生本振(LO)信号。频率合成器在锁相环(PLL)中工作,其中鉴频鉴相器(PFD)将反馈频率

2020-10-12 10:43:00 0

0 ADI公司针对时钟和频率合成器件(如直接频率合成(DDS)、锁相环(PLL)和时钟分配器)的选择、使用和配置提供了一系列工具,大幅简化设计流程

2019-06-25 06:18:00 3141

3141

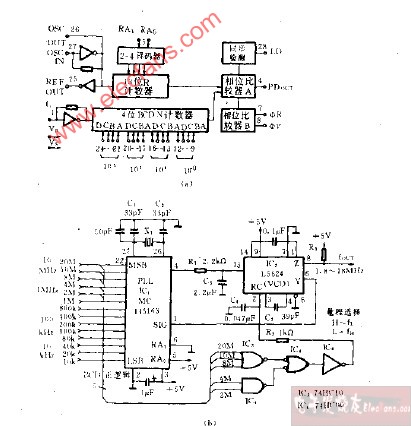

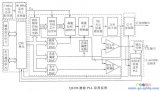

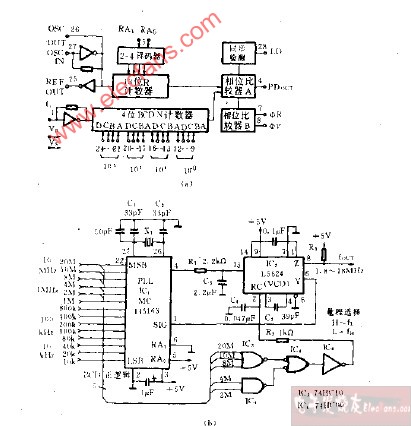

频率合成器主要有直接式、锁相式、直接数字式和混合式4种。目前,锁相式和数字式容易实现系列化、小型化、模块化和工程化,性能也越来越好,已逐步成为最为典型和广泛的应用频率合成器[1]。本文主要采用集成锁相环PLLphase-Lockde Loop芯片CD4046,运用FPGA来实现PLL频率合成器。

2019-01-07 09:52:00 2843

2843

为了应对日益紧缩的时钟抖动预算,麦瑞半导体(Micrel, Inc)已推出两个全新系列的ClockWorks超低抖动时钟合成器,能够满足这些精确计时要求。SM84xxxx标准时钟合成器系列,以及ClockWorks Flex可编程时钟系列的首台新型合成器SM802xxx。

2018-10-31 08:24:00 3859

3859 一70 dB,能输出DC~60 MHz的TTL信号,具有AM、FM、FSK、DPSK调制功能。 1. 40 MHz高稳定基准时钟 为了合成器输出信号的高质量,40 MHz时钟是用一个高稳定度5 MHz(优于l0-9/s)的恒温晶体振荡器,通过8倍频 PLL 系统获得的。

2018-03-17 11:13:00 3321

3321

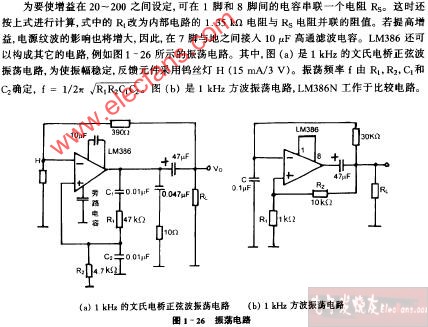

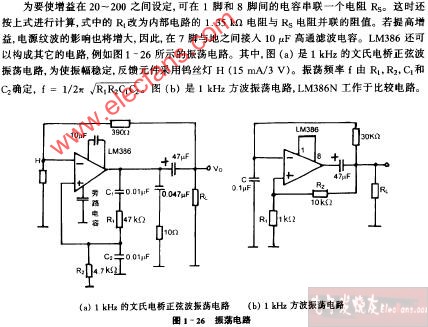

本文为大家介绍了自激振荡电路的概念、产生自激振荡的条件及三个自激振荡电路图。

2018-01-08 15:17:04 46501

46501

几乎每个RF和微波系统都需要频率合成器。频率合成器产生本振信号以驱动混频器、调制器、解调器及其他许多RF和微

2017-12-07 07:11:00 8548

8548

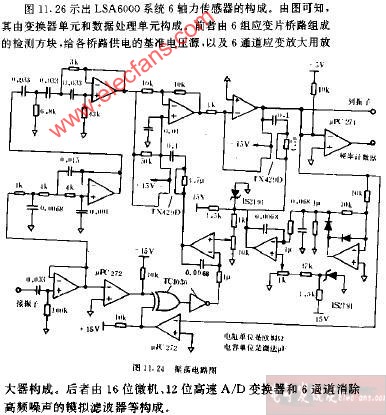

的设计、陶瓷与晶体振荡电路的设计,以及函数发生器的设计、电压控制振荡电路的设计、PLL频率合成器的设计、数字频率合成器的设计,等等。

2017-11-24 11:09:25 128

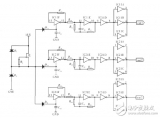

128 结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分 辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析

2017-10-27 17:54:21 7

7 学习单片机电路图的很好的资料——DDS-PLL组合跳频频率合成器

2016-11-03 15:15:39 16

16 DDS-PLL组合跳频频率合成器,有需要的都可以看看。

2016-07-20 15:48:57 30

30 美商亚德诺公司(ADI)发表一款具备领先的相位杂讯性能的PLL 合成器。从受到广泛使用的4GHz ADF 4153 fractional-N(分数N )PLL 升级上来的接脚与软体相容的ADF 4153A PLL 合成器,有利于提升在

2012-11-20 09:55:55 1178

1178 ADF4xxx系列PLL频率合成器的锁定检测

2011-11-29 15:37:17 38

38 电子发烧友为大家提供了时钟脉冲边沿整形电路图,本站还有其他相关资源,希望对您有所帮助!

2011-09-15 10:19:50 4669

4669

应用FPGA,采用PLL频率合成技术,结合教学实验平台的需要,设计出了一个整数/半整数频率合成器,输出范围为1kHz~999.5kHz,步进频率可达到0.5kHz。与以前的教学实验装置相比,系统在性能指

2010-09-01 09:43:34 45

45 对体积、速度和省电的更进一步的要求推动了频率合成器技术的发展。目前频率合成器的一个明显趋势是集成了越来越多的微型锁相环(PLL)/压控振荡器(VCO)元件。过去在PCB上的多个元

2010-05-28 11:11:31 1735

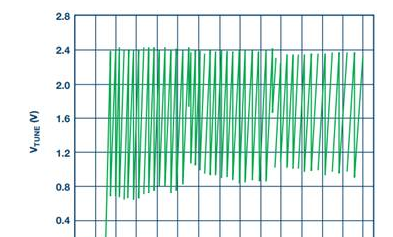

1735 PLL频率合成器的噪声基底测量

在无线应用中,相位噪声是频率合成器的关键性能参数。像PHS、GSM和IS-54等相位调制蜂窝系统的RF系统设计均需要低噪声本地振荡(L

2010-04-07 15:25:21 22

22 频率合成器,频率合成器原理及作用是什么?

所谓的频率合成器,就是以一个精确度、稳定度极好的石英晶体振荡器作为基准频率,并利用加、减

2010-03-23 11:04:54 14456

14456 ADI推出的 ADF4158 PLL 合成器

ADI最新推出的 ADF4158 PLL 合成器,可灵活 、高性价比地实现 FMCW (频率调制连续波)雷达系统。FMCW 雷达系统广泛应用于汽车、航空、军事、工业

2010-01-13 11:38:55 1220

1220 ADI发布新款PLL合成器,用于实现高性价比FMCW雷达系统

Analog Devices, Inc.,最新推出的 ADF4158 PLL 合成器,可灵活 、高性价比地实现 FMCW(频率调制连续波)雷达系统。FMCW

2010-01-13 08:37:59 852

852 ADI推出灵活、高性价比雷达系统的 PLL 合成器

Analog Devices, Inc.最新推出的 ADF4158PLL 合成器,可灵活 、高性价比地实现 FMCW (频率调制连续波)雷达系统。FMCW 雷达系统广

2010-01-12 17:58:32 720

720 本文讨论了DDS+PLL 结构频率合成器硬件电路设计中需要考虑的几方面问题并给出了设计原则,依此原则我们设计了一套短波波段频率合成器,实验结果证实了其可行性。

2009-09-07 16:07:29 34

34

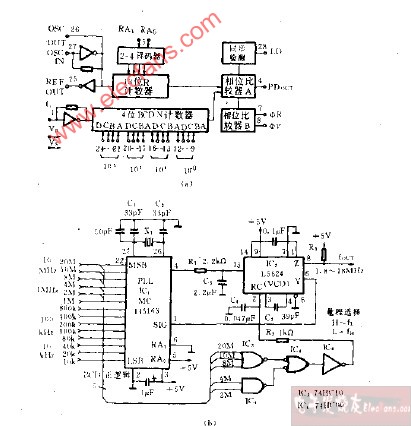

PLL合成器方式时钟脉冲振荡电路图

2009-07-20 13:41:20 436

436

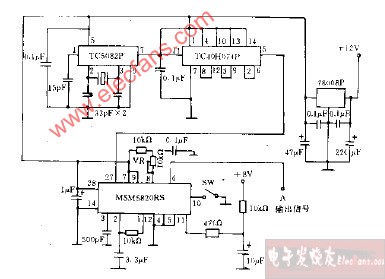

采用PLL的频率合成器电路图

2009-07-20 11:38:29 1005

1005

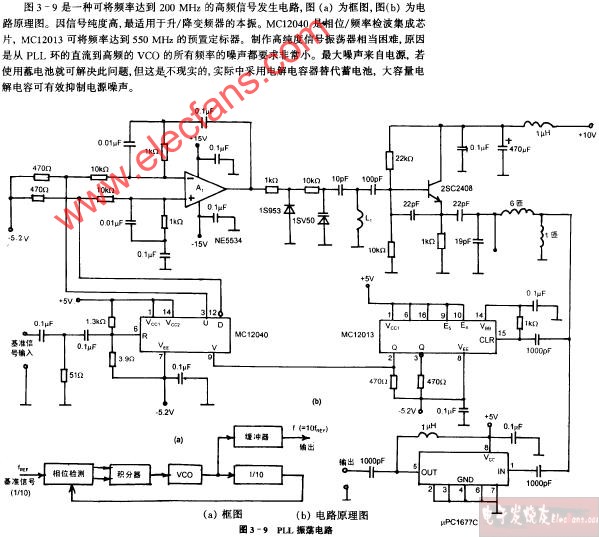

PLL振荡电路图

2009-07-14 17:08:44 725

725

PLL合成器电路图

2009-07-14 17:08:22 404

404

振荡电路图

2009-07-13 18:02:04 1568

1568

振荡电路图

2009-07-07 10:00:36 681

681

HFAN-04.5.5评估电源噪声抑制比对PLL时钟合成器的影响

Characterizing Power-Supply Noise Rejection in PLL Clock

2009-06-19 07:35:38 50

50

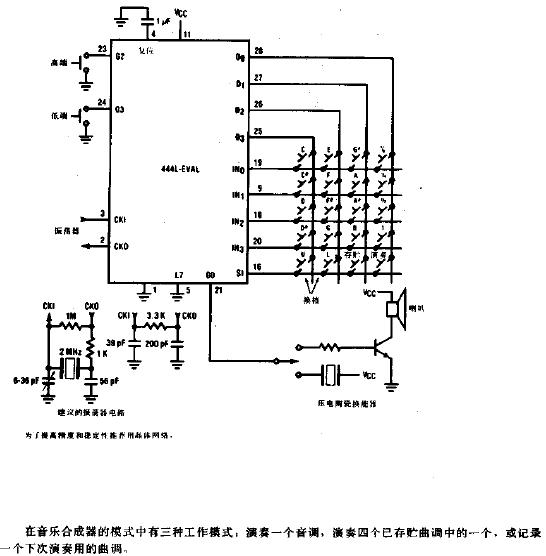

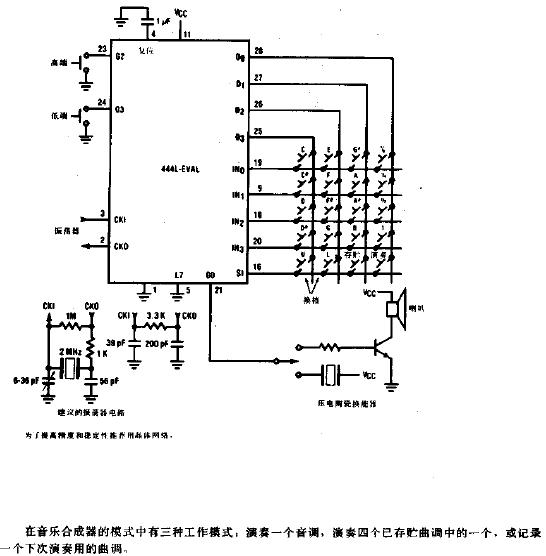

音乐合成器电路图

2009-04-09 09:40:20 1542

1542

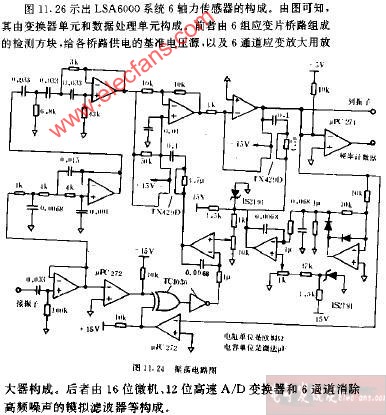

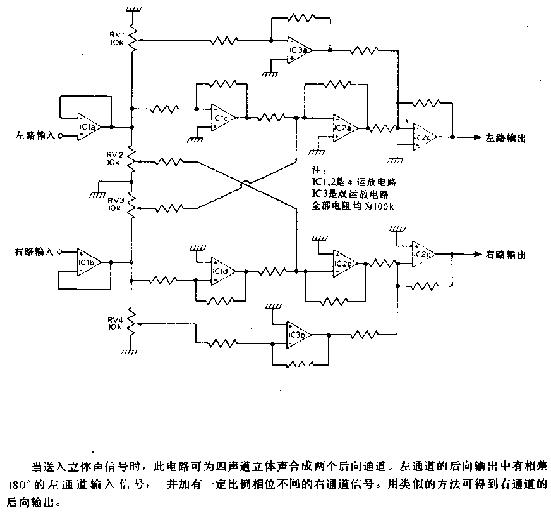

四通道合成器电路图

2009-04-09 09:36:23 711

711

时钟脉冲耦合电路图

2008-12-23 17:37:25 958

958

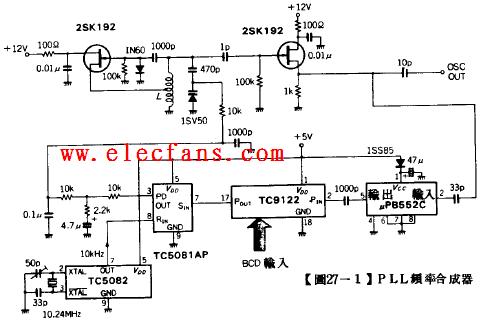

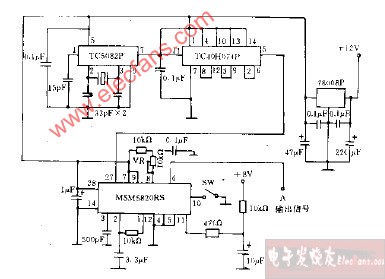

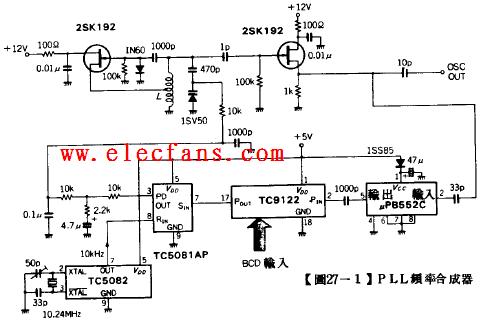

80M~120MHz频带PLL频率合成器图27-1为使用PLL IC TC9122(东芝)之80~120MHz的

2008-08-17 16:16:50 2027

2027

介绍了锁相频率合成器BU2614的结构、特性及控制方式。着重讨论了BU2614与单片机结合在收音机和集成压控振荡器中的应用。

Abstract:The composition、characteristic and control ways

2008-04-05 22:25:03 101

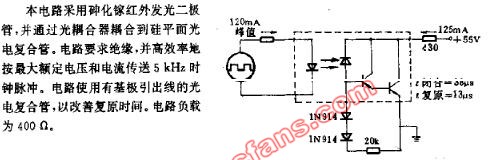

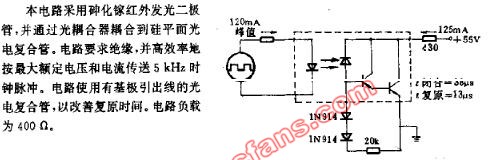

101 脉冲光电耦合电路图(能传送5000HZ时钟脉冲)

本电路采用砷化镓红外发光二极管,并通过光电耦合

2007-08-20 16:00:38 786

786

正在加载...

246

246 246

246 493

493 493

493

249

249 249

249

4878

4878 4878

4878

487

487 487

487

1451

1451 1451

1451 7

7 7

7 电子发烧友App

电子发烧友App

评论