一站式PCBA智造厂家今天为大家讲讲pcb设计布线解决信号串扰的方法有哪些?PCB设计布线解决信号串扰的方法。信号之间由于电磁场的相互而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可

2023-10-19 09:51:44 219

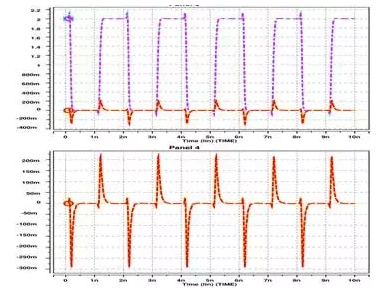

219 现一系列问题,如串扰、反射波、时钟抖动等。为了确保高速信号传输的稳定和可靠性,需要进行仿真串扰。本文将详细介绍高速信号仿真的串扰以及为什么需要进行仿真。 对于高速信号来说,串扰是一种令人头疼的问题。串扰是指高速信

2023-09-05 15:42:31 249

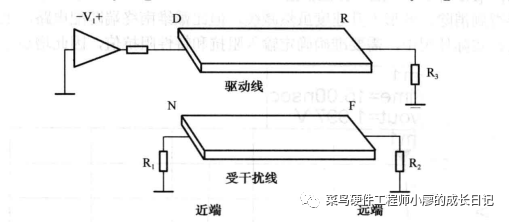

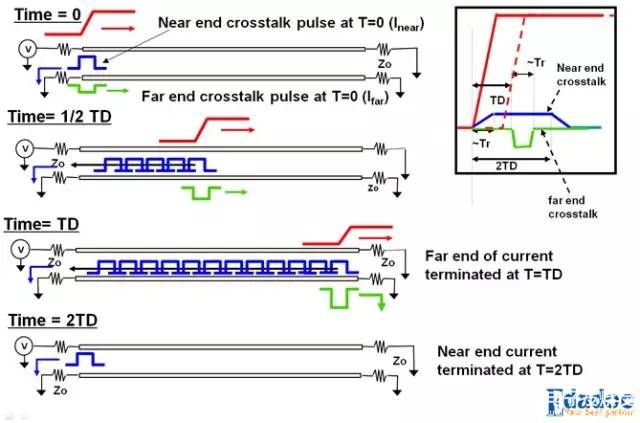

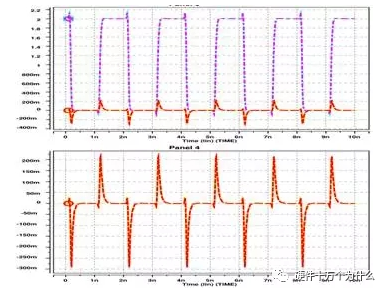

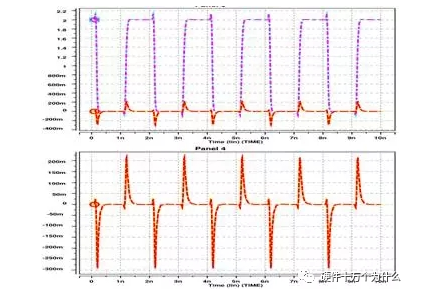

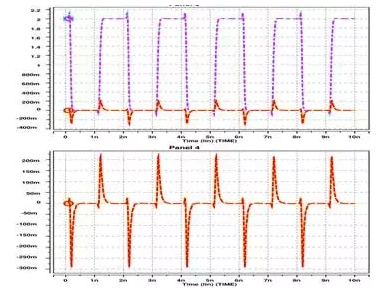

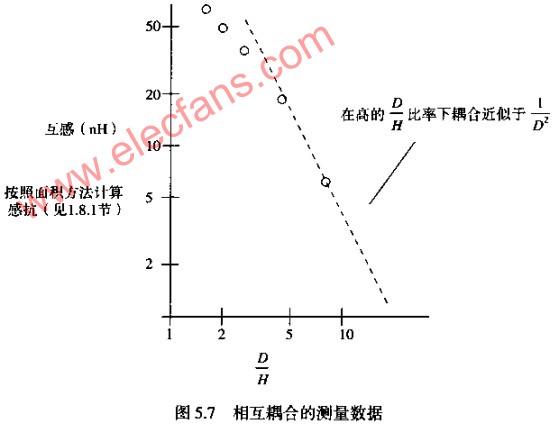

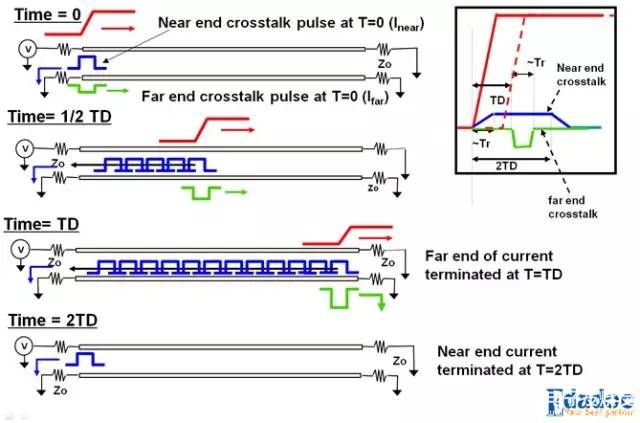

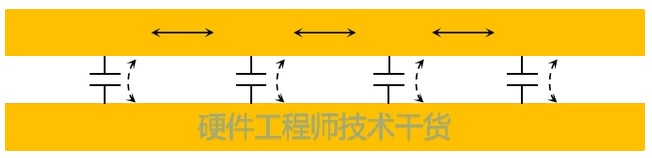

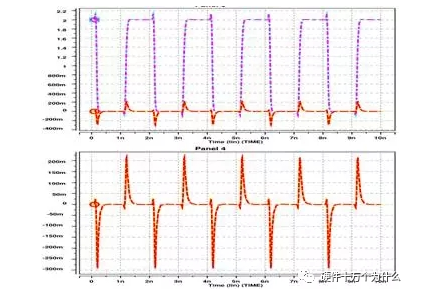

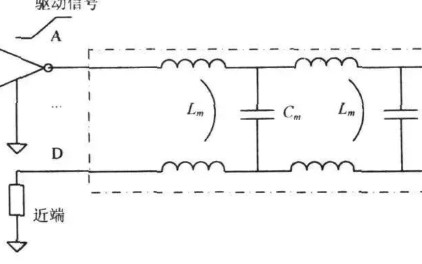

249 空间中耦合的电磁场可以提取为无数耦合电容和耦合电感的集合,其中由耦合电容产生的串扰信号在受害网络上可以分成前向串扰和反向串扰Sc,这个两个信号极性相同;由耦合电感产生的串扰信号也分成前向串扰和反向串扰SL,这两个信号极性相反。

2023-08-21 14:26:46 140

140 小的成本,快的时间使产品达到波形完整性、时序完整性、电源完整性的要求;我们知道:电源不稳定、电源的干扰、信号间的串扰、信号传输过程中的反射,这些都会让信号产生畸变,

2023-08-17 09:29:30 1263

1263

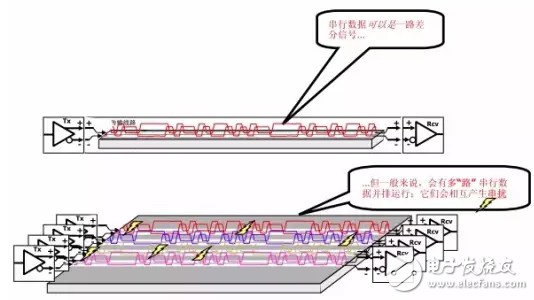

当信号通过电缆发送时,它们面临两个主要的通信影响因素:EMI和串扰。EMI和串扰严重影响信噪比。通过容易产生EMI 和串扰的电缆发送关键数据是有风险的。下面,让我们来看看这两个问题。

2023-07-06 10:07:03 592

592 串扰 :即两条信号线之间的耦合引起的线上噪声干扰。

2023-07-06 09:15:48 392

392

串扰是一种信号干扰现象,表现为一根信号线上有信号通过时,由于两个相邻导体之间所形成的互感和互容,导致在印制电路板上与之相邻线的信号线就会感应相关的信号,称之为串扰。

2023-07-03 15:45:10 595

595

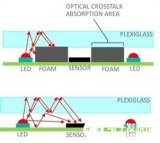

当 LED、传感器安装在玻璃后面时,这种光学串扰会变得更加严重。光学串扰会大大降低手势检测范围。 从 LED 到传感器可以有几条路径产生串扰。这些路径包括:直接路径、反射路径和玻璃盖片的光反射路径。直接路径和反射路径产生的串扰很容易缓解,在LED 和传感器之间放置一

2023-06-09 18:15:02 217

217

通常以断断续续或不易重现的方式发生,对于工程师来说, 尽早解决 PCB 上串扰发生的所有原因非常重要。 串扰会对时钟信号、周期和控制信号、数据传输线和 I/O 产生不良影响。通常来讲, 串扰是无法完全消除的,只能尽量减少串扰。 02 . 串扰的机制 1、耦合

2023-05-23 09:25:59 1079

1079

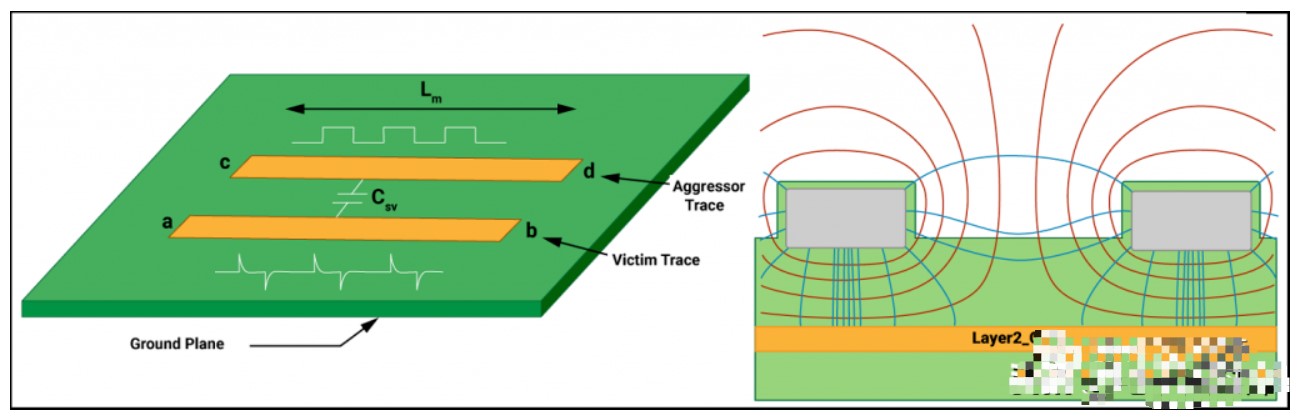

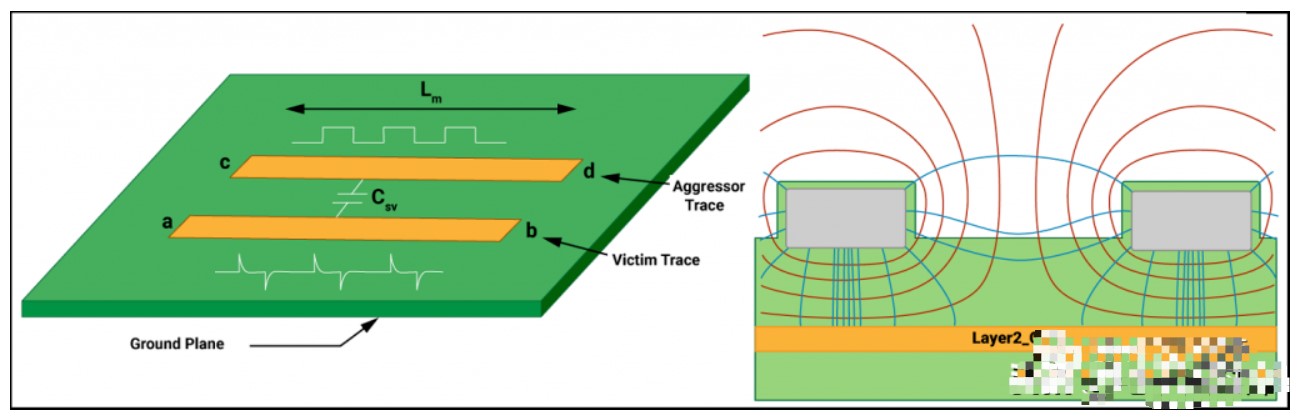

串扰是指有害信号从一个网络转移到相邻网络。任何一对网络之间都存在串扰。通常把噪声源所在网络称为动态网络或攻击网络。把受影响的网络称为静态网络或者受害网络。

2023-05-06 11:48:08 672

672

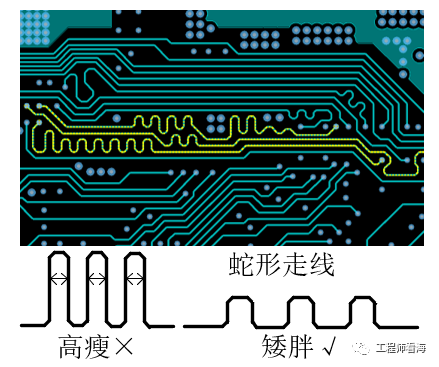

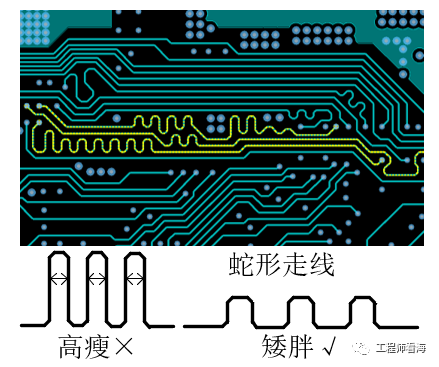

我们经常听说PCB走线间距大于等于3倍线宽时可以抑制70%的信号间干扰,这就是3W原则,信号线之间的干扰被称为串扰,串扰是怎么形成的呢?

2023-04-18 11:06:22 787

787

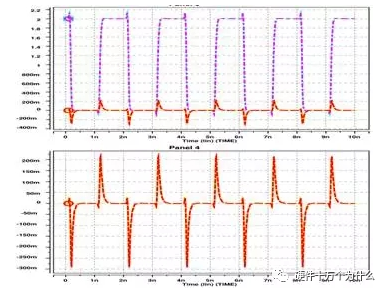

信号完整性仿真重点分析有关高速信号的3个主要问题:信号质量、串扰和时序。对于信号质量,目标是获取具有明确的边缘,且没有过度过冲和下冲的信号。

2023-04-03 10:40:07 553

553 高速电路信号完整性分析与设计—串扰串扰是由电磁耦合引起的,布线距离过近,导致彼此的电磁场相互影响串扰只发生在电磁场变换的情况下(信号的上升沿与下降沿)[此贴子已经被作者于2009-9-12 10:32:03编辑过]

2009-09-12 10:31:08

定义:信号完整性(Signal Integrity,简称SI)是指在信号线上的信号质量。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同 引起的。当电路中信号能以要求的时序、持续时间和电压幅度到达接收端时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。

2023-03-02 09:41:06 852

852

C语言中存在这样一种类型,名叫不完整类型(Incomplete types),虽然我们可能不太理解,或许也没有仔细研究过,但是在实际的编程中,我们却已经用到过很多次了。

2023-02-21 10:03:00 556

556 ____tz_zs 对于 ChatGPT 回答不完整的情况(篇幅限制,没有说完),可以输入“继续”指令,让其继续回答下去,获得完整内容。 如下图,发问 “使用web3js 调用 eth链智能合约” 直到这里才是获得了刚刚问题 “使用web3js 调用 eth链智能合约” 的完整回答。

2023-02-10 10:48:03 0

0 信号完整性分析的目的就是用最小的成本,最快的时间使产品达到波形完 整性、时序完整性、电源完整性的要求。

2023-02-03 11:25:55 464

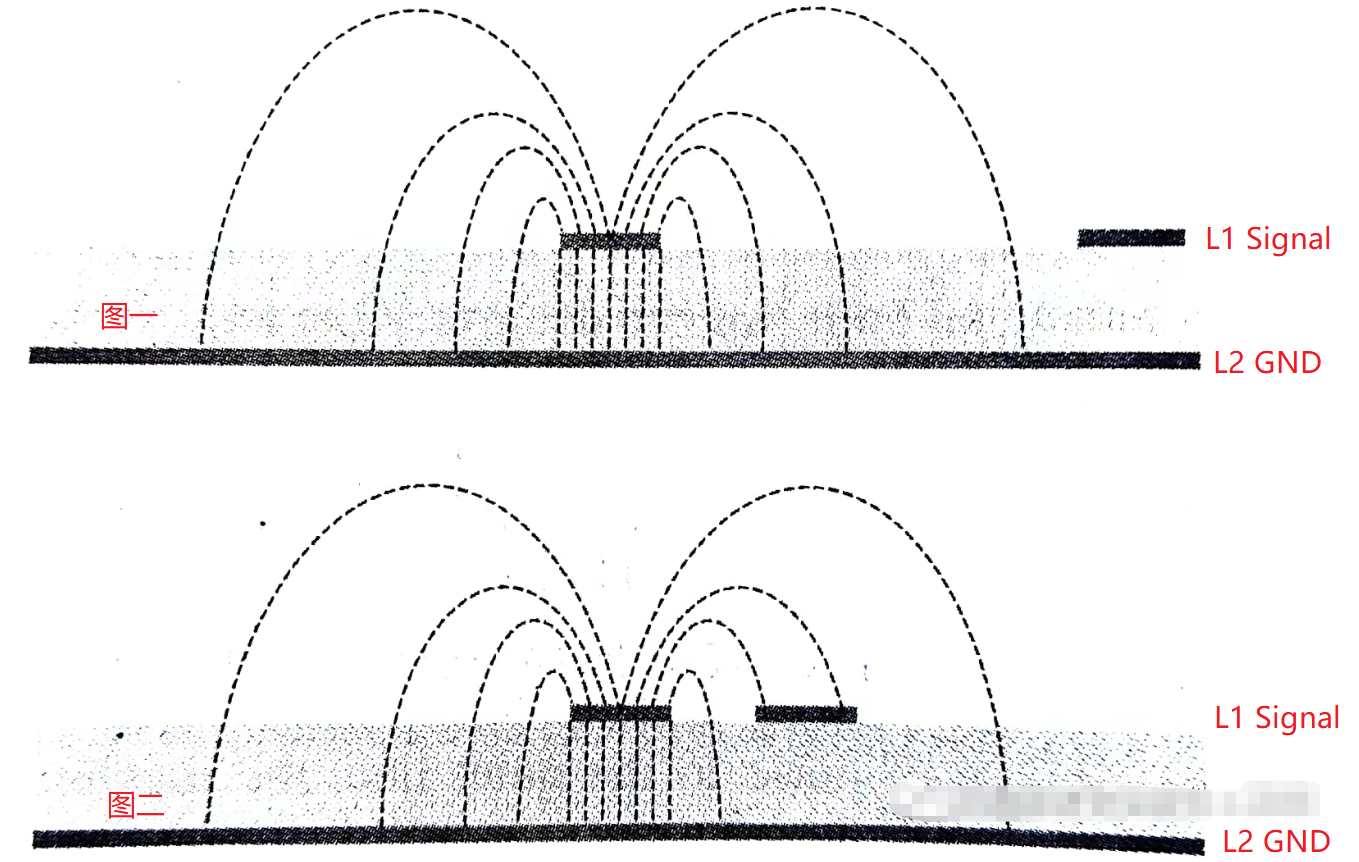

464 关于两个公式,我们不需要去记住,我们只需要知道它告诉了我们什么:攻击信号的幅值影响着串扰的大小;减小串扰的途径就是减小信号之间的耦合,增加信号与其回流平面之间的耦合。

2023-01-24 16:28:00 1494

1494

本章我们接着介绍信号完整性基础第三章节串扰剩余知识。

2023-01-16 09:58:36 1371

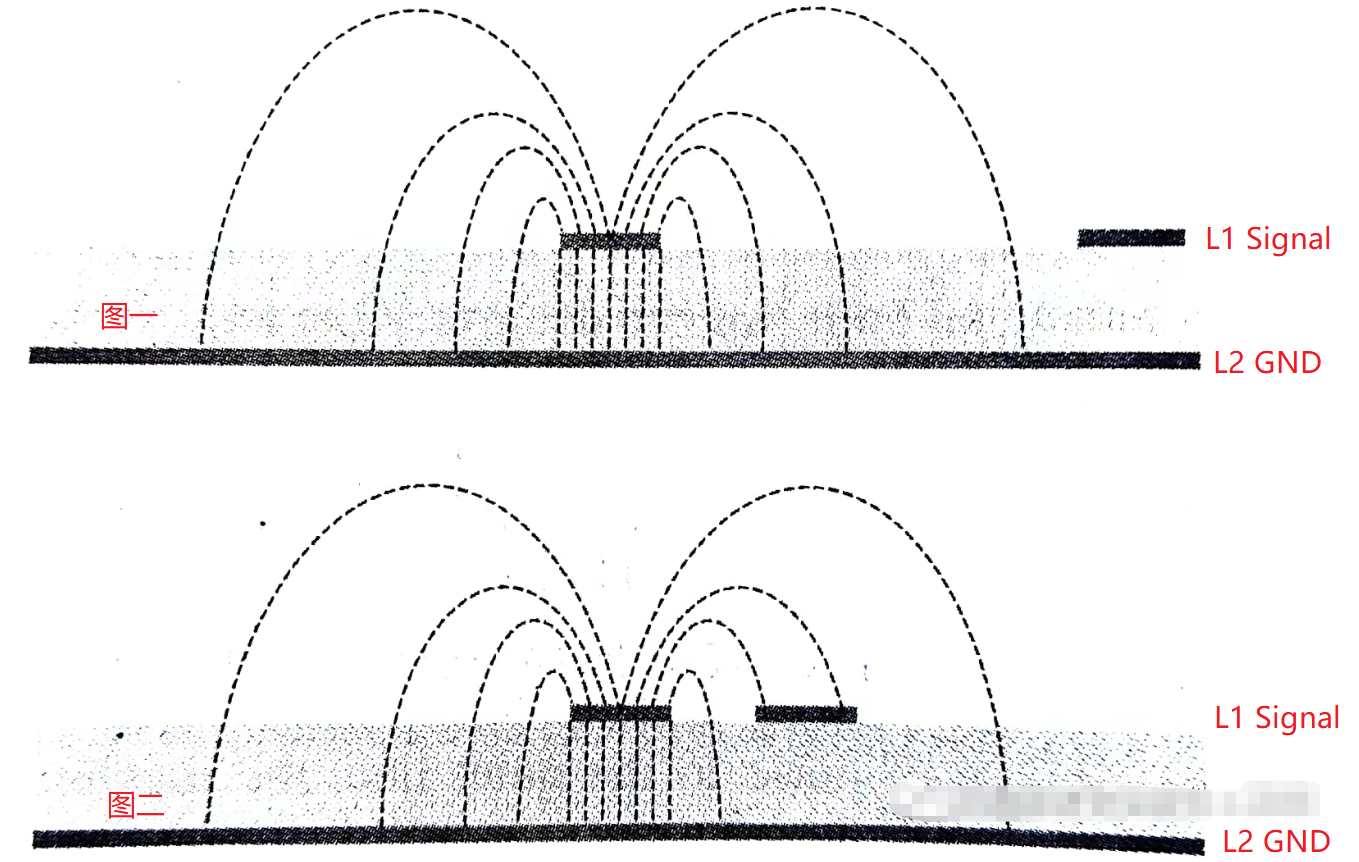

1371 当信号在一走线上传输时,一部分能量会通过电场容性耦合和磁场感性耦合到相邻走线上,从而引起串扰噪声,并以耦合后产生串扰噪声方向的不同区分为近端串扰(VNEXT)和远端串扰(VFEXT)。

2023-01-09 14:05:52 426

426 不完整类型(Incomplete types)是缺少足够信息来确定该类型对象大小的对象类型,不完整类型可以在翻译单元的某些点完整。

2022-12-16 09:52:07 272

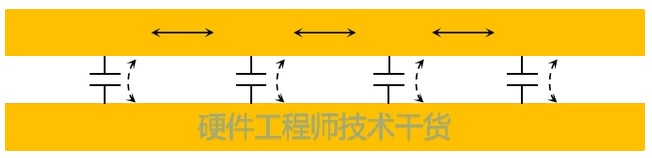

272 先来说一下什么是串扰,串扰就是PCB上两条走线,在互不接触的情况下,一方干扰另一方,或者相互干扰。主要表现是波形有异常杂波,影响信号完整性(Signal integrity, SI)等等。一般情况下可以分为容性串扰和感性串扰两种。

2022-11-10 17:00:44 1137

1137

APM32F091RCT6_SPI_从机接收数据不完整

2022-11-09 21:04:03 0

0 在实际的应用场景中,会遇到多种信号完整性问题,典型问题有如下几种:反射、串扰,电源/地噪,时序等。其中,发射和串扰是引起信号完整性问题的两大主要原因。

2022-10-09 10:56:55 2497

2497 通常说的信号完整性就是指信号无失真的进行传输。前面我们讨论很多信号完整性问题,包括时序、串扰、衰减、反射、电源完整性、EMC等等。

2022-09-29 17:00:06 880

880 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。串扰也可以理解为感应噪声。

2022-09-14 09:49:55 1684

1684

我们知道:电源不稳定、电源的干扰、信号间的串扰、信号传输过程中的反射,这些都会让信号产生畸变,看下面这张图,你就会知道理想的信号,经过:反射、串扰、抖动,最后变成什么鬼。

2022-08-24 11:22:17 499

499 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

2022-08-15 09:32:06 5670

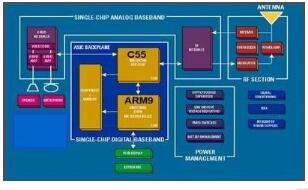

5670 信号完整性测量已成为开发数字系统过程中的关键步骤。信号完整性问题,如串扰、信号衰减、接地反弹等,在传输线效应也很关键的较高频率下会增加。

2022-07-25 09:59:58 6400

6400

串扰的危害:

降低板内信号完整性

时钟或者信号延迟

产生过冲电压和突变电流

造成芯片逻辑功能紊乱

2022-07-07 10:35:01 810

810 本文首先介绍了传输线理论,详细分析了高速PCB设计中的信号完整性问题,包括反射、串扰、同步开关噪声等,然后利用Mentor Graphics公司的EDA软件HyperLynx对给定电路模型进行了反射

2022-07-01 10:53:00 3

3 串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

2022-02-21 11:35:30 1779

1779

高速电路信号完整性分析与设计—串扰

2022-02-10 17:23:04 11

11 stm32串口DMA数据接收不完整问题说明最近做了一个项目需要用串口来接收模块端的应答数据,由于使用了实时操作系统,考虑中断嵌套或被打断的问题导致数据接收不完整的问题,使用串口dma接收数据,但

2021-12-24 19:37:57 17

17 介绍了高速PCB设计中的信号完整性概念以及破坏信号完整性的原因,从理论和计算的层面上分析了高速电路设计中反射和串扰的形成原因,并介绍了IBIS仿真。

2021-12-17 13:47:07 1

1 台积电公司CEO张忠谋近日表示:美国半导体供应链目前并不不完整,在美国建新厂的成本将比中国大陆高出37%至50%。目前台积电正在美国亚利桑那州厂建厂。

2021-10-28 10:37:15 1575

1575 说这段话时总会觉得很别扭,“我堂堂信号完整性怎么能是区区反射就能说明的呢?”之后随着理论与实践的深入,越来越觉得“反射中有黄金屋,反射中有颜如玉”,be the signal,弄清楚反射与串扰就拿到了解开信号完整性谜题的两

2021-04-13 09:46:29 2190

2190

文章——串扰溯源。 提到串扰,防不胜防,令人烦恼。不考虑串扰,仿真波形似乎一切正常,考虑了串扰,信号质量可能就让人不忍直视了,于是就出现了开头那惊悚的一幕。下面就来说说串扰是怎么产生的。 所谓串扰,是指有害信号从一

2021-03-29 10:26:08 2663

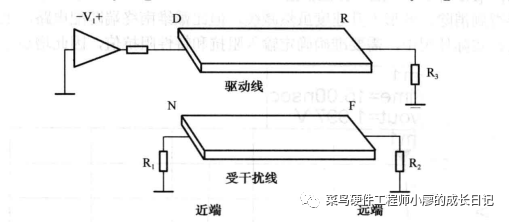

2663 静态网络靠近干扰源一端的串扰称为近端串扰(也称后向串扰),而远离干扰源一端的串扰称为远端串扰(或称前向串扰)。

2021-01-24 16:13:00 6444

6444

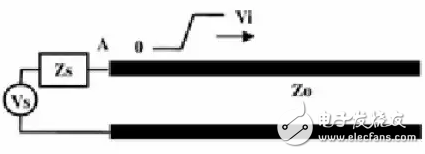

串扰是通过近电场(电容耦合)和磁场(电感耦合)在相邻导体之间耦合的噪声。尽管任何相邻导体都表现出串扰,但是当它出现在强干扰信号和敏感信号之间时,对信号完整性将造成很大的影响。 串扰的再定

2020-12-25 15:12:29 1968

1968 串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

2020-11-12 10:39:00 2

2 本文主要介绍串扰的概念,及其FEXT、NEXT等,以及串扰的消除措施。 串扰串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰。这种干扰是由于两条信号线间的耦合,即

2020-10-19 17:54:49 5160

5160

Altium中的信号完整性分析包括检查信号上升时间,下降时间,提供终端方案和进行串扰分析的能力。您还可以定义模型并设置规则和约束以及信号完整性分析相关的其它设置。一旦确认了串扰问题,就可以根据需要修改相同层或相邻层的布线路径。

2020-08-25 15:50:00 8673

8673

高速PCB设计中,信号之间由于电磁场的相互耦合而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可能引发电路误动作从而导致系统无法正常工作,解决PCB串扰问题可以从以下几个方面考虑。

2020-07-19 09:52:05 1991

1991 这个短暂的网络研讨会将指导您完成避免反射和串扰问题的方法在你的董事会设计pre-layout和布线后的设计阶段。

2019-10-23 07:04:00 2870

2870 串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

2019-09-18 15:10:37 13741

13741

信号完整性的问题主要包括传输线效应,如反射、时延、振铃、信号的过程与下冲以及信号之间的串扰等,涉及传输线上的信号质量及信号定时的准确性。

良好的信号质量是确保稳定时序的关键。由于反射和串扰造成

2019-06-24 15:27:25 1102

1102

出的AFT基本推导规则BRR的完备性.此外还对基于不完整AFT进行拓扑发现的NP难问题进行了讨论,深入剖析了任意实际的局域网络的不完整AFT通过BRR推导完成后的各种可能情况,并分析了单纯依靠AFT进行拓扑发现的局限性.该工作对于基于AFT进

2018-01-12 16:28:03 0

0 本文通过介绍信号完整性理论,对串扰和反射的成因进行探讨。利用Cadence公司的软件SpecctraQuest,以基于ARM11架构的S3C6410为主处理器嵌入式系统为载体进行信号完整性仿真分析

2017-12-01 17:16:01 963

963

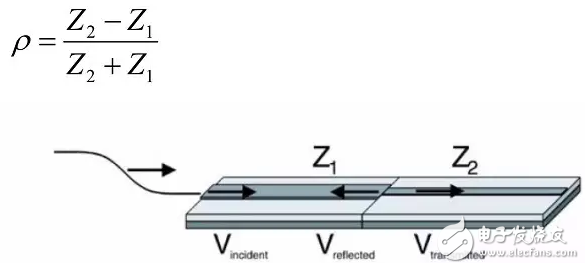

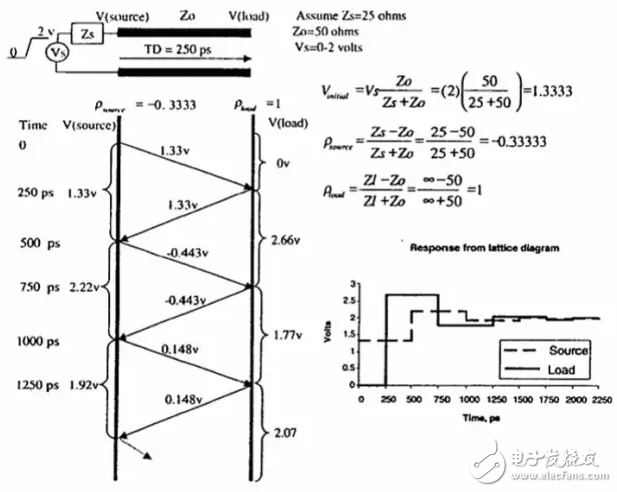

引起的。主要的信号完整性问题包括反射、振铃、地弹、串扰等。 源端与负载端阻抗不匹配会引起线上反射,负载将一部分电压反射回源端。如果负载阻抗小于源阻抗,反射电压为负,反之,如果负载阻抗大于源阻抗,反射电压为正。布线的几何形状、不正确的线端接、经过连接器的传输及电源平面

2017-11-16 13:24:51 36

36 介绍信号完整性的四个方面,EMI,串扰,反射,电源等。

2016-08-29 15:02:03 26

26 串扰是不同传输线之间的能量耦合。当不同结构的电磁场相互作用时,就会发生串扰。在数字设计中,串扰现象是非常普遍的。串扰可能出现在芯片、PCB板、连接器、芯片封装和连接器

2012-05-28 09:09:38 2368

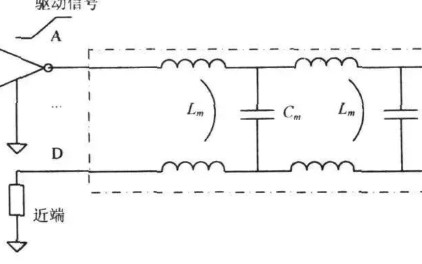

2368 通过端接电路在抑制攻击线上反射的同时,减小了受害线上信号的串扰,从而使信号在两条耦合线上的传输质量得到改善。最后进行了多组数据的串扰比较研究,分析了串扰减小的原因。

2011-12-12 14:31:21 28

28 文章介绍了数字电路设计中的信号完整性问题, 探讨了振铃、边沿畸变、反射、地弹、串扰和抖动等各种信号完整性问题的成因和抑制措施。针对常见的反射和串扰给出了较为详细的分

2011-09-07 16:14:58 104

104 串扰是 高速电路板 设计中干扰信号完整性的主要噪声之一;为有效地抑制串扰噪声,保证系统设计的功能正确,有必要分析串扰问题。针对实际PCB中互连线拓扑和串扰的特点,构

2011-06-22 15:58:54 31

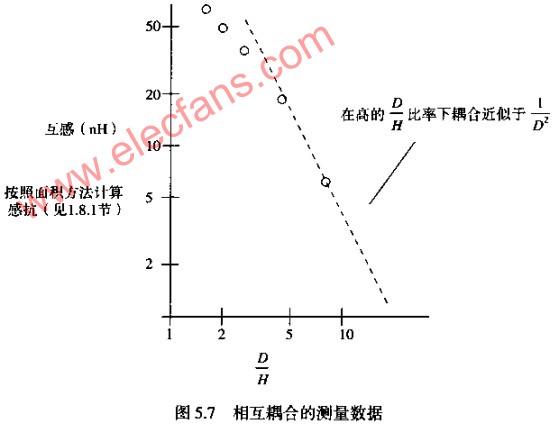

31 两个导体之间的串扰取决于它们之间的互感和互容。通常在数字设计中,感性串扰相当于或大于容性串扰,因此在这里开始我们主要讨论感性耦合的机制。

2010-06-10 16:22:46 1426

1426

高速电路信号完整性分析与设计—串扰串扰是由电磁耦合引起的,布线距离过近,导致彼此的电磁场相互影响串扰只发生在电磁场变换的情况下(信号的上升沿与下降沿)

2009-10-06 11:10:15 115

115

电子发烧友App

电子发烧友App

评论