数字频率计课程设计图

- 频率(58149)

- 数字频率计(35394)

相关推荐

[求助]数字频率计设计

我是一大三测控专业的学生,我们微电子实习需要设计一数字频率计,个人由于能力限制,许多方面都还不是很明白,希望能得到

2008-12-12 19:01:39

基于单片机的数字频率计设计

文末下载完整资料1.1数字频率计概述 数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。它是一种用十进制数字显示被测信号频率的数字测量仪器。它的基本功能是测量正弦信号

2021-11-04 12:51:04 31

31

31

31基于51单片机的数字频率计的设计讲解

基于51单片机的数字频率计的设计讲解(单片机原理及应用)-该文档为基于51单片机的数字频率计的设计讲解资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-22 10:54:43 85

85

85

85如何进行简易数字频率计的设计分析

文章简单阐述了数字频率计在设计之前的理论分析,给出了数字频率计误差分析、灵敏度涵义、触发信号误差、信号时间间隔的测量等问题的理论分析,为数字频率计的设计打下了一定的基础。

2019-05-27 08:00:00 7

7

7

7基于FPGA自适应数字频率计的设计

为频率的测量。目前,市场上有各种多功能、高精度、高频率的数字频率计,但价格不菲。为适应实际工作的需要,本文在简述频率测量的基本原理和方法的基础上,提供一种基于FPGA的数字频率计的设计和实现过程,本方案不但切实可行,而且具有成本低廉、小巧轻便、便于携带等特点。

2019-01-01 16:00:00 6008

6008

6008

6008

数字频率计

数字频率计,数字电路课程的课程设计,

1) 频率测量范围:1HZ-10KHZ,10KHZ-100KHZ。

2)测量时间:T≤1.5S。

3)被测信号幅度:0.5V。

4) 具有四位十进制数字显示功能。

2016-05-13 11:28:05 47

47

47

47大学数字频率计课程设计报告

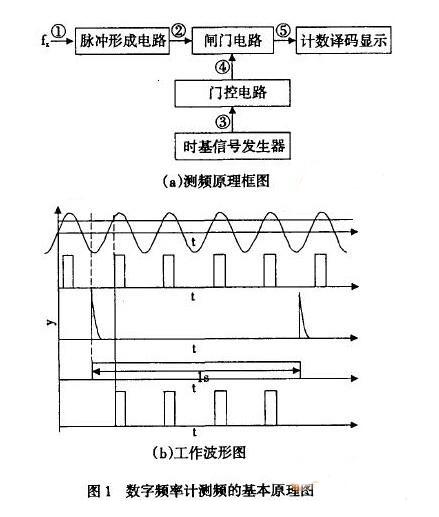

数字频率计是一种专门对被测信号频率进行测量的电子测量仪器。其最基本的工作原理为:当被测信号在特定时间段T内的周期个数为N时,则被测信号的频率f=N/T。

2016-03-01 17:29:08 63

63

63

63基于verilog语言的数字频率计设计

基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计基于verilog语言的数字频率计设计

2015-12-08 15:57:23 74

74

74

74数字频率计的制作

数字频率计是采用数字电路制做成的能实现对周期性变化信号频率测量的仪器。频率计主要用于测量正弦波、矩形波、三角波和尖脉冲等周期信号的频率值。其扩展功能可以测量信号的周期和脉冲宽度。通常说的,数字频率计是指电子计数式频率计。

2015-11-20 14:55:57 142

142

142

142基于DSP2812设计的简易数字频率计

我们设计的简易数字频率计在未采用任何门控器件控制的情况下,在很宽的范围内实现了等精度频率测量,0.5Hz~10MHz的范围内测量方波的最大相对误差小于2e-6,测量正弦波的最大相对误

2011-10-09 11:46:55 4613

4613

4613

4613

基于NiosII的等精度数字频率计的设计

NiosII 处理器是一个具有很大灵活性的32 软核处理器,比较容易在片上实现SOPC。本文主要提供了一种基于NiosII 软核处理器的等精度数字频率计的设计的实现方法。

2011-09-27 14:51:25 66

66

66

66设计简易数字频率计

频率测量用途非常广泛,高精度、宽量程的数字频率计因而成为重要的测量仪器。简易 数字频率计 采用多周期测量原理,即用标准频率信号填充整数个周期的被测信号,从而消除了被

2011-06-28 17:31:42 1194

1194

1194

1194数字频率计

数字频率计是一种基础测量仪器,到目前为止已有30多年的发展史。早期,设计师们追求的目标主要是扩展测量范围,再加上提高测量精度、稳定度等,这些也是人们衡量数字频率计的

2011-04-07 13:40:59 922

922

922

92212位十进制等精度数字频率计

分析了数字式频率计,利用VHDL设计一种量程可自动转换的12位十进制等精度数字频率计,具有自动校验和测量功能,能用标准时钟校验测量精度,并具有超量程报警功能,超出当前

2010-12-16 11:23:34 98

98

98

98超高频数字频率计的设计

摘要:介绍了以通用频率计数器ICM7216D为核心,结合大规模集成电路和简单的外围电路,采用分频法进行测量范围为10kHz~700MHz的超高频数字频率计的设计方法,并给出了该频率计的

2010-05-25 09:03:31 100

100

100

100八位150MHz数字频率计的制作

八位150MHz数字频率计的制作

在制作高频电路时,会经常碰到频率测量的问题,实际上频率计(frequency counter)是一种比较容易自制的电子设备。以下将要制作的频率计,其

2010-05-14 10:21:20 6257

6257

6257

6257

基于FPGA/CPLD芯片的数字频率计设计

基于FPGA/CPLD芯片的数字频率计设计摘要:详细论述了利用VHDL硬件描述语言设计,并在EDA(电子设计自动化)工具的帮助下,用大规模可编程逻辑器件(FPGA/CPLD)实现

2010-04-30 14:45:13 132

132

132

132基于单片机的数字频率计的方案

基于单片机的数字频率计的方案

概述:设计一种以单片机AT89C51为核心的数字频率计,介绍了单片机、数字译码和显示单元的组成及工作原理。测量

2010-03-24 10:02:01 6181

6181

6181

6181

基于高速串行BCD码除法的数字频率计的设计

摘要: 介绍了在PPGA芯片上实现数字频率计的原理。对各种硬件除法进行了比较,提出了高速串行BCD码除法的硬件算法,并将其应用在频率计设计中。

2009-06-20 14:48:14 1147

1147

1147

1147

基于FPGA的数字频率计的设计与实现

介绍了一种运用FPGA开发软件Quartus II设计的数字频率计。该数字频率计的1 Hz~1 MHz输入被测脉冲信号具有频率测量、周期测量、脉宽测量和占空比测量等多种用途,其测试结果由3 只

2009-03-17 10:31:31 184

184

184

184量程自动控制的数字频率计

量程自动控制的数字频率计一、 实验目的:1、数字系统的设计与调试2、TTL 数字集成电路的使用3、量程自动控制的逻辑设计二、实验要求:设计

2009-03-06 19:56:01 2310

2310

2310

2310

数字频率计测频率的基本原理

了解数字频率计测频率与测周期的基本原理;熟练掌握数字频率计的设计与调试方法及减小测量误差的方法。[重点与难点]重点:数字频率计的组成框图和波形图。难点:

2008-12-01 14:36:48 505

505

505

505基于单片机和CPLD的数字频率计的设计

基于单片机和CPLD的数字频率计的设计

在传统的控制系统中,通常将单片机作为控制核心并辅以相应的元器件构成一个整体。但这种方法硬件连线复

2008-10-15 08:59:51 992

992

992

992 电子发烧友App

电子发烧友App

评论